Opanuj jitter: pętle PLL nowej generacji

Użytkownicy współczesnych sieci telekomunikacyjnych bardzo dużej przepustowości: transmisja strumieniowa, filmy i YouTube, gry sieciowe i inne popularne aplikacje spowodowały znaczny wzrost ilości danych przesyłanych przez Internet. Prowadzi to do wzrostu zapotrzebowania na coraz szybsze urządzenia sieciowe: przełączniki, routery itp., które muszą radzić sobie z sygnałami o coraz większych częstotliwościach, aby obsłużyć większą szybkość transmisji.

W artykule omawiamy zjawisko jittera i przedstawiamy nowe sposoby, które pozwalają całkowicie usunąć lub zminimalizować wpływ jittera na działanie szybkich systemów cyfrowych.

Ten trend nie ogranicza się jedynie do rynku telekomunikacji. Przyspieszenie przetwarzania informacji następuje również w klastrach obliczeniowych, w przemyśle, w sektorze militarnym i lotniczym, a także w motoryzacji. Wszędzie tam wymagana jest szybsza transmisja i przetwarzanie większej ilości danych.

Dla projektanta systemu pracującego w tych sektorach kluczowym problemem jest integralność sygnałowa. Wiąże się ona z implementacją systemów zegarowych wysokiej szybkości. Często okazuje się, że nieskuteczny układ zegarowy stanowi przyczynę problemów z integralnością sygnałową – na przykład wysokiej stopy błędów w systemach telekomunikacji.

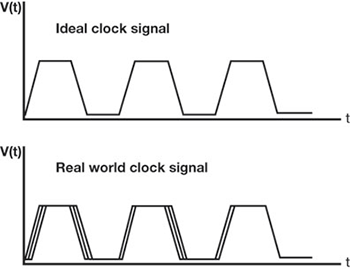

Jitter to odstępstwo chwil czasowych prawdziwego sygnału od stanu idealnego. Jest on jedną z najczęstszych przyczyn problemów w układach zegarowych, jak pokazano na rysunku 1, techniczna definicja ustalona przez amerykański National Institue of Standards and Technology mówi o „krótkookresowym odchyleniu fazy istotnych chwil sygnału cyfrowego od ich idealnych pozycji w czasie”. Matematycznie można to opisać wzorem:

Φ = tn – Tn

gdzie:

- Φ to jitter

- tn to istotna chwila czasowa sygnału

- Tn idealna pozycja tego sygnału w czasie

Rys. 1. Jitter oznacza wszelkie niedokładności i niespójności w czasie lub fazie sygnału

Jeden problem, wiele objawów

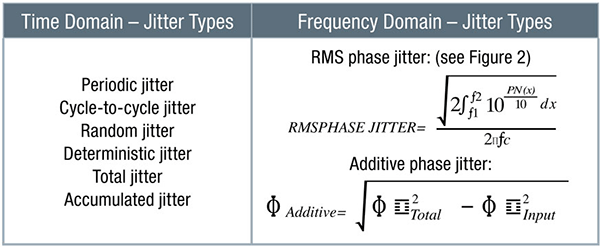

Jitter to popularne określenie, ale w rzeczywistości może oznaczać wiele różnego rodzaju problemów związanych z zegarem w obwodach elektronicznych. Zjawiska opisywane słowem „jitter” można zaobserwować zarówno w domenie czasu, jak i częstotliwości. W każdym z przypadków występuje wiele rodzajów problemów czasowych, które można określić jako jitter.

Tab. 1

Integralność sygnałowa systemu pogorszy się w większym lub mniejszym stopniu pod wpływem jittera w zależności od skali zjawiska i szybkości pracy systemu. W zastosowaniach o wysokiej przepustowości projektanci najczęściej muszą skutecznie zmniejszyć jitter. Aby to uczynić, należy wiedzieć jak on powstaje.

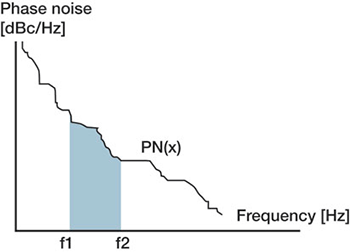

Rys. 2. Szum fazowy jest funkcją częstotliwości

Istnieje wiele potencjalnych źródeł jittera, zatem określenie tych najbardziej istotnych nie zawsze jest łatwe. Najbardziej typowe źródła to:

- Zasilacz – tętnienia prądu, pojemności pasożytnicze i interferencje magnetyczne spowodowane przełączaniem mogą zakłócić pracę układu zegara.

- Rezonatory kryształowe – pewien poziom jittera wynika z natury układu i nie da się go uniknąć. Poziom ten może wzrosnąć z upływem czasu oraz ze wzrostem temperatury.

- Przesłuch między ścieżkami na płytce PCB może wpłynąć na czasy przełączeń sygnału.

- Inne elementy na płytce – układy magnetyczne są szczególnie niebezpiecznym źródłem interferencji, które mogą powodować jitter.

Na szczęście istnieje wiele metod zmniejszenia skali jittera powodowanego przez każde z tych źródeł. Pierwsza z metod tak czy inaczej powinna być celem projektantów: poprawny schemat płytki. Jest to rozsądny punkt wyjścia, ponieważ ten sposób zmniejszenia jittera nie zwiększa kosztu materiałów. Praktyki, które mogą zmniejszyć jitter, to między innymi:

- Kontrola położenia i terminacji długich ścieżek. Na wysokich częstotliwościach pojedyncza ścieżka PCB zachowuje się jak linia transmisyjna w systemie komunikacyjnym, zatem może wprowadzać przesłuchy i tłumić sygnał. Projektant płytki powinien zadbać o dopasowanie impedancji na końcu każdej ścieżki i poprowadzić każdą ścieżkę sygnału prawidłowo, aby zmniejszyć przesłuchy, na przykład stosując konfigurację typu skrętka.

- Odpowiednie ułożenie warstw płytki PCB. Sygnały o małych amplitudach powinny biec przez środkowe warstwy. Górna i dolna warstwa powinny stanowić zasilanie i masę.

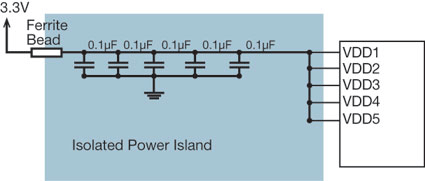

- Izolacja zasilania jak na rysunku 3. Ryzyko zaburzenia linii zegara przez zasilacz można oszacować na podstawie parametru PSRR (Power Supply Rejection Ratio). Izolowany obszar (wyspa) miedzi separuje zakłócający zasilacz od głównej warstwy zasilania za pomocą równolegle połączonych kondensatorów i koralika ferrytowego.

Rys. 3. Wyspa zasilania izoluje resztę obwodu od zakłóceń generowanych przez warstwy zasilania

Powyższe sposoby modyfikacji schematu mają jednak ograniczony wpływ na jitter. W szczególności wymagania mechaniczne lub elektryczne często nie pozwalają projektantowi na realizację schematu optymalnego pod względem interferencji. Na przykład sprzedawcy produktów przykładają większą wagę do zmniejszenia rozmiaru niż do zmniejszenia szumów. Możliwe też, że konfiguracja wejść i wyjść podłączonych do głównego procesora dyktuje sposób prowadzenia najważniejszych ścieżek.

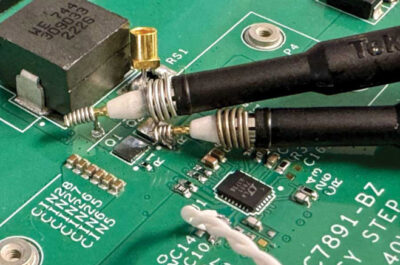

Projekty inteligentnych sterowników przetwornic buck z tranzystorami GaN — część 1: Zagadnienia i pomiary

Projekty inteligentnych sterowników przetwornic buck z tranzystorami GaN — część 1: Zagadnienia i pomiary  Prof. Ryszard Tadeusiewicz: Sztuczna inteligencja wykorzystująca seks w komputerze

Prof. Ryszard Tadeusiewicz: Sztuczna inteligencja wykorzystująca seks w komputerze  Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)