Grzegorz Kamiński wyjaśnia, do czego służy technologiczna platforma Treo firmy onsemi

W listopadzie br. Mikrokontroler.pl opublikował informację prasową dotyczącą platformy Treo firmy onsemi. Można było tam wyczytać, że jest to najbardziej zaawansowana w branży platforma dla sygnałów analogowych i mieszanych. Jednak – jak to w informacji prasowej – niewiele to wyjaśniło, a ponieważ w ostatnich tygodniach pojawiły się informacje o klientach, którzy Treo zastosowali, postanowiłem wyjaśnić, czym właściwie jest to narzędzie.

onsemi jako foundry dla ASIC

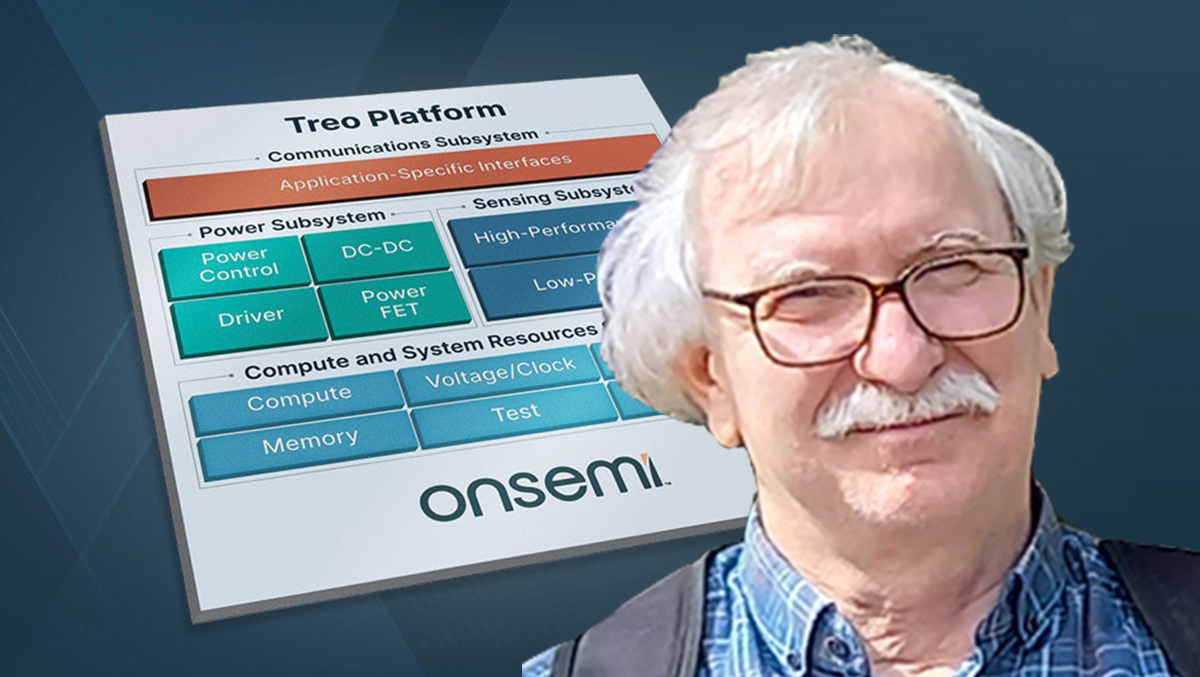

Treo jest platformą technologiczną, która wraz z platformą projektowania układów scalonych analogowo-cyfrowych, używana jest wewnętrznie przez firmę onsemi. Wprowadzenie jej na rynek miało na celu uświadomienie klientów, że mogą użyć platformy do zaprojektowania swoich układów scalonych np. typu ASIC. W takim przypadku onsemi działałoby jako klasyczne foundry, producent ASIC-a.

Wraz ze wzrostem zapotrzebowania na energię, w takich branżach jak motoryzacja, przemysł i centra danych AI, inżynierowie stają przed podwójnym wyzwaniem: zapewnienia wyższej wydajności przy jednoczesnym spełnieniu surowszych norm środowiskowych i oczekiwań dotyczących sprawności systemów zasilania. Ponadto, w przypadku mniejszych, energooszczędnych urządzeń, takich jak np. medyczne urządzenia noszone, zapotrzebowanie rynku dynamicznie rośnie, wymagając dodatkowej inteligencji, funkcjonalności i łączności pomiędzy światem czujników z zasady działających analogowo, a światem cyfrowym.

Dlatego właśnie firma onsemi, jako wieloletni producent podzespołów półprzewodnikowych mocy i do systemów zasilania oraz układów scalonych analogowych, opracowała nową platformę analogowo-cyfrową Treo. Zaprojektowała ją z myślą o zapewnieniu niezbędnej wydajności, integracji i efektywności. Dzięki zastosowaniu technologii Bipolar-CMOS-DMOS (BCD) w rozmiarze charakterystycznym 65 nm i możliwości obsługi zakresu napięć 1–90 V, platforma Treo rozszerzy ofertę onsemi w zakresie inteligentnych technologii zasilania i połączenia szeregu czujników ze światem cyfrowym, przez dostarczenie nowej generacji układów scalonych do zarządzania energią, interfejsów czujników, specjalnie zaprojektowanych urządzeń komunikacyjnych i niezawodnych produktów standardowych.

Analogowo-cyfrowa platforma Treo

Platforma Treo oparta jest na technologii BCD, która integruje najlepsze cechy trzech typów tranzystorów na jednym chipie:

- Tranzystor bipolarny dla funkcji analogowych;

- Tranzystory MOSFET CMOS (Complementary Metal-Oxide Semiconductor) dla przetwarzania cyfrowego;

- Tranzystory DMOS (Double-diffused Metal-Oxide Semiconductor) dla elementów mocy i wysokiego napięcia.

Pierwsze dwa to oczywistość, dlatego napiszę kilka słów o tych ostatnich, tranzystorach DMOS.

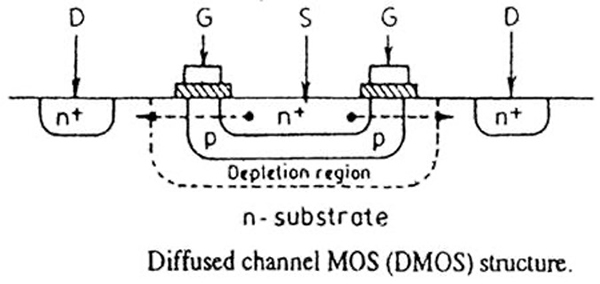

Poniższy rysunek przedstawia strukturę MOS z podwójną dyfuzją, tranzystor DMOS. Długość kanału [L], jest kontrolowana przez głębokość złącza wytworzoną przez dyfuzje typu n+ i p pod tlenkiem bramki. L jest również odległością boczną między złączem n+ p, a złączem podłoża p-n. Długość kanału można zmniejszyć do około 0,5 mikrometra. Zatem proces ten jest podobny do wytwarzania w tranzystorze bipolarnym obszaru bazy dla tranzystora bipolarnego z podwójnym dyfuzją. Gdy do bramki zostanie przyłożone dość duże napięcie dodatnie [>VTH], spowoduje to inwersję obszaru podłoża p pod bramką do typu n, a wytworzona przy powierzchni warstwa inwersyjna typu n będzie działać jako kanał przewodzący dla przepływu elektronów od źródła do drenu.

Konstrukcja tranzystora DMOS ( Double-diffused Metal-Oxide Semiconductor)

Ze struktury wynika, że podłoże typu n jest bardzo słabo domieszkowane ( obszar n-substrate). Pomoże to w zapewnieniu wystarczającej ilości objętości chipu na rozszerzenie obszaru zubożonego między obszarem dyfuzji typu p, a obszarem styku drenu n+. W rezultacie napięcie przebicia między drenem a źródłem będzie wyższe [BVDS].

Spójna podstawa dla różnych aplikacji

Platforma została zaprojektowana tak, aby zapewnić niezawodną i spójną podstawę dla różnych aplikacji, dzięki wykorzystaniu wstępnie opracowanych modułów projektowania analogowego, cyfrowego i zasilania lub bloków IP. Te bloki IP można łączyć, aby opracowywać nowe produkty i uprościć proces projektowania dla inżynierów onsemi, i nie tylko, umożliwiając szybszy rozwój produktów. Platforma Treo integruje złożone przetwarzanie sygnałów analogowych i cyfrowych, mikrokontrolery (MCU) i wiele innych funkcji dostępnych w technlogii CMOS, umożliwiając działanie bloków IP na niskich, średnich i wysokich poziomach napięcia. Jej wyjątkowe właściwości termiczne, charakteryzujące się sprawdzonym limitem temperatury pracy 175°C, a niektóre modele wytrzymują nawet do 200°C, umożliwiają zastosowanie tej technologii w układach motoryzacyjnych czy militarnych. To konkurencyjne rozwiązanie, o temperaturze pracy co najmniej 25°C większej względem produktów konkurencji, umożliwia lepsze odprowadzanie ciepła bezpośrednio z chipu.

Na platformie opracowano już wiele produktów, w tym translatory napięcia, stabilizatory LDO i sterowniki wielofazowe. Niektóre z nich zostały opracowane z myślą o rynku masowym, a inne są dedykowane dla konkretnych klientów. Jest już także dostępny kontroler Ethernet 10BASE-T1S, a w opracowaniu są przetwornice DC-DC, kontrolery wielofazowe do systemów komputerowych, sterowniki LED do systemów motoryzacyjnych, układy scalone zabezpieczeń w systemach elektrycznych oraz sterowniki bramek dla wielu rodzajów tranzystorów.

Produkty z platformy Treo na płytkach krzemowych 300 mm onsemi

Produkty opracowane na platformie Treo wytwarzane są w zakładzie onsemi na 300 mm płytkach krzemowych, zlokalizowanym w USA w East Fishkill w stanie Nowy Jork. Ten nowoczesny zakład, który może wytwarzać elementy w technologii 65 nm, posiada certyfikaty motoryzacyjne i ITAR ( ITAR – umożliwia opracowania dla rządu i armii USA).

Wiele szczegółów na temat technologii BCD65 i platformy Treo można znaleźć w dokumencie “High Performance, Precision Analog Capability Enabled by the Treo Platform”.

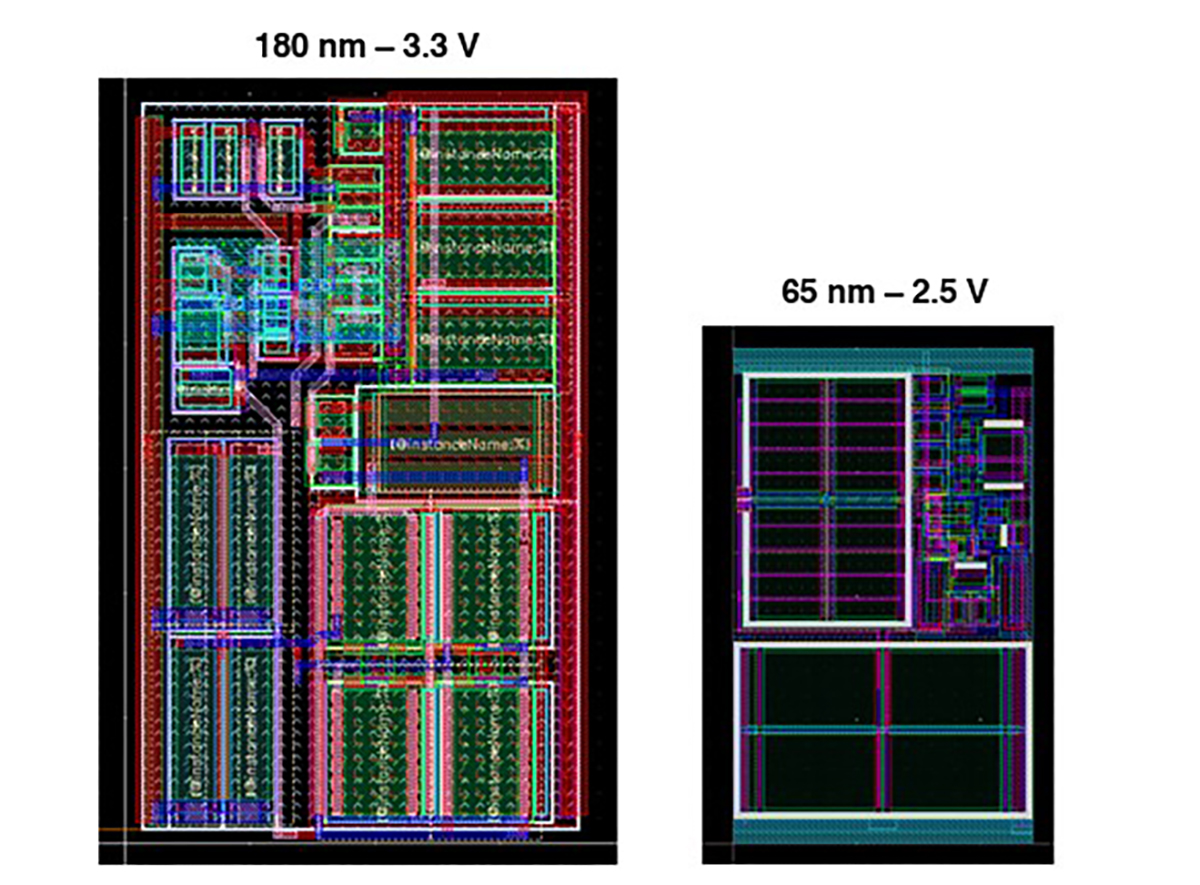

Na rysunku poniżej widzimy zmniejszenie o 45% powierzchni chipu przy zmianie technologii z 180 nm – 3,3 V do BCD65 – 2,5 V dla układu komparatora.

Porównanie powierzchni komparatora dla technologii 180nm -3,3V zasilania i technologii BCD65 ( po prawej) 65nm – 2,5V napięcie zasilania

Zalety technologii BCD65 firmy onsemi

Dla analogowych i mieszanych (analogowo-cyfrowych) sygnałów zmniejszenie napięcia zasilania przy podobnej dokładności nie tylko zapewnia poprawę kosztów układu, ale także pozwala na integrację wielu innych funkcji w mniejszej obudowie montażowej. Te współczynniki zmniejszania analogowych i mieszanych, analogowo-cyfrowych sygnałów są możliwe dzięki temu, że:

- W procesach półprzewodnikowych mniejszy węzeł procesu generalnie skutkuje lepszym dopasowaniem napięcia progowego tranzystora (Vth). Współczynnik niedopasowania, który jest parametrem zależnym od procesu, jest wtedy niższy. Zgodnie z prawem Pelgroma, obszar bramki dopasowanych tranzystorów zmniejsza się przy tym samym poziomie niedopasowania. Porównanie współczynników niedopasowania napięcia progowego między procesem 180 nm – 5 V i 65 nm BCD – 2,5 V, pokazuje skalowanie obszaru bramki w dopasowanych strukturach tranzystorowych i poprawę tego współczynnika co najmniej dwa razy. Ograniczoną poprawę widać pomiędzy 180 nm – 3,3 V i 65 nm – 2,5 V.

Prawo Pelgroma, znane również jako model Pelgroma, głosi, że statystyczna rozbieżność między dwoma identycznie narysowanymi tranzystorami (tak, tranzystory się rysuje, a tak naprawdę maski – szczególnie dotyczy to projektowania układów scalonych analogowych i podzespołów dyskretnych) jest odwrotnie proporcjonalna do pierwiastka kwadratowego z powierzchni bramki. Oznacza to, że wraz ze wzrostem rozmiaru tranzystora, zmienność jego charakterystyk, takich jak napięcie progowe, maleje. Jest to fundamentalna zasada stosowana w projektowaniu analogowych i mieszanych układów scalonych, aby uwzględnić zmienność procesu.

Marcel J.M. Pelgrom, inżynier z NXP, jest także autorem fundamentalnych podręczników do projektowania analogowo-cyfrowych konwerterów, a jego model został powszechnie zaakceptowany jako elegancki opis niedopasowania. Z tego powodu Marcel J.M. Pelgrom znany jest także z przydomka Mr. Mismatch.

To o czym mowa w powyższym punkcie to fakt że odchylenie standardowe niedopasowania σ(Vth) parametrów tranzystora, takich jak napięcie progowe Vth, jest proporcjonalne do AVTH / √A, gdzie A = W*L to powierzchnia bramki tranzystora, gdy AVTH to współczynnik Pelgroma. Ten współczynnik jest wyznaczany empirycznie i dlatego w tym przypadku tak jest. Generalnie dla technologii >=180nm zmniejszenie wymiarów krytycznych poprawia współczynnik Pelgroma. Dla technologii 130-65 nm musimy stwierdzić że “to zależy”, a dla technologii poniżej 65 nm współczynnik ten ulega pogorszeniu. A więc nie zawsze mniejsze jest lepsze.

I jeszcze jeden przykład np. dla projektu komparatora: Prawo to pomaga projektantom wybierać rozmiary tranzystorów, aby zachować wydajność i dokładność w obliczu odchyleń produkcyjnych. W lustrze prądowym projektanci mogą zwiększyć szerokość W i długość kanału L tranzystorów, aby zmniejszyć niedopasowanie i poprawić dokładność, mimo, że zwiększa to powierzchnię struktury i pojemność obciążenia. A więc nie zawsze mniejsze jest lepsze (po raz drugi).

- Standardowy rezystor polimerowy BCD65 wykazuje niższy współczynnik niedopasowania, w porównaniu zarówno ze standardowym rezystorem polimerowym, jak i rezystorem polimerowym o wysokiej rezystancji technologii BCD 180 nm firmy onsemi. Oprócz mniejszego odstępu między elementami, powierzchnia bloków rezystorów jest o ponad 40% mniejsza.

- Kondensatory Poly-N (well) mają mniejszą powierzchnię przy tej samej wartości bezwzględnej, w porównaniu z technologią BCD 180 nm. Pojemność tlenku bramki na jednostkę powierzchni, która jest odwrotnie proporcjonalna do grubości tlenku, jest o 30% wyższa w BCD65.

- Oprócz mniejszej powierzchni obszaru polikrzemu, gęstość upakowania podzespołów dodatkowo wzrasta, ponieważ zasady projektowania BCD65 pozwalają na mniejsze odstępy między tranzystorami. Wszystkie elementy tranzystora, obszary źródła, drenu i bramki zajmują mniej powierzchni, a kontakty są prawie 6 razy mniejsze.

- Tranzystory bipolarne są mniejsze i wykazują doskonałe dopasowanie.

- BCD65 zapewnia dużą skalowalność połączeń między podzespołami układu scalonego. Zasady projektowania pozwalają na mniejszą minimalną szerokość ścieżek metalizacji i mniejsze odstępy między nimi wraz z (prawie 7-krotnie) mniejszymi połączeniami pomiędzy poszczególnymi poziomami metalizacji. Nie musi to jednak powodować większej impedancji połączeń: wiele warstw metalizacji BCD65 wykorzystuje na połączenia tzw. miedź damasceńską o 35% mniejszej rezystancji w porównaniu z aluminium. Ze względu na mniejsze rozmiary chipu długości ścieżek metalizacji są zazwyczaj krótsze.

Miedź damasceńska albo lepiej proces damasceński

Ciągły wzrost szybkości i rozmiarów układów scalonych doprowadził do przejścia od tradycyjnej metalizacji aluminium i izolacji międzywarstwowej SiO₂ do metalizacji miedzią i izolatorów o niższej stałej dielektrycznej (zwanych izolatorami „low-k”). Miedź zapewnia niższą rezystywność połączeń łączących poszczególne tranzystory. Izolatory o niższej stałej dielektrycznej zapewniają mniejszą pojemność tych połączeń. Oba te czynniki sprzyjają projektowaniu szybkich układów scalonych. Przejście z aluminium/SiO₂ na Cu-low-k zaowocowało alternatywą dla konwencjonalnej sekwencji procesu technologicznego osadzania cienkich warstw, odwzorowywania wzoru w fotorezyście i trawienia. Ta nowa sekwencja procesu nazywana jest obróbką albo procesem damasceńskim. W tej sekwencji procesu najpierw osadzany jest dielektryk, a obszary, w których pożądane są ścieżki miedziane, są usuwane za pomocą konwencjonalnej metody fotolitografii i trawienia. W rezultacie w dielektryku pozostają rowki o wzorze pożądanym dla metalizacji miedzią. Gruba warstwa miedzi jest nakładana w celu wypełnienia rowków, a także na powierzchnię dielektryka. Cała powierzchnia płytki jest następnie polerowana metodą chemiczno-mechaniczną, tzw. process CMP, w celu usunięcia wierzchniej warstwy miedzi, pozostawiając pożądane ścieżki przewodzące tylko w obszarach rowków, oddzielone izolatorem dielektrycznym o niskiej stałej dielektrycznej. Istnieje wiele wariantów tej metody uzyskiwania połączeń metalicznych w układach scalonych. Opisany powyżej jest jednym z nich.

- BCD65 oferuje metalizację “stożkową” a właściwie dopasowaną do danego poziomu metalizacji, zapewniając wąskie, gęste linie połączeń na dolnych warstwach metalizacji oraz szersze i grubsze ścieżki metalizacji warstw wyższych, co zapewnia wysoką wydajność prądową, zasilanie i moc. Gęstość ścieżek jest ponadto ograniczona jedynie przez określone zasady odstępów między liniami przy wyższych napięciach.

- Kolejną istotną różnicą jest powierzchnia zajmowana przez izolację pojedynczego elementu np. tranzystora. W technologii niskonapięciowej BCD65 stosowana jest izolacja złączowa, w przeciwieństwie do technologii 180 nm – 5 V.

- Biblioteki cyfrowe zapewniają mniejsze cyfrowe komórki standardowe, co przekłada się na znaczną skalowalność obwodów cyfrowych. Pozwala to na trzykrotną poprawę upakowania bramek cyfrowych na chipie. W układzie scalonym można z łatwością dodać znacznie więcej funkcji cyfrowych.

- Zabezpieczenia przed wyładowaniami elektrostatycznymi (ESD) wykazują jedynie niewielką skalowalność, ponieważ wymiary są określane przez wymagania dotyczące pojemności energetycznej.

- Wartość Rsp ( specyficzna rezystancja włączenia tranzystora) układów wysokonapięciowych znacznie się poprawia w technologii BCD65. Układ DMOS 45 V wykazuje 40% poprawę w porównaniu z poprzednią podobną technologią BCD firmy onsemi.

Połączenie wszystkich tych czynników przekłada się na znaczący współczynnik skalowalności na poziomie produktu. Zostało to udowodnione poprzez przeprojektowanie produktu wykonanego w technologii BCD 180 nm na platformę onsemi Treo, wykorzystując technologię BCD 65 nm a następnie praktyczne wykonanie tego układu scalonego.

Jak już wspomniałem, układy wykonane na platformie Treo charakteryzują się limitem temperatury pracy 175°C. Więcej na ten temat można znaleźć w dokumencie “High Temperature Analog and Mixed-Signal Solutions Enabled by the Treo Platform”.

Zastosowanie Platformy Treo: Teledyne Technologies

Firma onsemi poinformowała 28 października 2025, że Teledyne Technologies wybrała platformę Treo do opracowywania układów scalonych odczytu danych z matrycy sensora podczerwieni (ROIC), w postaci dedykowanego układu scalonego ASIC. Jako najbardziej zaawansowana w branży platforma analogowa i cyfrowa, platforma Treo może być zastosowana do opracowania i wytwarzania specjalistycznych układów scalonych ROIC, aby sprostać wymaganiom systemów matryc ogniskowych w zakresie podczerwieni (Focal Plane Array FPA), które są niezbędne w szerokim zakresie zastosowań w lotnictwie, obronności, bezpieczeństwie i nauce. Pewnie wiele osób nie wie, że w maju 2021 roku firma Teledyne Technologies przejęła firmę FLIR, która była i obecnie jest – jako część Teledyne – światowym liderem w projektowaniu i produkcji kamer termowizyjnych, a pionierem tej technologii od lat 70. XX wieku.

Platforma Treo, której bazą jest technologia BCD65 65nm charakteryzuje się modułową architekturą i bogatym zestawem bloków konstrukcyjnych IP, które przyspieszają opracowanie i skracają wdrożenie nowych produktów. To idealna platforma projektowa i technologiczna dla układu ASIC-ROIC dla Teledyne Technologes.

Kluczowe cechy platformy Treo:

- Większa gęstość bramek zapewnia lepszą funkcjonalność i wydajność w mniejszej obudowie;

- Niższe rozpraszanie mocy poprawia efektywność energetyczną i wydłuża czas pracy w przypadku układów zasilanych z baterii;

- Możliwość obsługi dużych matryc detektorów podczerwieni bez zwiększania powierzchni chipu;

- Podłoża o niskiej rezystywności zapewniają większą odporność na promieniowanie w zastosowaniach kosmicznych i obronnych;

- Szeroki zakres temperatur zapewnia stałą wydajność w ekstremalnych warunkach, od kriogenicznych po temperatury stosowane w motoryzacji;

- Możliwość łączenia chipów (die stitching) wspiera projekty czujników wielkoformatowych w zaawansowanych systemach obrazowania

Łącznie te zaawansowane funkcje umożliwiają firmie Teledyne budowę mniejszych, szybszych i bardziej niezawodnych systemów obrazowania o krytycznych możliwościach, które skutecznie działają w ekstremalnych warunkach.

Teledyne Technologies ma centralę w Kaliforni USA i zatrudnia prawie 15 tysięcy osób na całym świecie. oferuje usługi foundry. Wartość giełdowa firmy to ok. 25 mld USD, a roczne obroty w roku 2024 wyniosły 5,67 mld USD. Zysk wyniósł prawie 820 mln USD, co daje marżę netto około 14,5%. Firma jest także producentem MEMS i ma dwie fabryki używające płytek krzemowych 150 i 200 mm. Obie o wydajności ok. 100 tys płytek rocznie.

Fabryki MEMS firmy Teledyne w Kanadzie

To przykład tego, jak duża firma zamawia w onsemi układ ASIC niezbędny we własnych produktach wytwarzanych w dużych ilościach.

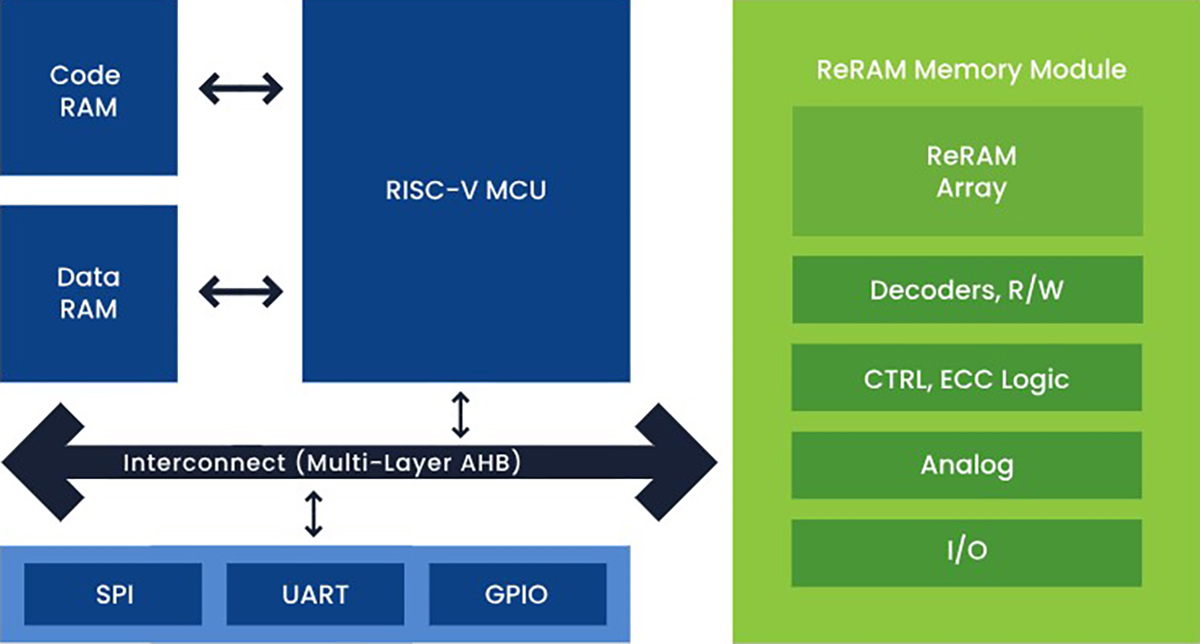

Zastosowanie Platformy Treo: Weebit Nano

Firma Weebit Nano poinformowała na początku października br., że wprowadziła do produkcji układy testowe z wbudowanym modułem rezystancyjnej pamięci o swobodnym dostępie (ReRAM/RRAM), wyprodukowane na płytkach krzemowych 300 mm w fabryce onsemi w East Fishkill, w stanie Nowy Jork. Układy są opracowywane na platformie Treo onsemi, która wykorzystuje proces 65 nm Bipolar-CMOS-DMOS (BCD65).

Wyprodukowanie tych testowych pamięci stanowi kluczowy krok w kierunku wdrożenia technologii Weebit ReRAM IP na platformie Treo. W przypadku projektów opartych na tej platformie, Weebit ReRAM zapewnia ultra-niskonapięciową pamięć NVM o wysokiej gęstości, która otwiera nowe poziomy integracji i funkcjonalności. Oczekuje się, że produkty nowej generacji onsemi wykorzystają tę przełomową technologię pamięci. Układy testowe zostaną teraz wykorzystane do ostatecznych testów i kwalifikacji przed planowaną produkcją seryjną.

Z tego komunikatu wynika, że Weebit Nano raczej nie będzie produkowała swoich produktów w onsemi, a jedynie sprzeda tej firmie IP do wdrożenia pamięci NVM RRAM w jej produktach.

Dlaczego te pamięci mają takie znaczenie?

Pamięć rezystancyjna o dostępie swobodnym Weebit ReRAM wychodzi naprzeciw rosnącemu zapotrzebowaniu na wydajne, niezawodne, energooszczędne i ekonomiczne rozwiązania pamięci nieulotnej (NVM). A dlaczego nie NVM Flash? eFlash nie da się już dalej skalować w dół jeżeli chodzi o rozmiar charakterystyczny. Pamięci firmy Weebit można będzie skalować aż do poziomu ok. 10 nm.

W zakładach Global Foundries, razem z francuską firmą CEA-Leti, wykonane zostały pamięci ReRAM w technologii 22nm FD-SOI (GF 22FDX®). Tak więc przejście na platformę Treo było dość proste. Trzeba pamiętać, że pierwsze prototypy tej pamięci były wykonane w technologii 130 nm. Ponadto pamięci Flash, wbudowane w mikrokontrolery, wymagają większej ilości dodatkowych masek i kroków procesu technologicznego, niż w przypadku pamięci ReRAM firmy Weebit Nano. To niewątpliwa zaleta tego typu pamięci.

Firma Weebit Nano, aby ułatwić proces projektowania produktów SoC zawierających pamięć ReRAM, dodatkowo zintegrowała początkowy moduł ReRAM w kompletny podsystem obejmujący mikrokontroler RISC-V (MCU), interfejsy systemowe, statyczną pamięć o swobodnym dostępie (SRAM) oraz urządzenia peryferyjne.

Embedded Demo-Chip z ReRAM firmy Weebit Nano

Weebit Nano powstała w 2011 roku w Izraelu jako start-up. Ma swoje biura i ośrodki badawcze w Izraelu i we Francji, ale – co ciekawe – jest notowana na giełdzie w Australii. Jej wartość giełdowa to tylko 735 mln USD. W 2024 roku osiągnęła obroty 678 mln USD, ale odnotowała 27,5 mln USD straty. Wartość jej akcji w ciągu ostatnich 12 miesięcy wzrosła o ponad 122%, co oznacza że inwestorzy wierzą w powodzenie tego projektu.

Możliwość zintegrowania pamięci ReRAM z układami analogowo-cyfrowymi onsemi, wykonanymi na bazie platformy Treo, to niewątpliwa zaleta.

Z tego przykładu widać, że także stosunkowo mała firmą może być partnerem dla onsemi, jeżeli tylko ma dobry produkt, a współpraca jest obopólnie korzystna. Oba przykłady natomiast pokazują, że platforma Treo może być istotna dla dalszego rozwoju układów scalonych analogowo-cyfrowych onsemi, a także dla przyszłości całej firmy.

onsemi przedstawia najbardziej zaawansowaną w branży platformę dla sygnałów analogowych i mieszanych

onsemi przedstawia najbardziej zaawansowaną w branży platformę dla sygnałów analogowych i mieszanych  Nowe, kompaktowe układy zabezpieczające przed ESD dla szybkich interfejsów komunikacyjnych

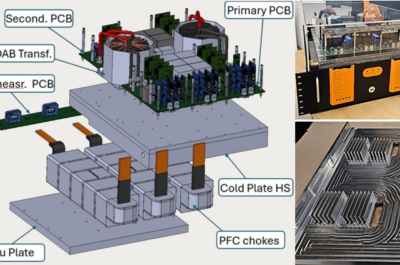

Nowe, kompaktowe układy zabezpieczające przed ESD dla szybkich interfejsów komunikacyjnych  onsemi przedstawia demonstrator technologii: 100-kilowatowy moduł na bazie SiC do szybkiego ładowania pojazdów elektrycznych

onsemi przedstawia demonstrator technologii: 100-kilowatowy moduł na bazie SiC do szybkiego ładowania pojazdów elektrycznych