Plany TSMC odnośnie rozwoju technologii wytwarzania układów półprzewodnikowych

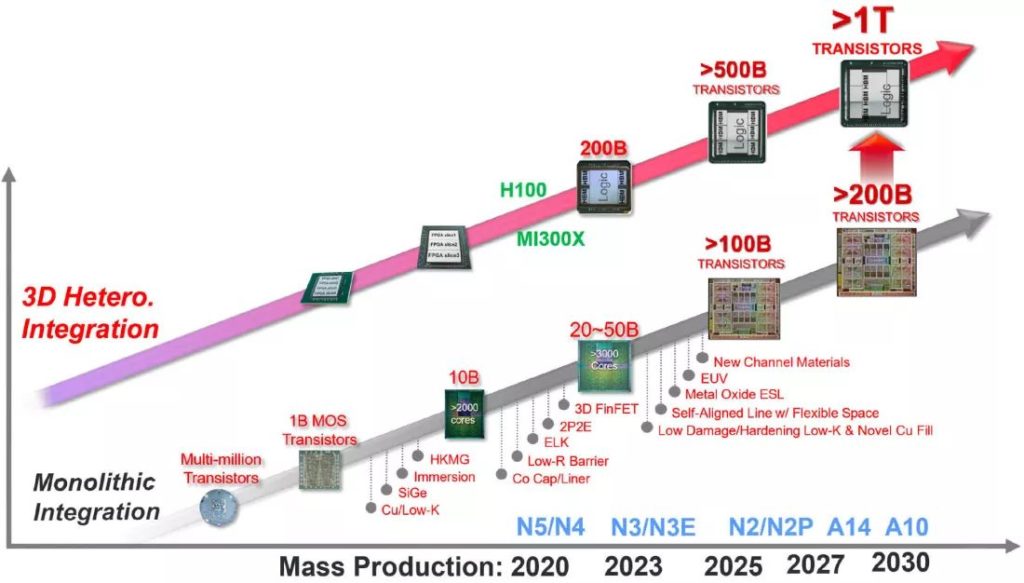

Podczas niedawnej konferencji IEDM poświęconej rozwojowi technologii wytwarzania półprzewodników, TSMC ogłosiło harmonogram technologiczny wprowadzania nowych procesów produkcyjnych. Aktualnie ostatecznym celem jest dostarczanie produktów opartych o chiplety w technologii 3D, które będą zawierały nawet bilion tranzystorów w jednej obudowie.

Eksperci przewidują, że ten cel będzie można osiągnąć dzięki nowoczesnym obudowom, jak CoWoS, InFO oraz SoIC. Do 2030 roku układy monolityczne będą w stanie pomieścić nawet 200 miliardów tranzystorów. Aktualnie jeden z najbardziej rozwiniętych procesorów monolitycznych na rynku, Nvidia GH100, zawiera ok. 80 miliardów tranzystorów. Natomiast TSMC uważa, że przyszłością są technologie chipletowe, takie jak AMD Instinct MI300X czy Intel Ponte Vecchio zawierający aż 100 miliardów tranzystorów.

Aktualnie TSMC rozwija procesy produkcyjne 2 nm – N2 oraz N2P, a także technologie 1,4 nm A14 oraz 1 nm – A10. Produkcja tranzystorów 1 nm jest spodziewana ok. 2030. W tym samym czasie Intel pracuje nad procesami 2 nm (20A) i 1,8 nm, które mają w pełni ruszyć w tym samym czasie. Jednak technologie Intela mają być nieco bardziej energooszczędne, dzięki technice PowerVia.

Źródło: Techspot.com

Unisystem i SoMLabs zacieśniają współpracę wzmacniając europejski rynek elektroniki

Unisystem i SoMLabs zacieśniają współpracę wzmacniając europejski rynek elektroniki  Creotech Quantum zamierza skomercjalizować system kwantowej dystrybucji klucza w 2026 roku

Creotech Quantum zamierza skomercjalizować system kwantowej dystrybucji klucza w 2026 roku  Procesory AMD Ryzen™ Embedded V3000 sercem przełączników Cisco N9300 oraz routerów z serii 8000 do obsługi obciążeń związanych z AI

Procesory AMD Ryzen™ Embedded V3000 sercem przełączników Cisco N9300 oraz routerów z serii 8000 do obsługi obciążeń związanych z AI