Zarządzanie ciepłem w zaawansowanych opakowaniach półprzewodników w latach 2026-2036

Dziesięcioletnia prognoza TIM1/TIM1.5 dla zaawansowanych opakowań półprzewodników (ASP) w podziale na grafen, ciekły metal, żel termiczny i folię indową. Prognoza dla chłodzenia mikroprzepływowego oraz szczegółowa analiza zarządzania temperaturą i energią dla ASP.

„TIM1” i „TIM1.5” odnoszą się do materiałów termoprzewodzących, które są używane w elektronice do poprawy odprowadzania ciepła. TIM1 to materiał umieszczany między układem scalonym a radiatorem, podczas gdy TIM1.5 to alternatywna konstrukcja, gdzie materiał znajduje się bezpośrednio na gołym rdzeniu i łączy się z radiatorem.

Wraz z rosnącymi wymaganiami w zakresie obliczeń sztucznej inteligencji i mocy obliczeniowej (TDP) wysokowydajnych chipów, a branża przechodzi z architektury opakowań 2,5D na 3D, zarządzanie temperaturą stało się kluczową barierą dla komercjalizacji i przyjęcia na dużą skalę. Aby sprostać temu wyzwaniu, branża bada szereg strategii, w tym wykorzystanie zaawansowanych materiałów termicznych (takich jak ciekły metal, diament i grafen), projekty chipów bez pokryw, optymalizację sieci zasilania, wdrożenie dostarczania mocy z tyłu oraz przyjęcie technologii chłodzenia cieczą i mikroprzepływowego.

Raport IDTechEx, „Thermal Management for Advanced Semiconductor Packaging 2026-2036: Technologies, Markets, and Opportunities„, zawiera kompleksową analizę przejścia z zaawansowanych opakowań półprzewodnikowych (ASP) 2,5D do 3D, postępów w metodach dostarczania energii (np. zasilanie od tyłu i przelotki krzemowe), wyzwań termicznych związanych z pakowaniem układów scalonych 3D, wykorzystaniem innowacyjnych materiałów termicznych (takich jak materiały interfejsu termicznego i podłoża diamentowe) oraz wdrażaniem technik chłodzenia cieczą, w tym systemów chłodzenia bezpośredniego, zanurzeniowego i mikroprzepływowego.

Wyzwania związane z zarządzaniem ciepłem dla opakowań półprzewodnikowych 2.5D i 3D

Od 2025 r. opakowania półprzewodnikowe 2.5D, takie jak technologia CoWoS firmy TSMC, pozostają dominującym podejściem do wysokowydajnych chipów, takich jak B200. Aby zwiększyć wydajność, szczególnie pod względem przepustowości i opóźnień, branża coraz bardziej koncentruje się na przejściu na pakowanie 3D. W przeciwieństwie do architektur 2.5D, w których matryca logiczna i pionowo ułożona pamięć o wysokiej przepustowości (HBM) są umieszczone obok siebie na wspólnym interpozytorze, pakowanie 3D obejmuje układanie aktywnej matrycy bezpośrednio na innej aktywnej matrycy. Ta pionowa integracja, choć obiecująca pod względem wzrostu wydajności, wprowadza znacznie większe wyzwania w zakresie zarządzania energią i temperaturą.

Wyzwania związane z zasilaniem w układach scalonych 3D

W układach scalonych 3D dostarczanie zasilania staje się znacznie bardziej złożone niż w układach 2D, ze względu na zwiększoną gęstość prądu, ograniczony dostęp do pinów i zastosowanie pionowych połączeń. K-poziomowy układ 3D pobiera około k razy więcej prądu niż układ 2D o tej samej powierzchni, ale piny zasilania i zasoby opakowania nie skalują się odpowiednio. Ta nierównowaga prowadzi do wielu wyzwań. TSV używane do dostarczania zasilania wprowadzają znaczną rezystancję, zwykle około 1 Ω na stos, co skutkuje większym spadkiem podczerwieni i trudnościami w utrzymaniu stabilnego napięcia zasilania. Zasilanie jest zwykle dostarczane przez dolną warstwę, która musi przenosić skumulowany prąd dla całego stosu, co czyni ją szczególnie podatną na spadki napięcia i dynamiczne zakłócenia. Sprawę dodatkowo komplikuje fakt, że energochłonne bloki obliczeniowe często znajdują się w pobliżu radiatora, również na dolnej kondygnacji. Tymczasem skuteczne odsprzęganie jest utrudnione przez ograniczoną przestrzeń, ponieważ TSV i gęste trasy zmniejszają obszar dostępny do umieszczenia kondensatorów odsprzęgających. Te połączone efekty pogarszają wahania napięcia w całym stosie, zwiększając zmienność wydajności, niepewność taktowania i ryzyko niezawodności, szczególnie w warunkach szczytowego obciążenia.

Wyzwania termiczne w układach scalonych 3D

Zarządzanie ciepłem jest jednym z najbardziej krytycznych wąskich gardeł w układach scalonych 3D. W przeciwieństwie do konstrukcji 2D, w których ciepło rozprasza się bocznie i w górę w kierunku radiatora, stosy 3D składają się z cieńszych matryc, które ograniczają boczne rozprzestrzenianie się ciepła. Ponadto, środkowe matryce są podatne na akumulację ciepła, ponieważ znajdują się dalej od radiatora i mają ograniczone efektywne ścieżki odprowadzania ciepła. Co więcej, pionowa ścieżka odprowadzania ciepła jest ograniczona przez niską przewodność cieplną materiałów między matrycami, takich jak warstwy dielektryczne i kleje łączące. Prowadzi to do powstawania gorących punktów termicznych, które pogarszają wydajność i zmniejszają niezawodność z powodu zwiększonego wycieku i naprężeń na połączeniach. Inną kluczową kwestią jest bliskość bloków logicznych o dużej mocy i pamięci, co może skutkować znacznym sprzężeniem termicznym między warstwami, co dodatkowo komplikuje projektowanie termiczne. Konwencjonalne metody chłodzenia często nie są w stanie skutecznie dotrzeć do ukrytych warstw, co sprawia, że konieczne jest rozważenie alternatywnych technik, takich jak termiczne TSV i chłodzenie mikroprzepływowe na poziomie chipa. Metody te wprowadzają jednak własne kompromisy pod względem złożoności projektu, kosztów i wyzwań związanych z integracją.

Innowacje materiałowe dla bardziej wydajnego transferu ciepła

Aby wspierać bardziej wydajne zarządzanie ciepłem zarówno w opakowaniach półprzewodnikowych 2.5D, jak i 3D, branża aktywnie bada kilka innowacyjnych rozwiązań. Jednym z kluczowych obszarów zainteresowania jest rozwój zaawansowanych materiałów interfejsu termicznego (TIM). Raport IDTechEx, „Thermal Management for Advanced Semiconductor Packaging 2026-2036: Technologies, Markets, and Opportunities”, oferuje szczegółową analizę technologii TIM, w szczególności TIM1 i powstającej kategorii TIM1.5. Materiały te obejmują takie opcje, jak ciekły metal, folia indowa, arkusze grafenowe i żele termiczne nowej generacji o zwiększonej przewodności cieplnej.

Od 2025 r. X23 firmy Shin-Etsu pozostaje powszechnie stosowanym materiałem TIM1 do zastosowań w matrycach kulkowych (BGA). Jednak wraz z rosnącą mocą projektowania termicznego w zaawansowanych chipach, branża coraz częściej zwraca się ku nowym materiałom TIM1 i TIM1.5, które oferują wyższą wydajność. Obiecującymi kandydatami są ciekły metal, materiały na bazie grafenu i żele termiczne wypełnione wysoce przewodzącymi wypełniaczami.

Równolegle następuje odejście od tradycyjnej dwuwarstwowej struktury TIM (TIM1 i TIM2) na rzecz pojedynczej warstwy TIM1.5. Ma to na celu zmniejszenie oporu cieplnego poprzez zminimalizowanie interfejsów materiałowych. Chociaż może to zmniejszyć liczbę używanych warstw TIM, niekoniecznie obniża ogólny rynek, ponieważ materiały TIM1.5 mają tendencję do generowania wyższych kosztów jednostkowych ze względu na ich wymagające specyfikacje techniczne. IDTechEx prognozuje, że połączony rynek TIM1 i TIM1.5 wzrośnie do około 500 milionów USD do 2036 rokue. Obiecującym obszarem badań jest również wykorzystanie diamentu pokrytego miedzią, jako podłoża dla wysokiej klasy opakowań półprzewodnikowych.

Chłodzenie cieczą, chłodzenie zanurzeniowe i chłodzenie mikroprzepływowe

Oprócz innowacji materiałowych, aktywne chłodzenie cieczą staje się coraz ważniejszym trendem w zaawansowanym zarządzaniu ciepłem. W wysokowydajnych centrach danych, technologie takie jak chłodzenie direct-to-chip i chłodzenie zanurzeniowe zostały już wdrożone komercyjnie. Warto zauważyć, że przyjęcie chłodzenia zimną płytą w konfiguracjach GB200 i NVLink72 firmy Nvidia w ubiegłym roku jeszcze bardziej ugruntowało jego pozycję jako dominującego rozwiązania w najbliższej przyszłości. IDTechEx spodziewa się, że chłodzenie zimną płytą pozostanie wiodącym podejściem przez co najmniej kolejne 2-3 lata.

Jednak zarówno chłodzenie zimną płytą, jak i chłodzenie zanurzeniowe zajmują się przede wszystkim rozpraszaniem ciepła z pakietu chipów do otoczenia. Bardziej palącym wyzwaniem termicznym jest samo opakowanie – a konkretnie zarządzanie ciepłem generowanym między pionowo ułożonymi komponentami w architekturze opakowań 3D. Do tej pory branża nie wypracowała jeszcze jasnego rozwiązania tej kwestii.

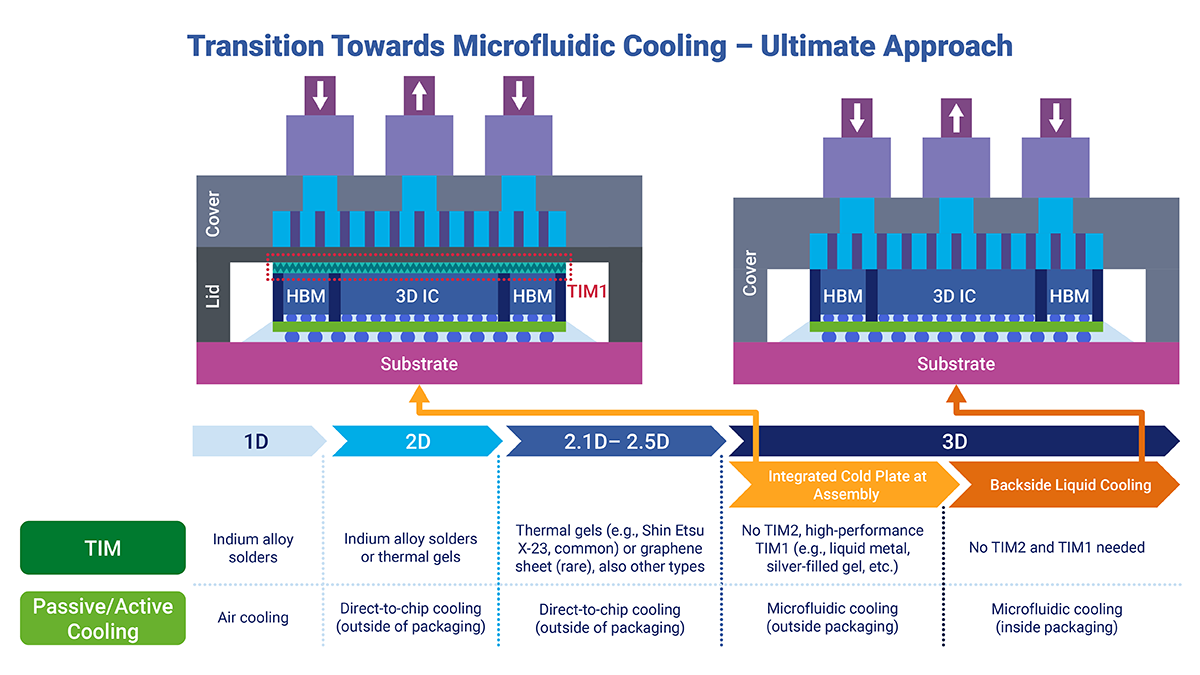

IDTechEx identyfikuje chłodzenie mikroprzepływowe jako obiecującego kandydata do rozwiązania tego wewnętrznego wąskiego gardła termicznego, pomimo złożoności związanej z jego wdrożeniem. Chłodzenie mikroprzepływowe wykorzystuje skomplikowane sieci mikrokanałów do cyrkulacji ciekłego chłodziwa w pokrywie opakowania lub bezpośrednio wewnątrz struktury opakowania. Chociaż opracowywane są różne konfiguracje architektoniczne, technologia ta wciąż napotyka kilka przeszkód, w tym wysoką złożoność projektu i produkcji, obawy dotyczące skalowalności i ograniczone dane dotyczące długoterminowej niezawodności.

Chłodzenie i architektura termiczna zaawansowanych opakowań 3D. Źródło: IDTechEx

Podsumowanie

Wraz z przejściem na pakowanie 3D w celu uzyskania większej przepustowości i wydajności, zaproponowano i zbadano wiele rozwiązań (np. dostarczanie mocy od tyłu, zintegrowany regulator napięcia, zaawansowane TIM1, chłodzenie mikroprzepływowe itp. Od połowy 2025 r. nadal istnieją znaczące wyzwania, takie jak kompromis między gęstością TSV, złożonością produkcji i wskaźnikiem defektów, równowaga między chłodzeniem mikroprzepływowym a skalowalnością komercyjną.

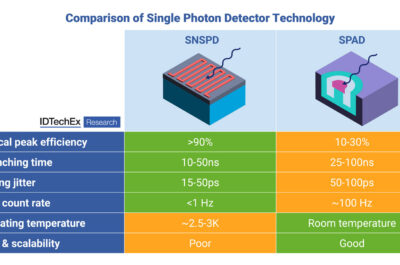

IDTechEx bada fotodetektory półprzewodnikowe i nadprzewodnikowe w technologiach kwantowych

IDTechEx bada fotodetektory półprzewodnikowe i nadprzewodnikowe w technologiach kwantowych  IDTechEx przygląda się temu, dokąd zmierzają drukowane czujniki

IDTechEx przygląda się temu, dokąd zmierzają drukowane czujniki  Prognoza innowacji technologicznych IDTechEx na lata 2025-2035

Prognoza innowacji technologicznych IDTechEx na lata 2025-2035