Xilinksowy pomysł na „7”: nowe rodziny FPGA

W odróżnieniu od dotychczas dostępnych w sprzedaży układów FPGA, wprowadzone do produkcji przez firmę Xilinx trzy nowe rodziny o nazwach: Virtex-7, Kintex-7 oraz Artix-7, oparte są na zunifikowanej architekturze (ASMBL), składającej się z następujących elementów:

– zespołów uniwersalnych komórek logicznych CLB, które są bardzo podobne do stosowanych w układach Virtex-6 (z 6-wejściową LUT),

– konfigurowalnych bloków pamięci RAM, które mogą pracować w trybie FIFO, DualPort SRAM, ROM i jako standardowy RAM – ich konstrukcja została również zaczerpnięta z układów Virtex-6,

– konfigurowalnych bloków DSP (o organizacji 25×18 i 48-bitowym akumulatorem), które mogą pracować jako bloki MAC lub szybkie ALU, z opcjonalnym detektorem sekwencji – podobne do stosowanych w układach Virtex-6,

– systemu generacji i dystrybucji sygnałów zegarowych MMCM (Mixed-Mode Clock Manager), pochodny rozwiązaniom stosowanym w układach Virtex-6, zasilający 32 globalne linie zegarowe.

Producent przewidział także przeniesienie do nowych układów innych elementów wyposażenia z układów Virtex-6 i Spartan-6, przede wszystkim:

– transceiverów GTP, GTX i GTH, a także PCS/PMA (choć z zastrzeżeniem, że wyłącznie ze względu na chęć zachowania kompatybilności z układami starszych generacji),

– 12-bitowych przetworników A/C o częstotliwości konwersji 1 MHz, współpracujące z czujnikami umożliwiającymi monitorowanie parametrów pracy układu FPGA (napięcia, temperatura) oraz napięć zewnętrznych w czym jest pomocny 17-kanałowy multiplekser analogowy,

– systemy ochrony własności intelektualnej, w tym blok kryptograficzny AES256 z nieulotną pamięcią klucza eFUSE,

– wydzielone bloki interfejsów PCIe (do Gen3 włącznie).

O ile pierwsze bloki z pierwszej grupy wchodzą – w różnej liczbie – w skład wszystkich układów FPGA z serii Xilinx-7, to pozostałe są wyposażeniem opcjonalnym. Zestawienie charakteryzujące elementy wyposażenia układów z serii Xilinx-7 przedstawiono w tab. 1.

Producent pozycjonuje nowe układy w następujący sposób:

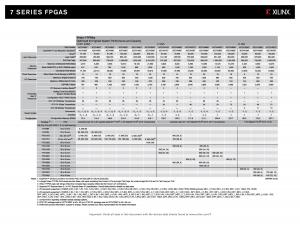

– Virtex-7 – układy o największych zasobach logicznych, przeznaczone do najbardziej zaawansowanych aplikacji, w których duże znaczenie mają parametry czasowo-częstotliwościowe struktur FPGA,

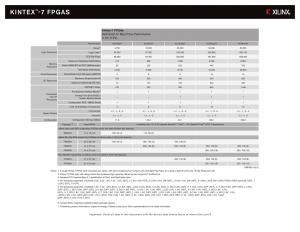

– Kintex-7 – układy o zasobach logicznych znacznie mniejszych niż Virtex-7, wyposażona w szybkie interfejsy komunikacyjne o dużej szybkości pracy (jak w Virtex-7),

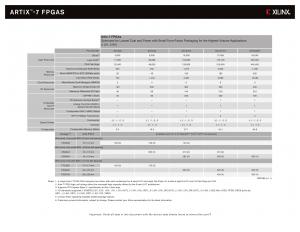

– Artix-7 – układy będące tańszymi, dostarczanymi w mniejszych obudowach, odpowiednikami układów Spartan-6.

| Technologia półprzewodnikowa HKMG (High-k Metal Gate) jest wykorzystywana m.in. przy produkcji mikroprocesorów iCore firmy Intel, sięgnęła po nią także firma Xilinx, wykorzystując jej 28-nm wersję do produkcji układów FPGA z rodzin Xilinx-7 (Virtex-7, Kintex-7 oraz Artix-7). Producent uzyskał w ten sposób znaczne obniżenie poboru mocy, zachowując jednocześnie dużą szybkość ich pracy. |

Tab. 1. Zestawienie podstawowych cech i wyposażenia układów FPGA z rodzin Xilinx-7 (podano wartości maksymalne)

|

Parametr |

Artix-7 |

Kintex-7 |

Virtex-7 |

|

Liczba komórek logicznych |

352k |

407k |

1955k |

|

Pojemność BlockRAM |

12 Mb |

29 Mb |

65 Mb |

|

Liczba bloków DSP |

700 |

1540 |

3960 |

|

Liczba wbudowanych transceiverów |

4 |

16 |

80 |

|

Maksymalna przepływność transceiverów |

3,75 Gb/s |

10,3125 Gb/s |

13,1 Gb/s |

|

Inerfejsy PCIe |

Gen1 x 4 |

Gen2 x 8 |

Gen3 x 8 |

|

Przepływność portu danych pamięci |

800 Mb/s |

2133 Mb/s |

2133 Mb/s |

|

Liczba linii I/O |

450 |

500 |

1200 |

Podczas projektowania układów z rodzin Xilinx-7 brano pod uwagę konieczność udostępnienia maksymalnie dużych zasobów logicznych przystosowanych do pracy z sygnałami o dużych częstotliwościach przy jednoczesnym zminimalizowaniu pobieranej mocy. Z tego powodu do produkcji nowych układów zastosowano nowoczesną technologię półprzewodnikową o wymiarze charakterystycznym 28 nm, noszącą nazwę High-k Metal Gate (HKMG), w której zastąpiono izolator bramki wykonany z dwutlenku krzemu izolatorem wykonanym z syntetycznego materiału o nazwie hafnium, dzięki któremu upływność bramki jest pomijalnie mała. Nie ma obecnie dostępnych pełnych danych katalogowych owych układów, ale z dostępnych materiałów wynika, że układy z rodzin Xilinx-7 będą pobierały o ok. 50% mniej energii niż ich odpowiedniki z serii Xilinx-6, przy jednoczesnym zwiększeniu maksymalnej częstotliwości taktowania o 20…40%. Obniżenie poboru mocy wynika także z zastosowania napięcia zasilającego rdzeń FPGA o wartości 1 V lub – w wersjach specjalnych – 0,9 V. Linie I/O wszystkich prezentowanych w artykule układów mogą współpracować z systemami cyfrowymi zasilanymi napięciami o wartości do 3,3 V.

Szczegółowe porównanie zasobów logicznych oferowanych przez poszczególne rodziny nowych układów FPGA firmy Xilinx przedstawiono poniżej.

|

Kintex-7 |

Virtex-7 |

Artix-7 |

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii