Nowa rodzina układów CPLD w ofercie Altery: MAX V

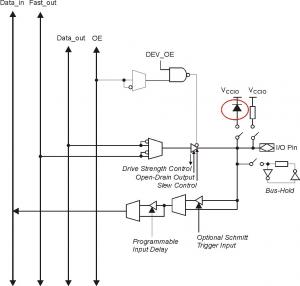

Rys. 10. Budowa komórki I/O w układzie z rodziny MAX V (diodę umożliwiającą pracę linii IO z napięciami powyżej 3,6V zaznaczono czerwonym kółkiem)

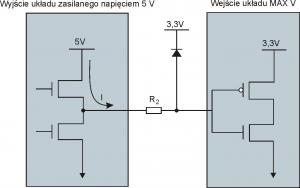

Widoczna na rysunku dioda zabezpieczająca linie wejściowe przed napięciem o zbyt dużej wartości (w czerwonym kółku) jest – niestety – dostępna tylko w niektórych (o największych zasobach logicznych – 5M1270Z oraz 5M2210Z, co zapewnia kompatybilność tych linii ze standardem PCI2.2/33 MHz) typach układów MAX V. Z tego powodu w przypadku stosowania układów MAX V w systemach zasilanych napięciem 5 V konieczne będzie zastosowanie nie tylko zewnętrznego rezystora ograniczającego prądu wejściowy, ale także diody dołączonej w sposób pokazany na rys. 11.

Rys. 11. Sposób dołączenia linii I/O układu MAX V do systemu cyfrowego zasilanego napięciem 5 V

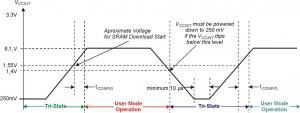

Rys. 12. Charakterystyka czasowo-napięciowa funkcji układów MAX V

Układy MAX V są konstrukcyjnie przystosowane do pracy w systemach hot-socketing, dzięki czemu wszystkie linie I/O automatycznie są przełączane w stan wysokiej impedancji w chwili włączania i wyłączania napięcia zasilającego (rys. 12), dzięki czemu logika zaimplementowana w układzie nie wpływa negatywnie na pracę całego systemu na przykład podczas montażu lub demontażu pakietu. Komórki I/O układów MAX V oferują ponadto możliwość transmisji (wyłącznie w trybie nadawczym) sygnałów różnicowych w standardach LVDS (Low-Voltage Differential Signaling) i RSDS (Reduced Swing Differential Signaling), dzięki czemu możliwy jest szeregowy transfer danych z prędkością do 400 Mb/s.

Układy MAX V są przystosowane do zasilania napięciem o wartości 1,8 V, a ich linie I/O mogą być zasilane napięciem z zakresu od 1,2 do 3,3 V. Dzięki podziałowi grup linii I/O na banki (w układach od 5M40 do 5M240 są dwa, w układach 5M1270 i 5M2210 jest ich cztery) układy MAX V mogą bezproblemowo pracować w systemach wielonapięciowych, bez konieczności stosowania translatorów poziomów logicznych (poza wspomnianym wyjątkiem przy zasilaniu napięciem 5 V). Niskie napięcie zasilania oraz nowoczesna technologia produkcji układów MAX V zapewniają niewielki pobór mocy podczas pracy, do którego oszacowania może się przydać interaktywny arkusz kalkulacyjny udostępniony przez producenta na firmowej stronie internetowej.

| W układach MAX V producent przewidział możliwość implementacji cyfrowego syntezera sygnałów zegarowych z pętlą PLL. W obecnie dostępnej wersji pakietu Quartus II (10.1) nie można wykorzystać tej możliwości, ma to być możliwe w chwili udostępnienia przez Alterę nowej wersji pakietu Quartus II (11.0). Nie jest obecnie jasne, która część syntezera jest „twardo” zaimplementowana w krzemie, a która jego część będzie zajmowała uniwersalne zasoby logiczne (co producent zapowiada, ale ogólnikowo). |

Podsumowanie

Konstruktorzy korzystający w swoich aplikacjach z układów MAX II nie będą zaskoczeni budową, możliwościami i wyposażeniem oferowanym przez układy MAX V, są one bowiem ich udoskonaloną i – miejmy nadzieję – tańszą wersją. Rozwiązania zastosowane w MAX V nie należą do przełomowych, ale zwiększając wygodę realizacji projektów w i z CPLD, mają szansę zwiększyć powszechność ich stosowania, mogą także pomóc producentowi utrzymać status lidera rynku PLD.

| Dodatkowe informacje o układach MAX V są dostępne pod adresem: http://www.altera.com/maxv |

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485