Optymalizacja zasilania układów FPGA

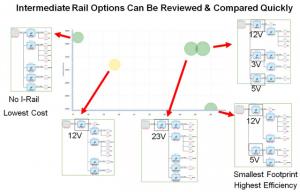

Każda architektura ma inny zestaw podzespołów co skutkuje różnym rozmiarem, wydajnością oraz kosztem całkowitym. Jedna z pokazanych możliwości nie ma szyny pośredniej podczas gdy inne mają jedną, dwie a nawet trzy szyny pośrednie pracujące z różnymi napięciami. Każde z tych rozwiązań daje inne możliwości minimalizacji rozmiaru, maksymalizacji wydajności oraz zmniejszania kosztów.

Rys. 14.

Na stronie View/Edit znajdują się wykresy kołowe, które prezentują wkład poszczególnych podzespołów do dyssypacji mocy, zwiększania rozmiaru oraz całkowitego kosztu. Klikając na podzespół użytkownik uzyskuje dostęp do dodatkowych informacji.

W ten sposób użytkownik może określić czy którykolwiek podzespół ma decydujący wpływ na kształt rozwiązania i podjąć próbę korekty. Na przykład jeżeli jeden elementów ma decydujący wpływ na rozmiar całego układu użytkownik może go zamienić na mniejszy jeżeli istnieje taka możliwość.

Następnie należy kliknąć przycisk Create Project Design by zapisać projekt i przejść do kolejnego kroku.

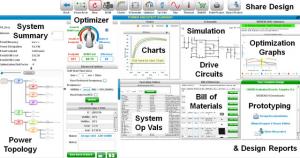

Rys. 15.

Kiedy projekt jest gotowy i zapisany zostaje otwarty w środowisku WEBENCH. Po lewej pojawia się schemat blokowy układu.

Do każdego z podzespołów można uzyskać dostęp poprzez kliknięcie odpowiedniego bloku. Projektant uzyskuje wtedy możliwość użycia wszystkich funkcji WEBENCH takich jak:

- ocena i zmiana kosztów układu

- wyświetlanie wykresów parametrów pracy podzespołów tj. wydajność w funkcji prądu, symulacji przewodnictwa elektrycznego, symulacji przewodnictwa cieplnego (jeżeli dostępna)

- zamówienie zestawu do konstrukcji prototypu za pomocą WEBENCH Build It (jeżeli dostępne)

W lewym górnym rogu znajdują się ogólne parametry układu: wydajności układu: całkowity koszt oraz rozmiar.

Rys. 16.

WEBENCH Power Designer udostępnia wiele zaawansowanych możliwości symulacji oraz narzędzi do testowania zapisanego projektu.

Rys. 17.

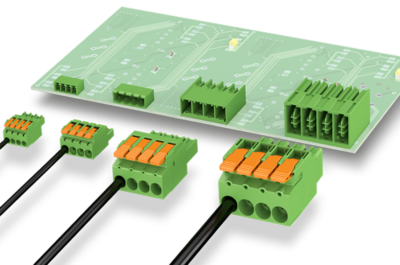

Nowe generacje złączy: innowacyjne metody połączeń w elektronice

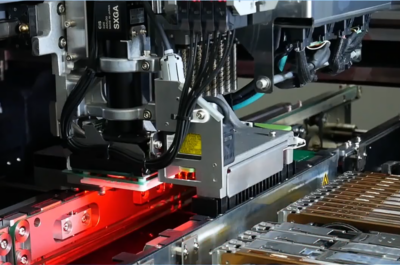

Nowe generacje złączy: innowacyjne metody połączeń w elektronice  Zaawansowane urządzenia do montażu SMT na przykładzie automatu P&P RS-2 – analiza technologiczna i zastosowania w nowoczesnej produkcji elektroniki

Zaawansowane urządzenia do montażu SMT na przykładzie automatu P&P RS-2 – analiza technologiczna i zastosowania w nowoczesnej produkcji elektroniki  Wdrażanie fizycznej AI na obrzeżach sieci radiowej w systemach obronnych

Wdrażanie fizycznej AI na obrzeżach sieci radiowej w systemach obronnych