Obsługa interfejsu CAN w mikrokontrolerach STM32

CAN w STM32

Interfejs magistrali CAN wbudowany w mikrokontrolery STM32 oferuje wiele dodatkowych możliwości, które pozytywnie wpływają na łatwość ich wykorzystania w sieciach CAN. Zarówno część odbiorcza kontrolera, jak i część nadawcza są wyposażone w sprzętowo zarządzane bufory mogące przechowywać odebrane (przeznaczone do wysłania) ramki, są tzw. skrzynki pocztowe (mailbox). Nadajnik ma zaimplementowane trzy skrzynki, o których kolejności wysyłania decyduje planista (scheduler). Dane przeznaczone do wysłania mogą być wpisywane tylko do pustych skrzynek. Po zapisaniu skrzynka ma nadawany status przyjęcia do realizacji i, w zależności od priorytetu skrzynki, oczekuje na zwolnienie magistrali, lub na wcześniejsze wysłanie zawartości skrzynek o wyższym priorytecie. Po zakończeniu wysyłania skrzynka uzyskuje status pustej i jest gotowa do ponownego zapisu.

Bufory odbiorcze (skrzynki) części odbiorczej są zorganizowane w kolejki FIFO. Poprawnie odebrane dane są zapisywane kolejno w poszczególnych skrzynkach. Jeśli wszystkie trzy skrzynki zostaną zapełnione danymi, a aplikacja na czas nie odczyta ich zawartości, to zachowanie kontrolera CAN, w zależności od ustawień może być dwojakie. Nowo odebrana wiadomość może być odrzucona, wtedy w buforach przechowywane są trzy najstarsze wiadomości. Najświeższa wiadomość może też nadpisywać zawartość skrzynek, dzięki czemu przechowywane będą zawsze najnowsze wiadomości, a starsze będą tracone.

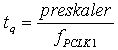

Komunikacja po magistrali CAN odbywa się z ustaloną prędkością, wyznaczaną przez czas trwania jednego bitu. Wyznaczenie cyklu transmisji jednego bitu (bit timing) nie jest tak oczywiste jak ma to miejsce w większości szeregowych interfejsów komunikacyjnych. Ważnym pojęciem jest kwant czasu, ponieważ prędkość komunikacji jest determinowana przez jego wielokrotność. Kwant czasu to okres sygnału zegarowego magistrali PCLK1 podzielonego przez wartość preskalera kontrolera CAN.

Standard CAN definiuje cztery segmenty czasowe, na które podzielony jest czas trwania jednego bitu:

- segment synchronizacji SYNC_SEG,

- segment kompensacji czasu propagacji magistrali PROP_SEG,

- dwa segmenty wyznaczające miejsce próbkowania bitu – PHASE_SEG1 oraz PHASE_SEG2.

Pierwsze pole czasowe bitu, czyli segment synchronizacji, trwa tyle ile jeden kwant czasu. Wtedy to spodziewana jest ewentualna zmiana bitu. Dwa następne segmenty, czyli blok przeznaczony na kompensację propagacji magistrali (Propagation Time Segment) oraz segment wskazujący chwilę próbkowania PHASE_SEG, są często łączone w jeden blok Bit segment 1 (BS1). Kontroler CAN w mikrokontrolerach STM32 również korzysta z modelu trójsegmentowego.

Rys. 8. Cykl transmisji bitu w dla zaimplementowanych w mikrokontrolerach STM32 kontrolerów CAN (źródło: ST)

Na rys. 8 przedstawiono cykl transmisji bitu w interfejsach wbudowanych w mikrokontrolery STM32. Czas trwania segmentów BS1 oraz BS2 mogą ulegać automatycznej zmianie w celu kompensacji różnic częstotliwości pracy węzłów podłączonych do magistrali. Czas trwania segmentu BS1 jest programowalny i może wynosić od jednej do 16 wielokrotności kwantu czasu. Segment BS2 może trwać maksymalnie osiem kwantów czasu.

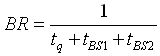

Prędkość komunikacji to odwrotność sumy czasów trwania wszystkich segmentów, można ją zatem wyznaczyć z zależności:

gdzie:

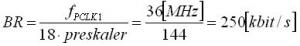

Należy zaznaczyć, że wartość preskaler oznacza tutaj liczbę wpisaną do struktury inicjującej kontroler CAN, a nie wartość wpisywaną do rejestru preskalera. Żeby osiągnąć ten sam efekt bez użycia funkcji API firmy ST, należałoby do rejestru preskalera wpisać wartość preskaler – 1. Sposób wyznaczania prędkości komunikacji stanie się bardziej zrozumiały po zapoznaniu się z poniższym przykładem. Celem jest osiągnięcie prędkości 250 kbit/s.

Częstotliwość PCLK1 wynosi zazwyczaj 36 MHz. Przyjmując czasy trwania segmentów BS1 i BS2 odpowiednio: 10 i 7 wielokrotności kwantu czasu oraz preskaler = 8, otrzymujemy:

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485