Freescale Coldfire i Kinetis od środka

Rdzeń ARM Cortex-M4

Rdzeń ARM Cortex-M4 jest zbudowany w oparciu o swojego poprzednika, ARM Cortex™-M3. Ponadto łączy w sobie cechy mikrokontrolera i procesora DSP. Cortex-M4 implementuje zestaw instrukcji ARMv7-ME™ Thumb2, co zapewnia kompatybilność z układami Cortex-M3 oraz daje wiele nowych możliwości poprzez dodatkowe instrukcje DSP i SIMD. Rdzeń ARM Cortex-M4 może też opcjonalnie mieć zintegrowaną jednostką zmiennoprzecinkową (Floating-Point Unit, FPU) pojedynczej precyzji, która zawiera zestaw 32 32-bitowych rejestrów zmiennoprzecinkowych dla danych.

Na rysunku 2 pokazano podstawowy model programowania dla użytkownika, w którym widać:

- 13 rejestrów ogólnego przeznaczenia (r[0-12]),

- wskaźnik stosu (Stack Pointer, r13 = SP), rejestr obsługi powrotu z procedury (Link Register, r14 = LR) oraz licznik programu (Program Counter, r15 = PC),

- rejestry stanu programu (Program Status Registers, xPSR)

Model programowy procesora definiuje operacje zmiennej długości z instrukcjami 16- i 32-bitowymi. Obsługiwane są 8-, 16- i 32-bitowe operandy całkowite oraz pola bitowe o szerokości od 1 do 32 bitów.

Rdzenie ARM Cortex-Mx zostały zaprojektowane z myślą o zastosowaniach, w których całościowy rozmiar układu i przewidywalne działanie są ważniejsze niż duża wydajność. W związku z tym, rdzeń Cortex-M4 wykorzystuje trójstopniową mikroarchitekturę potokową (three-stage pipeline), na którą składają się fazy: pobrania instrukcji, dekodowania jej i wykonania.

Dodatkowe instrukcje DSP i SIMD są wykonywane w strukturze typu MAC. Prawie wszystkie instrukcje mnożenia (i opcjonalnie akumulacji) mają czas wykonania równy jeden cykl.

ARM Cortex-M4 implementuje kilka 32-bitowych magistral interfejsowych, dzięki czemu może pracować w architekturze Harvard. W szczególności rdzeń zapewnia zmodyfikowane połączenie typu Harvard poprzez magistrale typu AHB: kodową i systemową. Magistrala kodowa jest zwykle używana do pobierania instrukcji i realizowania dostępu do danych, a magistrala systemowa – do komunikacji z pamięcią RAM i peryferiami. Osobna, 32-bitowa magistrala peryferyjna (Private Peripheral Bus, PPB), wykorzystywana do komunikacji z kilkoma ważnymi modułami (np. wektorowym kontrolerem przerwań NVIC) jest dostępna jedynie dla rdzenia.

Kompatybilność i skalowalność

Mikrokontrolery z rodzin Kinetis osiągnęły niespotykaną skalowalność i są wyjątkowo kompatybilne między sobą, co daje możliwość uproszczenia projektowania zarówno części programowej, jak i sprzętowej. Wszystkie rodziny współdzielą następujące cechy:

- szeroki zakres napięć zasilania (1,71 – 3,6 V), z zachowaniem możliwości programowania pamięci Flash oraz wykonywania operacji analogowych przy napięciu 1,71 V,

- zakres temperatur pracy od -40°C do +105°C,

- elastyczność w wyborze wydajności – układy o maksymalnych częstotliwościach pracy od 50 do 150 MHz,

- różne rodzaje obudów, od 32-pinowej QFN (o rozmiarach 5×5 mm) do 256-wyprowadzeniowej MAPBGA,

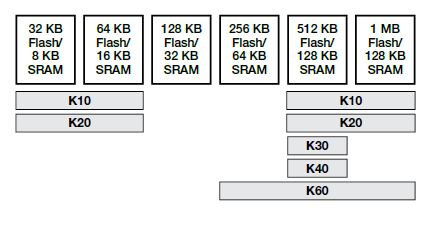

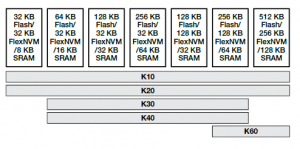

- duży wybór rozmiarów wbudowanych pamięci, od 32 kB Flash i 8 kB SRAM do 1 MB Flash i 128 kB SRAM, z wieloma matrycami komórek pamięci Flash, pozwalającymi na odczyt w czasie trwania zapisu,

- trwały, wbudowany EEPROM z możliwością zapisu bajtowego, o rozmiarach od 32 B do 16 kB, pozwalający na ponad 10 milionów cykli zapisu i odczytu,

- identyczne peryferia i mapy pamięci, ułatwiające powtórne wykorzystanie kodu,

- rdzeń ARM Cortex-M4, z obsługą instrukcji DSP i opcjonalną jednostką zmiennoprzecinkową pojedynczej precyzji,

- standardowy, szeregowy interfejs debugujący IEEE® 1149.1 JTAG oraz kompaktowy IEEE 1149.7 JTAG, a oprócz tego architektura ARM CoreSight™, pozwalająca na śledzenie pracy procesora i bardziej zaawansowane debugowanie,

- 10 różnych trybów oszczędzania energii, do wyboru w czasie zwykłej pracy (run), wstrzymania (wait) lub całkowitego zatrzymania (stop),

- trwałe wyprowadzenia, tolerujące napięcie 5V.

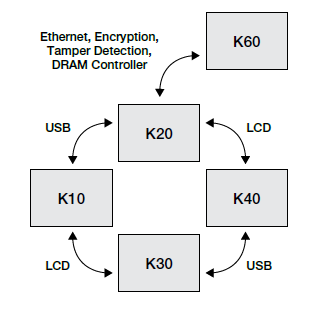

Rys. 3. Kompatybilność rodzin mikrokontrolerów Kinetis

Tab. 1. Rodziny mikrokontrolerów Kinetis

| Rodzina | Wyróżniające peryferia |

| K10 | Podstawowe |

| K20 | Podstawowe + USB |

| K30 | Podstawowe + LCD |

| K40 | Podstawowe + USB + LCD |

| K60 | Podstawowe + USB + Ethernet + szyfrowanie + kontroler DRAM + detekcja przekłamań (tamper detect) |

Rys. 4. Porównanie rozmiarów pamięci dostępnych w rodzinach Kinetis (bez pamięci FlexMemory)

Rys. 5. Porównanie rozmiarów pamięci dostępnych w rodzinach Kinetis (z pamięcią FlexMemory)

Bezpieczeństwo AI pod presją. Cisco publikuje raport „State of AI Security 2026”

Bezpieczeństwo AI pod presją. Cisco publikuje raport „State of AI Security 2026”  IPC-A-610 i IPC-J-STD-001: Nierozłączny duet w profesjonalnej produkcji elektroniki

IPC-A-610 i IPC-J-STD-001: Nierozłączny duet w profesjonalnej produkcji elektroniki  Nie ma rzeczy niemożliwych: polska elektronika na ISS

Nie ma rzeczy niemożliwych: polska elektronika na ISS