Podstawy bezpośredniej syntezy cyfrowej (DDS)

Rozdzielczość przetwornika jest zazwyczaj o 2 do 4 bitów niższa, niż szerokość tablicy wartości. Nawet dokładnie N-bitowy przetwornik DAC wnosiłby dodatkowy szum kwantyzacji do sygnału. Na rysunku 4 przedstawiono obliczone widmo sygnału wyjściowego dla 32-bitowego akumulatora fazy i obcięcia fazy do 15 bitów. Wartość M została tak dobrana, aby częstotliwość wyjściowa była nieco odsunięta od 0,25 częstotliwości zegara. Można zauważyć, że dodatkowe częstotliwości wnoszone przez obcięcie fazy i skończoną rozdzielczość przetwornika są przynajmniej 90 dB poniżej generowanego sygnału. Jest to znacznie więcej, niż oferują jakiekolwiek dostępne przetworniki 12-bitowe i wystarcza do większości zastosowań.

Podstawowy system DDS opisany powyżej jest bardzo praktyczny i posiada wysoką rozdzielczość. Częstotliwość można przestrajać natychmiastowo bez nieciągłości fazy, zmieniając po prostu zawartość rejestru M. Jednakże prawdziwe systemy DDS wymagają najpierw wykonania szeregowej procedury ładowania bitów, by umieścić nową częstotliwość w wewnętrznym buforze, który poprzedza równoległy rejestr M. Ma to na celu minimalizację ilości wyprowadzeń w obudowie. Kiedy nowe słowo zostanie załadowane do rejestru bufora, rejestr zmiany fazy o równoległym wyjściu oczekuje na takt zegara, tym samym zmieniając wszystkie bity równocześnie. Liczba cykli zegara potrzebnych, by załadować bufor zmiany fazy określa maksymalną szybkość, z jaką częstotliwość wyjściowa może być przestrajana.

Aliasing w systemach DDS

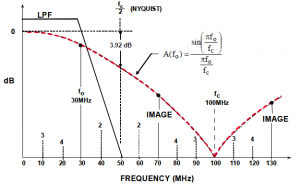

Istnieje jedno poważne ograniczenie zakresu częstotliwości wyjściowych, które mogą być generowane przez prosty system DDS. Twierdzenie Nyquista mówi, że taktowanie zegara (częstotliwość próbkowania) musi być przynajmniej dwukrotnie wyższe od częstotliwości wyjściowej. W praktyce ograniczeniem jest wartość generowanej częstotliwości równa około 1/3 częstotliwości zegara. Rysunek 5 przedstawia wyjście przetwornika w systemie DDS, w którym częstotliwość wyjściowa wynosi 30 MHz, a częstotliwość zegara – 100 MHz. Filtr antyaliasingowy musi być umieszczony za przetwornikiem, by usunąć niższą częstotliwość lustrzaną (100 – 30 = 70 MHz).

Rys. 5. Aliasing w systemie DDS

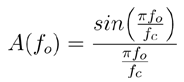

Amplituda odpowiedzi przetwornika cyfrowo-analogowego przed filtracją odpowiada przebiegowi sin(x)/x z zerami na częstotliwości zegara i jej wielokrotnościach. Dokładne równanie określające znormalizowaną amplitudę wyjściową A(fo) jest następujące:

Gdzie fo jest częstotliwością wyjściową, a fc to częstotliwość zegara.

Spadek przebiegu występuje, ponieważ wyjście przetwornika nie jest serią impulsów o zerowej szerokości (jak w idealnym przypadku), lecz stanowi ciąg impulsów prostokątnych, których szerokość jest równa odwrotności częstotliwości odświeżania. Amplituda sin(x)/x spada o 3,92 dB na częstotliwości Nyquista (? częstotliwości odświeżania DAC). W praktyce transmitancja filtru antyaliasingowego może zostać wykorzystana do kompensacji spadku sin(x)/x do tego stopnia, iż ostateczna odpowiedź częstotliwościowa jest względnie płaska aż do maksymalnej częstotliwości wyjściowej przetwornika (zazwyczaj 1/3 częstotliwości odświeżania).

Innym ważnym zagadnieniem jest fakt, iż w przeciwieństwie do systemów opartych o pętlę PLL, harmoniczne częstotliwości podstawowej w systemie DDS znajdą się w paśmie podstawowym na skutek aliasingu. Te harmoniczne nie mogą zostać usunięte przez filtr antyaliasingowy. Dla przykładu, jeśli częstotliwość zegara wynosi 100 MHz, a częstotliwość wyjściowa – 30 MHz, druga harmoniczna sygnału wyjściowego 30 MHz jest równa 60 MHz (poza pasmem), ale również 100 – 60 = 40 MHz (składnik wnoszony przez aliasing). Podobnie, trzecia harmoniczna (90 MHz) znajdzie się w paśmie na 100 – 90 = 10 MHz, a czwarta na 120 – 100 = 20 MHz. Harmoniczne wyższych rzędów również znajdą się w zakresie pasma Nyquista (od 0 do fc/2).

Systemy DDS jako kontrolery zegara przetworników analogowo-cyfrowych (ADC)

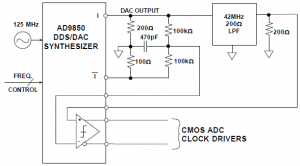

Układy DDS, jak na przykład AD9850 firmy Texas Instruments, stanowią doskonałą metodę generacji zegara taktującego przetwornik ADC, zwłaszcza, gdy częstotliwość próbkowania ADC musi być kontrolowana przez program i zsynchronizowana z zegarem systemowym (rysunek 6).

Rys. 6. Wykorzystanie systemu DDS do sterowania zegara przetworników

Prąd wyjściowy przetwornika zasila filtr dolnoprzepustowy 200 ? / 42 MHz, którego zasilanie i obciążenie jest zakończone terminatorem, tworząc równoważne obciążenie 100 ?. Filtr usuwa niepożądane częstotliwości składowe powyżej 42 MHz. Odfiltrowany sygnał zasila wejście wewnętrznego komparatora AD9850. Komplementarny prąd wyjściowy przetwornika zasila obciążenie 100 ?. Wyjście dzielnika 100 k? umieszczone pomiędzy dwoma wyjściami prądowymi jest odsprzężone i tworzy napięcie odniesienia dla wewnętrznego komparatora.

Wyjście komparatora ma czas narastania i opadania równy 2 ns i generuje przebieg prostokątny kompatybilny z TTL/CMOS. Błąd średniokwadratowy zegara między wyjściami komparatora wynosi mniej, niż 20 ps. W razie potrzeby dostępne jest wyjście bezpośrednie i zanegowane.

W schemacie pokazanym na rysunku 6 całkowity błąd średniokwadratoy zegara przetwornika o wydajności 40 milionów próbek na sekundę (MSPS) wynosi 50 ps, a spowodowane tym pogorszenie stosunku sygnał-szum musi być uwzględnione w zastosowaniach wymagających dużego zakresu dynamicznego.

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii