Podstawy bezpośredniej syntezy cyfrowej (DDS)

Modulacja amplitudy w systemie DDS

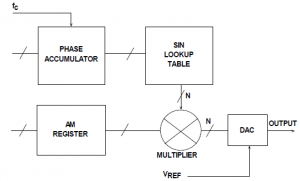

Modulację amplitudy w systemie DDS można uzyskać poprzez umieszczenie cyfrowego układu mnożącego pomiędzy tablicą wartości a wejściem przetwornika, jak pokazano na rysunku 7. Inną metodą modulacji amplitudy wyjściowej przetwornika jest zmiana jego napięcia referencyjnego. W przypadku układu AD9850, pasmo wewnętrznego interfejsu kontrolnego wzmacniacza wynosi około 1 MHz. Ta metoda jest użyteczna dla raczej niewielkich zmian amplitudy wyjściowej, dopóki wartość sygnału nie przekracza zalecanej wartości 1 V.

Rys. 7. Modulacja amplitudy w systemie DDS

Ograniczenia zakresu dynamicznego w systemach DDS

W wielu zastosowaniach czystość widma na wyjściu przetwornika jest podstawowym problemem. Niestety, pomiary, przewidywanie i analiza jego zachowania są utrudnione przez szereg współzależnych czynników.

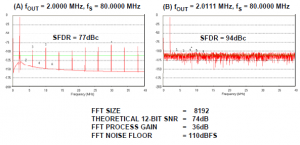

Nawet idealny N-bitowy przetwornik wprowadza harmoniczne do systemu DDS. Amplituda tych harmonicznych ściśle zależy od stosunku częstotliwości wyjściowej do częstotliwości zegara. Dzieje się tak, gdyż zawartość harmonicznych w szumie kwantyzacji DAC zmienia się wraz ze zmianą tego stosunku, nawet jeśli teoretyczna wartość błędu średniokwadratowego wynosi q/?12 (gdzie q jest wagą najmniej znaczącego bitu). Założenie, że szum kwantyzacji pojawia się w postaci szumu białego i jest rozproszony równomiernie w paśmie Nyquista jest nieprawdziwe w systemie DDS (jest bliższe prawdy w systemie opartym o przetwornik analogowo-cyfrowy (ADC), ponieważ przetwornik ten wnosi pewną ilość szumów do sygnału, który „rozmywa” lub wprowadza losowy błąd kwantyzacji. Jednak wciąż istnieje tu pewna korelacja). Na przykład, jeśli częstotliwość wyjściowa DAC stanowi dokładną podwielokrotność częstotliwości zegara, szum kwantyzacji będzie skoncentrowany wokół wielokrotności częstotliwości wyjściowej, a zatem jest silnie zależny od sygnału. Jeśli generowana częstotliwość jest nieco przesunięta, szum kwantyzacji będzie bardziej losowy, tym samym zwiększając efektywny zakres SFDR. Jest to zilustrowane na rysunku 8, gdzie 4096-punktowa FFT jest obliczona w oparciu o cyfrowo wygenerowane dane z idealnego 12-bitowego przetwornika DAC.

Rys. 8. Wpływ stosunku częstotliwości zegara do sygnału na SFDR teoretycznego 12-bitowego DAC przy zastosowaniu 4096-punktowej transformaty Fouriera.

Na lewym diagramie (A) stosunek częstotliwości zegara do częstotliwości wyjściowej został ustalony na 40, prowadząc do SFRD około 77 dBc. Na prawym diagramie stosunek ten został nieco zmieniony, a efektywne SFDR wzrosło do 94 dBc. W tym wyidealizowanym przykładzie zaobserwowano polepszenie SFDR o 17 dB dzięki niewielkiej zmianie stosunku częstotliwości.

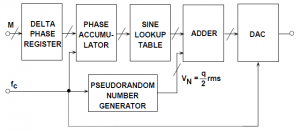

Najlepszy SFDR można otrzymać zatem poprzez uważny dobór częstotliwości zegara i sygnału. Jednakże w niektórych zastosowaniach może to nie być możliwe. W systemach opartych na przetwornikach ADC dodanie niewielkiego szumu na wejściu prowadzi do losowych błędów kwantyzacji i redukuje ten efekt. To samo można zastosować w systemie DDS pokazanym na rysunku 9.

Rys. 9. Dodanie cyfrowego ditheringu do systemu DDS w celu randomizacji szumu kwantyzacji i zwiększenia SFDR

Pseudolosowy szum cyfrowy z wyjścia generatora jest dodawany do amplitudy sinusoidy otrzymanej z DDS przed podaniem na DAC. Amplituda szumu cyfrowego została ustalona na poziomie około ? wartości najmniej znaczącego bitu. Jest to proces randomizacji uzyskany kosztem minimalnego zwiększenia poziomu szumu. Jednak w większości zastosowań DDS istnieje wystarczająca swoboda w doborze stosunku częstotliwości, także dithering nie jest wymagany.

Przykładowe narzędzie projektowe systemów DDS

Dostępne w sieci narzędzie projektowe Analog Device ADIsimDDS jest interaktywną aplikacją pomagającą użytkownikowi w doborze i testowaniu zintegrowanych układów DDS. Pozwala ona użytkownikowi wybrać urządzenie, wprowadzić pożądane parametry pracy i ocenić ogólne zachowanie. Narzędzie to wykorzystuje wzory matematyczne do przybliżenia skuteczności wybranego układu i nie uwzględnia wszystkich możliwych błędów. Z tego powodu powinno być używane jedynie jako pomoc w projektowaniu i nie zostało przeznaczone jako zamiennik rzeczywistych testów i badań.

Opracowanie wykonane na podstawie noty aplikacyjnej Analog Devices MT-085: Fundamentals of Direct Digital Synthesis (DDS); Rev.0, 10/08.

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii