Implementacja protokołu PTP IEEE 1588 V2 na mikrokontrolerze Kinetis K60

Określanie czasu (timestamping)

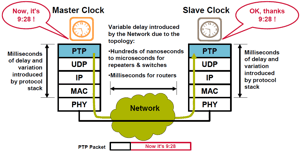

Protokół PTP może być zaimplementowany całkowicie programowo, korzystając ze standardowego modułu Ethernetu. Ponieważ jednak informacja o czasie jest dodawana na poziomie aplikacji, fluktuacje opóźnienia wnoszone przez stos programu uruchomionego jednocześnie na urządzeniu nadrzędnym i podrzędnym powodują, że można w ten sposób uzyskać tylko niewielką precyzję (rysunek 4).

Rys. 4. Implementacja określająca czas w programie

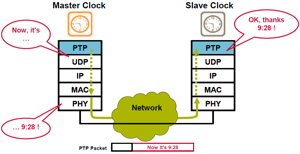

Możliwe jest zminimalizowanie wpływu opóźnienia stosu protokołów poprzez określanie czasu bliżej interfejsu fizycznego, w warstwie MAC lub fizycznej – PHY (rysunek 5). Dedykowane urządzenia zdolne do określania czasu, takie jak moduł peryferyjny MAC-NET zawarty w układzie Freescale Kinetis K60 pozwala na synchronizację ze znacznie wyższą precyzją.

Rys. 5. Implementacja określająca czas sprzętowo

Implementacja IEEE 1588 na Kinetis K60 z wykorzystaniem biblioteki MQX1588

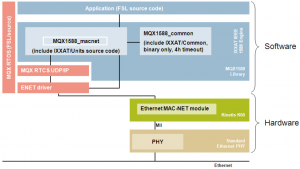

Zestaw TWR-K60N512-KIT z mikrokontrolerem Kinetis K60 stanowi platformę sprzętową dla implementacji protokołu PTP IEEE 1588. W połączeniu z biblioteką Freescale MQX1588 używającą stosu MQX TCP/IP i oprogramowaniem protokołu IEEE 1588 V2 od IXXAT Automation GmbH pozwala użytkownikom na projektowanie systemów IEEE 1588 o dużej dokładności. Rysunek 6 ilustruje elementy sprzętowe i programowe tego rozwiązania.

Rys. 6. Pakiet rozwiązań IEEE 1588 dla Kinetis K60

Składniki sprzętowe – modularny zestaw TWR-K60N512-KIT

Zestaw TWR-K60N512-KIT jest częścią modularnej platformy projektowej Freescale Tower System. Może również pracować jako samodzielna, niedroga platforma testowa dla mikrokontrolerów Kinetis. Na wyposażeniu TWR-K60N512-KIT znajduje się oparty na rdzeniu ARM Cortex-M4 mikrokontroler Kinetis K60 o niskim poborze mocy.

TWR-K60N512-KIT zawiera:

- Moduł z mikrokontrolerem K60: TWR-K60N512

- Moduł szeregowy obsługujący USB (host/device/OTG), Ethernet, CAN, RS232 oraz RS485: TWR-SER

- Moduł łączący: TWR-ELEV

Moduł TWR-K60N512 z mikrokontrolerem K60 zawiera:

- Mikrokontroler K60: model K60N512VMD100 w obudowie MAPBGA z 144 wyprowadzeniami,

- Pojemnościowe panele dotykowe

- Zintegrowany interfejs JTAG

- Gniado na kartę pamięci SD

- Trójosiowy akcelerometr MMA7660

- Gniazdo rozszerzeń TWRPI (Tower Plugi-In) przeznaczone m.in. dla czujników

- Łączność modułu umożliwiająca dostęp do USB, Ethernetu, RS232/RS485, CAN, SPI, I2C, Flexbus i innych

- Potencjometr, cztery diody LED, dwa przyciski i port podczerwieni

Więcej informacji o TWR-K60N512-KIT można uzyskać w podręczniku użytkownika TWR-K60N512 Tower User’s Manual lub na stronie internetowej platformy Tower System.

Składniki sprzętowe – 32-bitowy mikrokontroler Kinetis K60

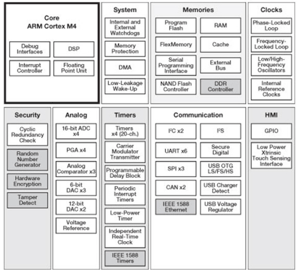

Kinetis stanowi najbardziej zróżnicowaną rodzinę mikrokontrolerów o niskim poborze mocy i z rdzeniem ARM Cortex-M4 dostępną na rynku. Pierwsza część tej serii składa się z pięciu rodzin mikrokontrolerów z ponad 200 układami kompatybilnymi ze sobą pod względem wyprowadzeń, peryferii i oprogramowania. Każda z rodzin oferuje doskonałą wydajność, pojemną pamięć i skalowalność funkcjonalności dzięki wspólnym peryferiom i mapom pamięci, umożliwiając łatwą migrację między układami zarówno w obrębie rodziny, jak i pomiędzy nimi.

Wśród zasobów mikrokontrolerów z rodziny K60 znajduje się między innymi interfejs Ethernet IEEE 1588, USB 2.0 On-The-Go (Full Speed i High Speed) i sprzętowy moduł szyfrujący. Mikrokontrolery wyposażone są w pamięć Flash (od 256 kB dla układów w obudowach 100LQFP do 1MB dla układów w obudowach 256MAPBGA), bogaty zestaw zasobów analogowych, interfejsów komunikacyjnych, liczników i innych zasobów. Dodatkowo wybrane układy zawierają opcjonalną jednostkę arytmetyki zmiennoprzeciwnkowej pojedynczej precyzji oraz kontroler pamięci NAND Flash i DRAM.

Na rysunku 7 przedstawiono schemat wewnętrzny rodziny mikrokontrolerów Kinetis K60. Więcej informacji można odnaleźć w podręczniku użytkownika K60 Sub-Family Reference Manual, K60P104M100SF2RM.

Rys. 7. Schemat blokowy mikrokontrolerów Kinetis K60

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485