STMicroelectronics STEF05: elektroniczny ogranicznik prądu z zabezpieczeniem przeciwprzepięciowym

Na rysunku 2 pokazano wykres sekwencji napięć w czasie normalnej pracy, sygnalizacji przegrzania, zerowania i powrotu do normalnej pracy po usunięciu przyczyny przegrzania.

W związku ze sposobem pracy wyprowadzenia ENABLE/FAULT powinno być ono łączone z zewnętrznymi układami typu otwarty kolektor/dren.

Rys. 3. Schemat elektryczny zestawu testowego

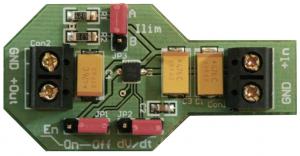

Fot. 4. Wygląd zmontowanej płytki testowej z układem STEF05

Na rysunku 3 przedstawiono schemat elektryczny zestawu zaprojektowanego do testowania układu STEF05. Wejściowe napięcie zasilające należy podać na złącze Con1 natomiast obciążenie dołącza się do złącza Con2. Ustawienie zwory JP1 w pozycji 1-2 zewrze wejście ENABLE/FAULT do masy i trwale wyłączy STEF05. Ustawienie zwory JP2 w pozycji 1-2 dołącza zewnętrzny kondensator wydłużając po włączeniu zasilania czas narastania napięcia na wyjściu. Zwora JP3 służy do ustawienia ograniczenia prądu wyjściowego. W pozycji 1-2 prąd będzie ograniczony do ok. 2 A a w pozycji 2-3 do wartości 1 A. W przypadku samodzielnego projektowania płytki drukowanej z wykorzystaniem układu STEF05 należy pamiętać, że napięcie Vcc podawane na wyprowadzenie ulokowane pod spodem obudowy układu scalonego.

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii