Sygnały zegarowe w STM32F1 Connectivity Line

Wraz z pojawieniem się na rynku mikrokontrolerów STM32 należących do komunikacyjnego segmentu Connectivity Line, pojawiło się wiele pytań o poprawną konfigurację sygnałów zegarowych. W odpowiedzi na te pytania publikujemy artykuł ukazujący sposób konfiguracji zaawansowanego systemu kontroli sygnałów zegarowych w układach STM32F107.

Każdy synchroniczny system cyfrowy, a do takich z pewnością należą układy mikroprocesorowe, wymaga do poprawnej pracy odpowiednich sygnałów zegarowych. W najprostszym przypadku cały system jest taktowany z jednego źródła tą samą częstotliwością.

Wraz ze wzrostem poziomu skomplikowania, a co ważniejsze, ze wzrostem skali integracji, istnieje potrzeba generowania w układach mikroprocesorowych sygnałów zegarowych o różnych częstotliwościach, determinowanych przez rodzaj stosowanych układów peryferyjnych.

Mikrokontrolery STM32 należące od rodziny connectivity line są wyposażone w imponującą liczbę peryferiów komunikacyjnych, m. in. Ethernet MAC (opcjonalnie), USB OTG, I2S. Na rys. 1 przedstawiono schemat blokowy obrazujący mnogość dostępnych peryferiów układów connectivity line. Tak duża liczba elementów o różnorodnym przeznaczeniu sprawia ,że konieczne staje się generowania jednocześnie wielu przebiegów zegarowych, o różnych częstotliwościach. W artykule przedstawiona została konfiguracja sygnałów zegarowych dla aplikacji korzystającej z USB i Ethernet.

Rys. 1. Wyposażenie segmentu connectivity line [źródło: STMicroelectronics]

Układy warstwy fizycznej PHY Ethernet wymagają zazwyczaj taktowania częstotliwością 25MHz, w przypadku stosowania interfejsu MII (Media Independence Interface), lub 50MHz, jeżeli wykorzystano interfejs RMII (Reduced MII). Najczęściej mikrokontrolery z wbudowanym sterownikiem Ethernet wymagają pracy z zewnętrznym źródłem sygnału zegarowego (np. rezonator kwarcowy) o częstotliwości 25 MHz. Konstruktorzy, którzy zdecydowali się na stosowanie układu z rodziny STM32 nie są jednak skazani na stosowanie w swoich aplikacjach ethernetowych „kwarców” tylko o tej częstotliwości. Jak pokażemy w dalszej części artykułu, architektura mikrokontrolerów firmy STMicroelectronics pozwala na odstępstwa od tej reguły.

Kontroler magistrali USB do poprawnej pracy wymaga taktowania z częstotliwością 48MHz. Jeśli tylko aplikacja nie ma zbyt dużych wymagań i nie korzysta z urządzeń peryferyjnych wymagających specyficznych częstotliwości pracy, to wtedy można cały system mikroprocesorowy taktować zegarem 48 MHz. A co, jeśli owe 48 MHz to za mało dla naszej aplikacji? W takim przypadku na ratunek przychodzi możliwość taktowania rdzenia mikrokontrolera z innego źródła sygnału zegarowego.

Taktowanie w STM32

Mikrokontrolery STM32F107, czyli należące do szerszej rodziny connectiviy line, mają wbudowane aż trzy układy PLL, które umożliwiają mnożenie wejściowego sygnału przez wiele współczynników. Do dyspozycji są również dwa układy wstępnego dzielenia sygnału oraz liczne multipleksery sygnałów zegarowych. Budowa bloku kontroli zegarów została przedstawiona na rysunku poniżej.

Rys. 2. Schemat RCC (Reset and Clock Control) [źródło: STMicroelectronics]

Mikrokontrolery connectivity line mogą pracować z rezonatorami o częstotliwościach z przedziału od 3 MHz do 25 MHz. Dokumentacje dostarczane przez firmę ST podają, że celem rozszerzenia górnej granicy do 25 MHz było osiągnięci możliwości pracy wszystkich interfejsów komunikacyjnych po podłączeniu tylko jednego źródła sygnału zegarowego. Pokażemy, że niezwykła elastyczność układu taktowania tej podrodziny mikrokontrolerów STM32 pozwala na wykorzystanie również rezonatorów o innych częstotliwościach. Przedstawiona zostanie konfiguracja dla rezonatora 10 MHz z przeznaczeniem dla aplikacji z obsługą Ethernet i USB.

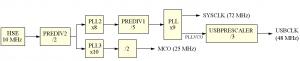

Obsługa obu interfejsów: Ethernet i USB wymaga uzyskania dwóch różnych sygnałów zegarowych, odpowiednio 25 MHz i 48 MHz. Jeśli mikrokontroler STM32 ma dodatkowo wykorzystywać pełnię swoich możliwości, to należy odpowiednio skonfigurować sygnał zegarowy dla rdzenia mikrokontrolera, tak by uzyskał on 72 MHz. Na rys. 3 przedstawiono konfigurację dla poszczególnych bloków, tak by każdy z peryferiów pracował z optymalną częstotliwością. Jak widać droga do zamierzonego celu wydaje się dość kręta, jednak jak zaraz przekonamy się, nie jest aż tak źle.

Rys. 3. Konfiguracja sygnałów zegarowych dla rdzenia, USB i Ethernet, przy oscylatorze 10MHz

Wszystkie czynności związane z konfiguracją sygnałów zegarowych mogą zostać zgrupowane do postaci jednej funkcji. W przedstawianym przykładzie funkcję nazwano RCC_Configuration(), listing funkcji zamieszczono poniżej.

![Rys. 1. Wyposażenie segmentu connectivity line [źródło: STMicroelectronics]](/wp-content/uploads/artykuly/Sygnaly_zegarowe_w_STM32F1_Connectivity_Line/Rys.%201.do_artykulow.jpg)

![Rys. 2. Schemat RCC (Reset and Clock Control) [źródło: STMicroelectronics]](/wp-content/uploads/artykuly/Sygnaly_zegarowe_w_STM32F1_Connectivity_Line/Rys.2%20_small.do_artykulow.jpg)

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii  Firma Nordic Semiconductor wprowadza adaptacyjne monitorowanie stanu baterii dla urządzeń IoT

Firma Nordic Semiconductor wprowadza adaptacyjne monitorowanie stanu baterii dla urządzeń IoT