Mikrokontrolery z Cortex-M3 w ofercie Analog Devices – przegląd oferty

Sukces mikrokontrolerów ADuCM360/361 zachęcił firmę Analog Devices do wdrożenia kolejnych mikrokontrolerów wyspecjalizowanych w aplikacjach analogowych, które także wyposażono w rdzenie Cortex-M3. Omówimy je osobno, ponieważ są one konstrukcyjnie i pod względem wyposażenia zorientowane na różne obszary aplikacyjne.

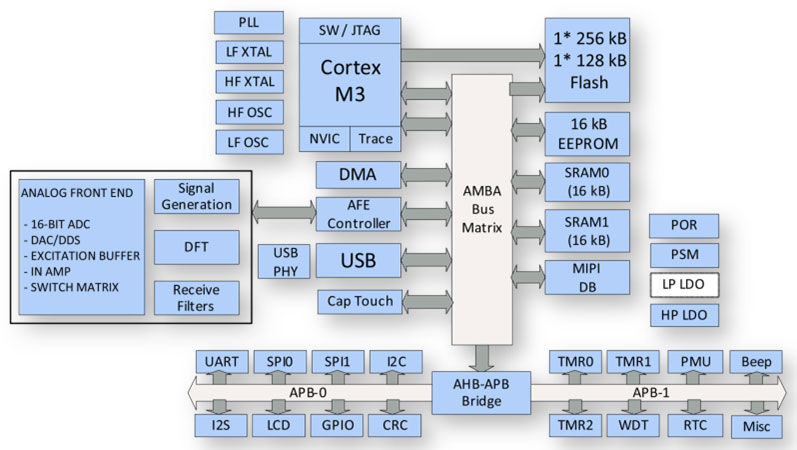

Zaczniemy od mikrokontrolera ADuCM350 (schemat blokowy pokazano na rysunku 4), który został przez producenta pomyślany jako jednoukładowy, zintegrowany system pomiarowy z dużymi możliwościami obróbki sygnałów. Ze względu na ukierunkowanie na realizację zaawansowanych algorytmów obliczeniowych, mikrokontrolery ADuCM350 wyposażono w pamięć Flash o pojemności 384 kB, SRAM ma pojemność 32 kB, dodatkowo użytkownik ma do dyspozycji 16 kB pamięci EEPROM (emulowanej w wydzielonym obszarze Flash). Rdzeń tego mikrokontrolera może być taktowany z częstotliwością do 16 MHz, co pozwala uzyskać prędkość wykonywania programu ok. 20 MIPS.

Rys. 4. Schemat blokowy mikrokontrolera ADuCM350

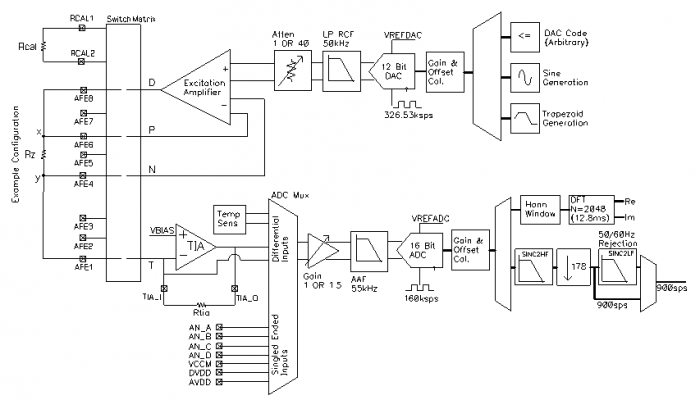

Najważniejszą siłą mikrokontrolerów ADuCM350 są wbudowane w nie interfejsy analogowe, które zgrupowano w bloku AFE (jego schemat blokowy pokazano na rysunku 5). W torze wejściowym zastosowano m.in. wzmacniacz transimpedancyjny, analogowy filtr dolnoprzepustowy i multiplekser analogowy, sygnał przetworzony w 16-bitowym przetworniku ADC może być poddawany sprzętowej obróbce za pomocą wyspecjalizowanych bloków cyfrowych, wśród których warto zwrócić uwagę na blok pomiaru impedancji (obliczający zarówno jej moduł jak i fazę) oraz blok programowany filtracji pasmowoprzepustowej z decymatorem.

Rys. 5. Schemat blokowy AFE – zespolonego toru ADC/DAC

Głównym elementem toru wyjściowego AFE jest 12-bitowy przetwornik DAC, który może być sterowany z syntezera DDS o konfigurowanych parametrach lub za pośrednictwem rejestru, do którego CPU może wpisywać dowolne dane, co zapewnia mikrokontrolerowi funkcjonalność generatora arbitralnego. Na wyjściu przetwornika zastosowano filtr dolnoprzepustowy oraz wzmacniacz-bufor o programowanym wzmocnieniu.

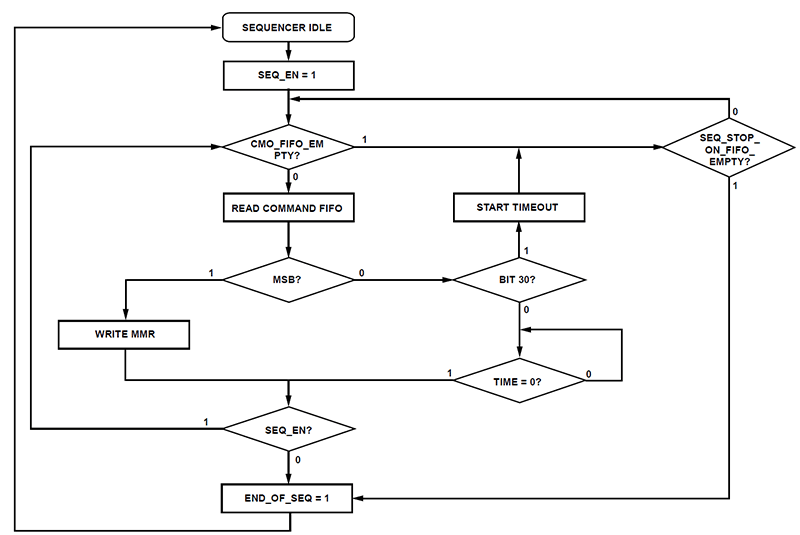

Sygnały analogowe są krosowane za pomocą wejściowej matrycy połączeniowej. Projektanci mikrokontrolera ADuCM350, chcąc odciążyć CPU od bieżącej obsługi jego pracy MMR, blok AFE wyposażyli w programowalny sekwencer, którego poszczególne kroki są zapisywane w pamięci FIFO. Algorytm działania sekwencera pokazano na rysunku 6.

Rys. 6. Algorytm działania sekwencera autonomicznie zarządzającego pracą AFE

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii  Mieszacze aktywne – ćwiczenie z serii ADALM

Mieszacze aktywne – ćwiczenie z serii ADALM