Opanuj jitter: pętle PLL nowej generacji

Z tego powodu warto zastosować inne metody, które pozwalają uchronić sygnały wysokich szybkości od zniekształceń. Jednym z rozwiązań jest pętla fazowa (PLL) – układ kontrolujący częstotliwość, który pozwalający zmniejszyć jitter. Dyskretne układy PLL są powszechnie stosowane, aby zapewnić niezaburzony sygnał zegarowy w systemach wysokiej szybkości. Istotne jest jednak, aby pętli PLL używać w prawidłowy sposób. W szczególności należy zoptymalizować jej pasmo.

|

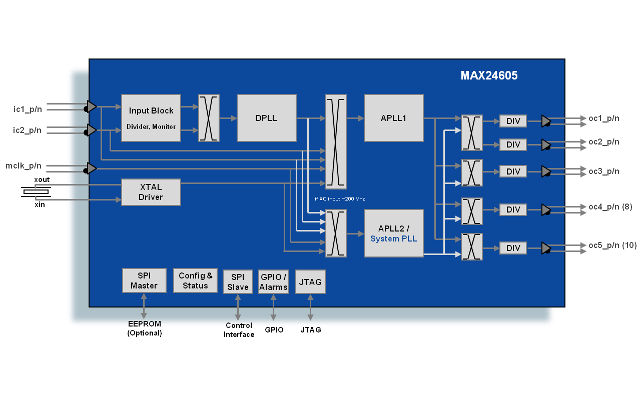

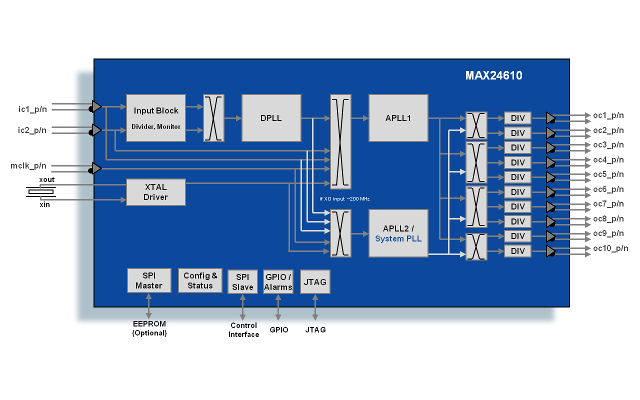

Schematy blokowe scalonych pętli PLL z tłumikami jittera z oferty firmy Microsemi:

MAX24605

MAX24610 |

Jitter na wyjściu PLL zależy od dwóch czynników: szumu sygnału wejściowego i szumu oscylatora sterowanego napięciem (VCO). Pierwszy z nich to suma jittera cechującego źródło sygnału zegarowego oraz szumu PCB i zasilania. Drugi zależy od pasma PLL i musi zostać odpowiednio dobrany, aby zminimalizować całkowity wpływ szumów VCO i sygnału wejściowego. Decyzja o zmniejszeniu pasma pętli PLL zależy zatem od konkretnego systemu.

Prowadzi to do ważnego problemu: czy należy użyć zewnętrznego VCO, czy układu PLL z wbudowanym VCO? Zewnętrzny VCO pozwala projektantowi na wybór dowolnego układu o najbardziej pożądanych cechach. Jednak taki układ będzie bardziej wrażliwy na zakłócenia wnoszone przez płytkę, takie jak sprzężenie magnetyczne i wpływ zasilacza oraz szum generowany przez elementy takie, jak dyskretny filtr pętli.

Z drugiej strony pętla PLL z wbudowanym VCO i zewnętrznym filtrem wrażliwym na zakłócenia może powodować wystąpienie niedokładności. Wybór jednej z opcji zależy od konkretnego przypadku.

Mimo to użycie wysokiej klasy układu PLL pozwala zmniejszyć znacząco wpływ jittera na sygnały zegarowe wysokich szybkości. Przykładowo, seria modułów PLL z oscylatorami kryształowymi PureEdge firmy ON Semiconductor jest przeznaczona do pracy z sygnałami zegarowymi LVPECL/LVDS/CML i napięciem 2,5 lub 3,3 V. The moduły cechują się typowym szumem fazowym 0,4 – 0,5 ps (wartość średniokwadratowa), co jest wystarczające do większości zastosowań telekomunikacyjnych, sieciowych, centrów obliczeniowych i centrów danych. Układy z serii PureEdge są stosowane w urządzeniach korzystających z technologii takich, jak SONET/SDH, Ethernet 10 Gb/s, LAN, Fiber Channel, PCIe, DIMM, SAS/SATA oraz w układach FPGA.

Możliwa jest dalsza redukcja jittera poprzez kaskadowe połączenie układów PLL. Technika ta jest skuteczna, ponieważ pozwala projektantowi na optymalizację pasma każdej z pętli PLL osobno. Dzięki niej da się osiągnąć jitter na poziomie setek femtosekund.

Kaskadowe połączenie PLL można zrealizować z oscylatorem kryształowym lub zewnętrznym oscylatorem na wejściu. Układy tego typu zazwyczaj mają do 10 wyjść, co pozwala użytkownikowi utworzenie kompletnego systemu zegarowego.

Interesującymi przykładami układów tego typu są MAX24605 oraz MAX24610 stworzone przez Microsemi. Zawierają one cyfrową pętlę PLL i mogą generować częstotliwość wyjściową do 750 MHz.

Konfiguracje usuwające jitter stosują jednocześnie analogowe i cyfrowe układy PLL. Zaletą cyfrowej pętli PLL jest możliwość programowania pasma w zakresie od 4 Hz do 400 Hz, a cyfrowo sterowany oscylator pozwala na kontrolę częstotliwości za jej pomocą. Obecność dwóch analogowych pętli PLL w tym samym układzie pozwala na uzyskanie dwóch zbiorów częstotliwości z jednego zegara lub z dwóch różnych zegarów referencyjnych. Układy MAX24605 oraz MAX24610 zawierają interfejsy szeregowe i wbudowaną pamięć EEPROM, która pozwala na automatyczną konfigurację po włączeniu zasilania.

Wykorzystanie tego typu układów redukujących jitter pozwala projektantowi zrealizować układ zegarowy z jitterem jedynie 300 fs. W artykule zostały przedstawione różne sposoby zwalczania jittera w zależności od istniejących wymagań i ograniczeń. W niektórych przypadkach dedykowany układ zmniejszający jitter może nie być w ogóle potrzebny, ponieważ dobry projekt płytki wystarczy, aby obniżyć jitter do akceptowalnego poziomu.

W zastosowaniach, w których konieczne jest użycie pętli PLL, projektant musi zwrócić uwagę na poprawny dobór pasma. W wyjątkowych przypadkach można uzyskać bardzo niski jitter, używając dedykowanych układów zmniejszających jitter łączonych kaskadowo.

Paweł Kaczyński, FE

Projekty inteligentnych sterowników przetwornic buck z tranzystorami GaN — część 1: Zagadnienia i pomiary

Projekty inteligentnych sterowników przetwornic buck z tranzystorami GaN — część 1: Zagadnienia i pomiary  Prof. Ryszard Tadeusiewicz: Sztuczna inteligencja wykorzystująca seks w komputerze

Prof. Ryszard Tadeusiewicz: Sztuczna inteligencja wykorzystująca seks w komputerze  Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)