[PROJEKT] Gra Pong na FPGA z zestawu Digilent Basys 3

W artykule pokażemy, że układy FPGA to nie „nuda” z przyszytą łatą dydaktyczności, ale również dobra zabawa. W artykule pokażemy jak uruchomić grę Pong na tanim zestawie startowym Basys 3 z nowoczesnym FPGA z rodziny Artix-7 firmy Xilinx…

Prezentowaną grę zaimplementowano na płytce deweloperskiej Basys 3, która jest wyposażona w układ FPGA z rodziny Artix-7. Szczegółowe informacje są dostępne na stronie producenta.

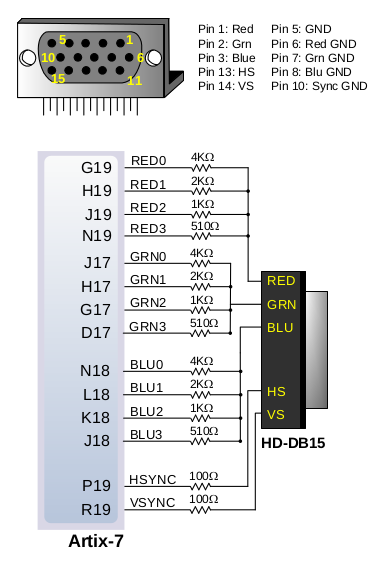

Standardem, jakiego będziemy używać do wyświetlania obrazów, będzie VGA. Jest to dość leciwy standard, ale za to ciągle używany i prosty w obsłudze. Płytka Basys 3 ma wyjście VGA sterowane 14-stoma sygnałami: po 4 na każdą z wartości RGB, oraz po jednym na synchronizację pionową i poziomą, co można zobaczyć na rysunku 1. Dokładny opis działania VGA na płytce Basys 3 znajdziecie w dokumentacji.

Rys. 1. Opis wyjścia VGA płytki Basys 3 (źródło: Basys3 Reference Manual)

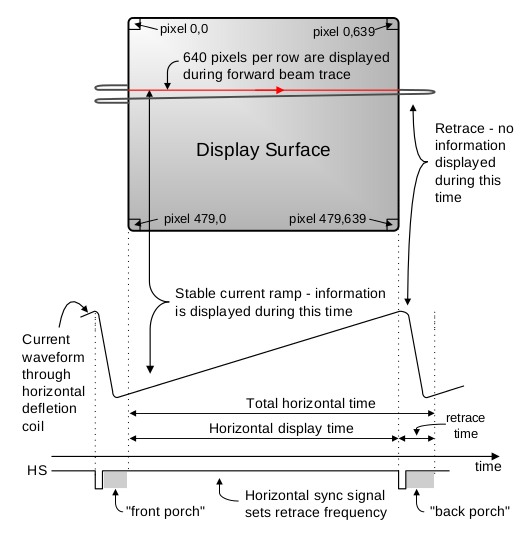

Łatwo obliczyć, że mając 12 bitów określających kolor, możemy wygenerować 4096 różnych kolorów – dla nas to w zupełności wystarczy. Interfejs VGA był zaprojektowany dla ekranów kineskopowych, które wykorzystywały działka elektronowe. W tylnej części kineskopu, w katodzie, emitowane były elektrony, które trafiały do dział elektronowych. Następnie skupiane były w wiązki i kierowane na ekran, aby podświetlić barwne punkty luminoforu. Za kierowanie wiązek w odpowiednie punkty odpowiedzialne były sygnały synchronizacji poziomej i pionowej. Zasadę działania ekranów kineskopowych dobrze ilustruje rysunek 2.

Rys. 2. Zasada działanie ekranów kineskopowych (źródło: http://m.ocdn.eu)

Nowoczesne monitory nie posiadają już ekranów kineskopowych, jednak nadal obsługują standard VGA. Generowanie obrazu odbywa się poprzez wyświetlanie rzędami kolejnych pikseli. Kiedy ostatni piksel zostanie wyświetlony, następuje powrót do pierwszego piksela w kolejnym rzędzie. Kiedy zostanie wyświetlony ostatni rząd, następuje powrót do rzędu pierwszego. Zasadę generowania obrazu dla rozdzielczości 640×480 przedstawiono na rysunku 3.

Rys. 3. Generowanie obrazu VGA (źródło: Basys3 Reference Manual)

Czasy powrotów do początkowych pikseli i rzędów nie są zerowe i różnią się w zależności od rozdzielczości obrazu, który chcemy wyświetlić. Parametry dla różnych rozdzielczości obrazu można bez trudu znaleźć w Internecie.

Pierwszą grą, jaką zaimplementujemy będzie klasyczny i prosty Pong, którego źródła znajdziemy na stronie: http://fpgacenter.com/examples/vga/index.php.

Gra ta została zaimplementowana w rozdzielczości 640×480 pikseli. Układem FPGA, na który została pierwotnie zaprojektowana był Cyclone III firmy Altera. Aby uruchomić Ponga na naszej płytce Basys 3 konieczne będzie wprowadzenie do projektu kilku zmian:

- Na wejście głównego modułu projektu musi być doprowadzony sygnał zegarowy 50 MHz. Ponieważ na naszej płytce mamy generator sygnału zegarowego 100 MHz, musimy częstotliwość tego sygnału obniżyć. Najprościej i najbezpieczniej będzie użyć gotowego IP core’a.

- W głównym module przy przypisaniu sygnałów do komponentu im_gen.vhd należy usunąć negację przy portach button_r i button_l.

- Na koniec wystarczy połączyć w nowo utworzonym przez nas pliku *.xdc odpowiednie porty z wyjściami układu FPGA.

Wszystkie pliki projektowe znajdziecie w materiałach załączonych do artykułu. Powyżej przedstawiamy filmik z demonstracją działającej gry.

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii