[3] Pierwsze kroki z FPGA – szkoła MAXimatora – testowanie funkcjonalne i weryfikacja działania projektu

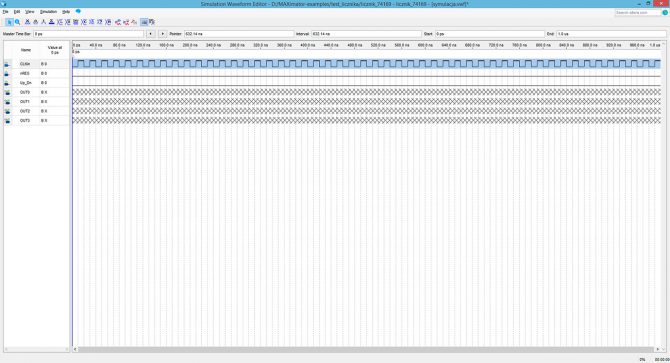

W pozycji Transitions Occur można zdefiniować odstępy czasowe pomiędzy zboczami sygnału zegarowego (dla wartości 10 ns okres przebiegu wynosi 20 ns).W wyniku opisanego ciągu operacji uzyskaliśmy przebieg jak pokazano na rysunku 12.

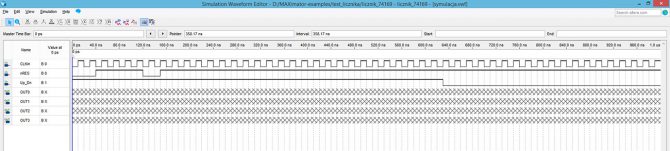

W podobny sposób postępujemy z pozostałymi sygnałami wejściowymi, na rysunku 13 pokazano przykładowe definicje przebiegów.

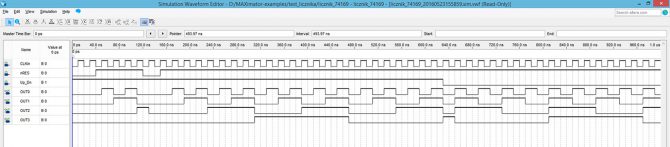

Symulator wbudowany w Quartus Prime umożliwia wykonanie dwóch rodzajów symulacji:

- funkcjonalnej, podczas której brane są pod uwagę wyłącznie zależności logiczne pomiędzy sygnałami, bez uwzględnienia wpływu czasów ich propagacji na działanie układu,

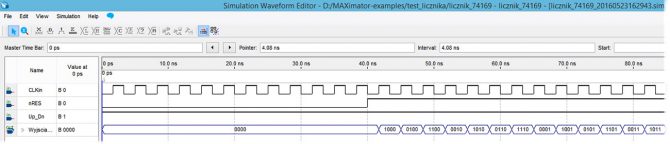

- czasowej, która jest bliższa realnym układom, bowiem oprócz zależności logicznych brane są pod uwagę także zależności czasowe pomiędzy sygnałami. Na rysunku 14 pokazano wynik symulacji funkcjonalnej weryfikowanego układu.

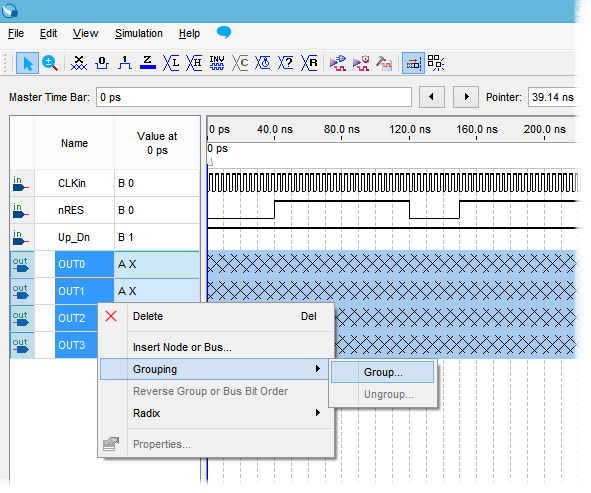

Edytor przebiegów wyposażono w kilka mechanizmów, które ułatwiają przygotowanie symulacji projektów o większej niż w przykładzie liczbie analizowanych wejść i wyjść.

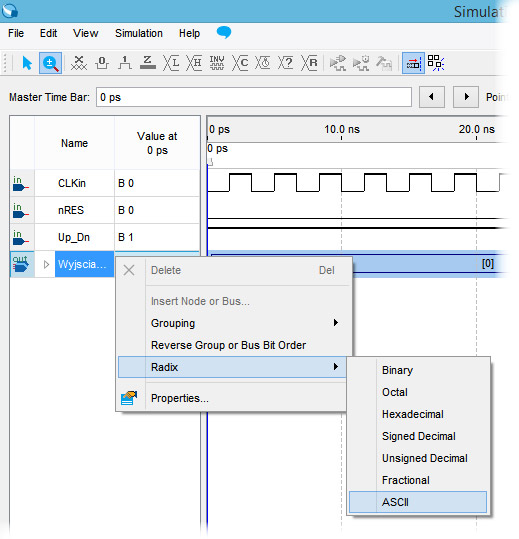

Można na przykład grupować wybrane linie w magistrale (rysunki 15 i 16), można także zmieniać format wyświetlanych wartości w zależności od indywidualnych potrzeb (rysunek 17).

W ten sposób przeszliśmy kompletną ścieżkę implementacji prostego projektu w FPGA. W kolejnej części skupimy się na pokazaniu zaawansowanych mechanizmów weryfikacji projektów implementowanych w FPGA, koncepcyjnie zbliżonych do debugowania programów uruchamianych na mikrokontrolerach.

Piotr Zbysiński

Prof. Ryszard Tadeusiewicz: Sztuczna inteligencja wykorzystująca seks w komputerze

Prof. Ryszard Tadeusiewicz: Sztuczna inteligencja wykorzystująca seks w komputerze  Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku