[4] Pierwsze kroki z FPGA – szkoła MAXimatora – monitorowanie pracy projektu z użyciem debugera SignalTAP II

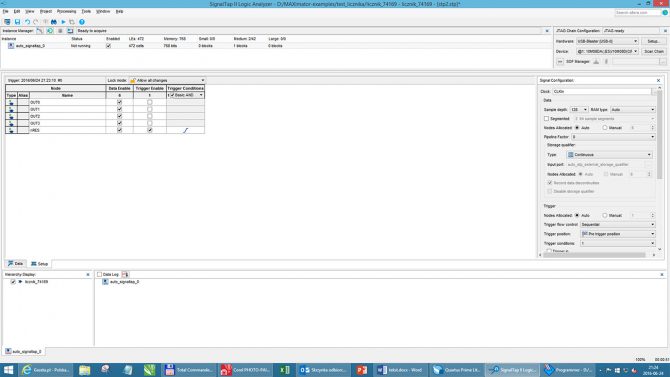

Ponieważ wejścia debugera SignalTAP II dołączyliśmy do wyjść i niektórych wejść monitorowanego licznika, w filtrze sygnałów (Options>Filter) wybieramy opcję Pins:all i następnie klikamy List. Wynik tej operacji pokazano na rysunku 12. Wybieramy z listy interesujące nas sygnały (w przykładzie OUT3…OUT0 oraz nRES, przy którym aktywujemy opcję Trigger Enable – rysunek 13) i klikamy Insert.

Po wykonaniu tych czynności ponownie kompilujemy cały projekt, do czego zachęca komunikat widoczny w belce Instance Manager, w górnej części okna pokazanego na rysunku 13. Po rekompilacji programujemy lub konfigurujemy docelowy układ FPGA, co jest oczywiste – musimy umieścić testowany projekt w FPGA, żeby móc go fizycznie monitorować.

Rys. 14. Wynik działania debugera – wyświetlone sygnały zostały pobrane we wnętrzu FPGA za pomocą SignalTAP II

Alternatywnym, wygodniejszym sposobem implementacji w projekcie umieszczanym w FPGA debugera SignalTAP, jest dodanie do projektu pliku *.stp (jak na rysunku 10) i wykonanie kolejnych czynności, łącznie z wybieraniem monitorowanych sygnałów z poziomu okna SignalTap II Logic Analyzer (jak na rysunku 13). W nowych wersjach Quartusa uruchomienie tego okna i zdefiniowanie listy sygnałów powoduje automatyczną implementację debugera w projekcie.

Piotr Zbysiński

Prof. Ryszard Tadeusiewicz: Sztuczna inteligencja wykorzystująca seks w komputerze

Prof. Ryszard Tadeusiewicz: Sztuczna inteligencja wykorzystująca seks w komputerze  Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku