Wytwarzanie układów CMOS 5 nm przy użyciu bloków z nanorurek

Publikacje z konferencji IEDM 2016 przedstawiają nowe rozwiązania problemów wydajności i redukcji pojemności pasożytniczych.

Leti, instytut wchodzący w skład CEA Tech, zademonstrował podczas konferencji IEDM 2016 wyniki badań nad możliwością stworzenia konkurencyjnych układów o wymiarze technologicznym 5 nm z wykorzystaniem nanorurek.

Architektura oparta na nanorurkach jest uważana za najbardziej obiecującą technologię. Leti rozwiązał największe problemy techniczne, takie jak uzyskanie odpowiedniej wydajności i ograniczenie pojemności pasożytniczych. Uzyskane wyniki sugerują, że w ułożonych jednej na drugiej nanorurek można wywołać naprężenia, zmniejszając pojemności pasożytnicze dzięki ciaśniejszemu upakowaniu.

W pracy „Vertically Stacked-Nanowires MOSFETs in a Replacement Metal Gate Process with

Inner Spacer and SiGe Source/Drain” znajduje się pierwsza demonstracja funkcjonalnych układów wykonanych z krzemogermanu. Wykonanie źródła oraz drenu z tego materiału pozwoliło wprowadzić naprężenia w kanale i zwiększyć wydajność układu, a wewnętrzna warstwa izolująca umożliwiła zmniejszenie pojemności pasożytniczej. Oba wymienione elementy są potrzebne do realizacji układu w procesie 5 nm. Architektura MOSFET pozwala oddalić ograniczenia skalowalności technologii CMOS i stanowi potencjalne rozszerzenie technologii FinFET.

Podczas konferencji IEDM w roku 2008 Leti był jedną z pierwszych organizacji, która ogłosiła sukces w pracach nad tworzeniem bloków nanorurek i nanowarstw.

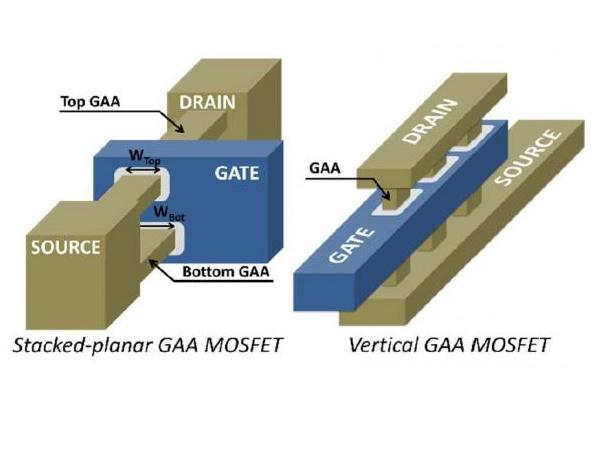

W drugiej pracy „NSP: Physical Compact Model for Stacked-planar and Vertical Gate-All-

Around MOSFETs” zostały zaprezentowane modele dla tranzystorów MOSFET wykonanych z nanorurek i nanowarstw – jest to kompaktowy, przewidywalny model fizyczny.

„Jest to pierwszy kompaktowy model (przeznaczony dla programu SPICE), który może symulować bloki nanorurek i nanowarstw o różnych geometriach.” – tłumaczy Oliver Faynot, kierownik ds. mikroelektroniki Leti i współautor obu publikacji. „Pozwala on również na symulację pionowej nanorurki, co stanowi jedną z największych zalet tego rozwiązania.”

Raport przedstawia fizyczny model SPICE dla nanorurek ułożonych w bloki, który pozwoli projektantom układów na dokładne przeniesienie istniejących projektów układów na proces technologiczny 5 nm i testowanie innowacyjnych rozwiązań.

Polska chce zwiększyć znaczenie sektora półprzewodników. Toczą się prace nad krajową polityką w tym obszarze

Polska chce zwiększyć znaczenie sektora półprzewodników. Toczą się prace nad krajową polityką w tym obszarze  Medicalgorithmics wesprze nowego partnera z Korei Południowej w ekspansji na rynku amerykańskim

Medicalgorithmics wesprze nowego partnera z Korei Południowej w ekspansji na rynku amerykańskim  PGZ i Frankenburg Technologies pogłębiają strategiczną współpracę w obszarze nowoczesnych systemów obronnych

PGZ i Frankenburg Technologies pogłębiają strategiczną współpracę w obszarze nowoczesnych systemów obronnych