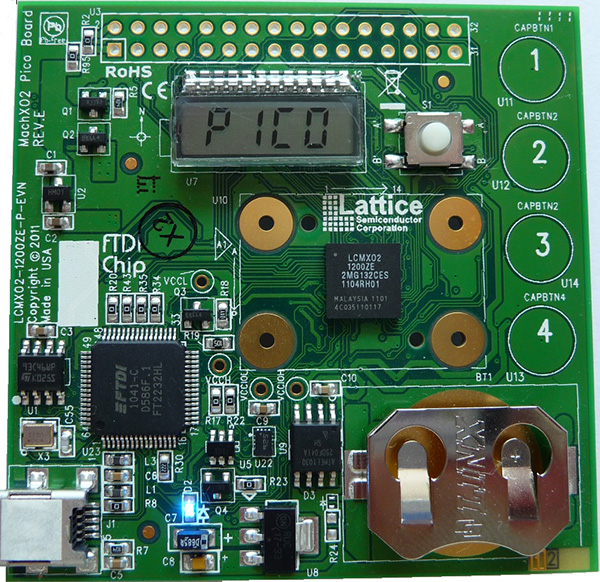

[PIERWSZY PROJEKT] Pierwsze kroki z zestawem FPGA Lattice MachXO2 Pico Development Kit [2]

Uwaga! Pierwsza część artykułu jest dostępna pod adresem.

Pokażemy teraz szczegółowo w jaki sposób rozpocząć projektowanie z zestawem MachXO2 Pico, wykorzystując środowisko Lattice Diamond. W naszych przykładowych projektach będziemy wykorzystywać język opisu sprzętu Verilog. Chociaż specyfikację projektowanego systemu można również, w znacznej części, wykonać stosując edytor schematów, jednak w przypadku np. użycia bloku funkcji wbudowanych EFB jest to praktycznie nieopłacalne. Tym bardziej, że aplikacja generatora wirtualnych komponentów IPexpress dla bloku EFB wytwarza kod stosując jeden z języków HDL: Verilog lub VHDL. Implementacja interfejsu WISHBONE, za pomocą którego odbywa się komunikacja z blokiem EFB, jest co prawda możliwa przy użyciu edytora schematów jednak znacznie prościej i szybciej można to zrobić wykorzystując język opisu sprzętu. Oczywiście w przypadku bardzo prostych układów cyfrowych można nadal posługiwać się edytorem schematu lub zastosować go do specyfikacji części większego projektu.

Na początku pokażemy bardzo prosty projekt, którego zadaniem będzie wytworzenie, na jednym z wyjść układu PLD, fali prostokątnej o częstotliwości około 1 Hz. Przebieg ten można wykorzystać do wysterowania diody LED, która po zaprogramowaniu układu PLD powinna cyklicznie zapalać się i gasnąć. Ponieważ w zestawie MachXO2 nie przewidziano diody LED ogólnego przeznaczenia, aby sprawdzić efekt działania naszego projektu potrzeba będzie taką diodę dołączyć do zewnętrznego złącza we/wy zestawu, lub zamiast LED zastosować np. sondę oscyloskopu.

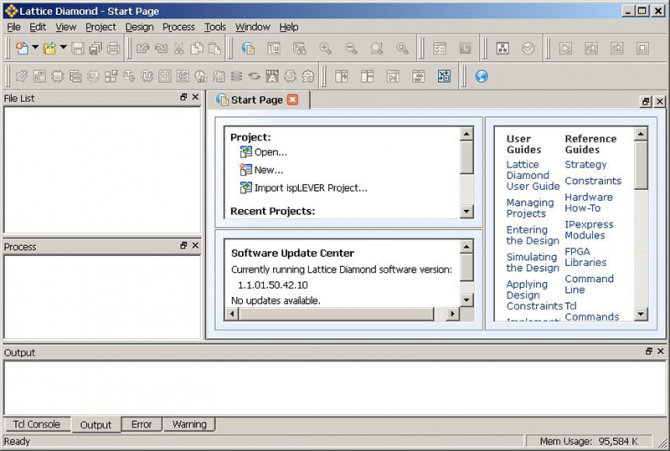

Rys. 11. Widok okna aplikacji Lattice Diamond po uruchomieniu

Na rysunku 11 pokazano wygląd głównego okna aplikacji Lattice Diamond tuż po uruchomieniu. Warto zauważyć, że z prawej strony okna zakładki Start Page dostępne są, w formacie PDF, instrukcje użytkownika dotyczące sposobu wykorzystania środowiska Lattice Diamod, opisy poszczególnych opcji itp.

Aby utworzyć nowy projekt należ z menu File wybrać opcję New a następnie Project lub w zakładce Start Page, poniżej etykiety Project, kliknąć opcję New. Otworzone zostanie okno kreatora nowego projektu, w którym, jako jeden z pierwszych kroków, będziemy musieli wybrać lokalizację dla plików naszego projektu oraz nazwę projektu.

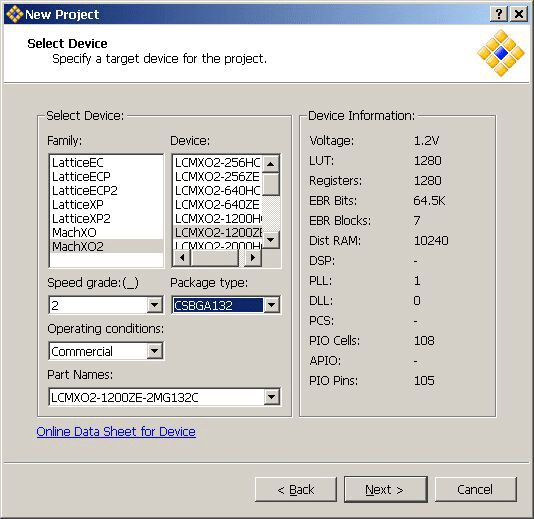

Rys. 12. Wybór docelowego układu programowalnego

Po wciśnięciu przycisku Next otrzymamy możliwość dodania istniejących plików źródłowych do naszego projektu. Jeżeli nie mamy takich plików i chcemy dopiero je utworzyć wybieramy opcję Next. Kolejnym – ostatnim krokiem jest wybór docelowego układu programowalnego. W przypadku zestawu MachXO2 Pico należy wybrać parametry pokazane na rysunku 12. Wygląd okna aplikacji Lattice Diamond, po utworzeniu projektu o nazwie „ Flashing_led” pokazano na rysunku 13.

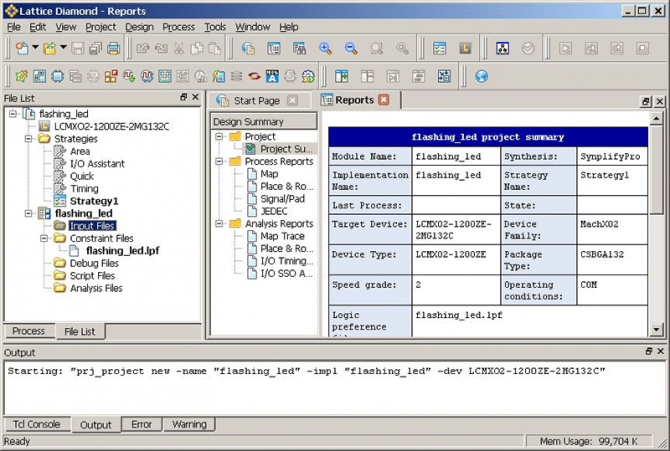

Rys. 13. Widok okna aplikacji Diamond po utworzeniu projektu

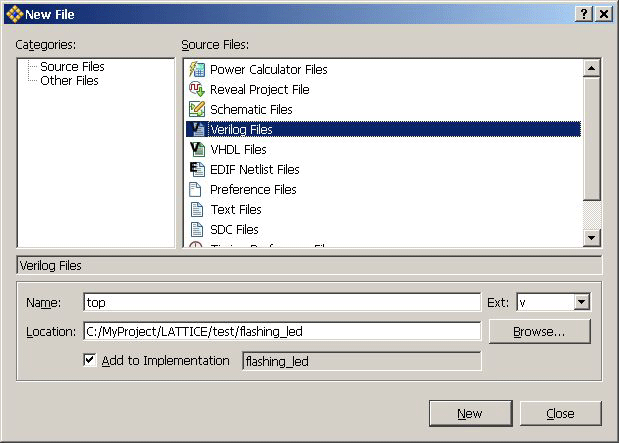

Teraz do projektu można dodawać pliki źródłowe. Można to zrobić klikając prawym klawiszem, zaznaczony na rysunku 13, folder Input Files i wybierając opcję Add -> New File. Analogiczny efekt uzyskamy wybierając z głównego menu aplikacji następujące opcje: File -> New -> File. W odpowiedzi na wybraną opcję otwarte zostanie okno pokazane na rysunku 14. W rozważanym przykładzie nasz plik źródłowy z kodem w języku Verilog nazwaliśmy „top”, sugerując, że jest to nadrzędny moduł w hierarchii projektu. Po naciśnięciu przycisku New w głównym oknie aplikacji Diamond, w zakładce o takiej samej nazwie jak właśnie utworzony plik źródłowy (w tym przypadku „top.v”) zostanie otwarte okno edycyjne, gdzie można wprowadzać kod źródłowy.

Rys. 14. Okno wyboru pliku źródłowego

List. 1. Kod modułu w języku Verilog opisującego działanie przykładowej aplikacji

module top (input RST,

output LED);

defparam OSCH_inst.NOM_FREQ = "2.08"; // częstotliwość w MHz

// instancja oscylatora

OSCH OSCH_inst(.STDBY(1'b0), // 0 - oscylator włączony

.OSC(CLK),

.SEDSTDBY()); // wyjście - nie wykorzystane

reg [20:0] cntr;

// prosty licznik binarny

always @(posedge CLK, negedge RST)

if(~RST) cntr<=0;

else cntr<=cntr+1;

// najmłodszy bit licznika steruje diodą LED

assign LED=cntr[20];

endmodule

Na listingu 1 pokazano kompletny kod źródłowy modułu, który realizuje zadanie sterowania diody LED z częstotliwością około 1Hz. Moduł ma tylko dwa porty: wejściowy o nazwie RST (zerowanie) i wyjściowy o nazwie LED (sterowanie diodą). Jako źródło sygnału zegarowego wykorzystaliśmy wbudowany w układzie MachXO2, oscylator COMS. Szczegółowo sposób wykorzystania tego oscylatora opisuje nota aplikacja Lattice TN1199 (MachXO2 sysCLOCK PLL Design and Usage Guide), dostarczając kompletny szablon utworzenia instancji oscylatora w językach Verilog i VHDL. Częstotliwość oscylatora może być jedną z kilkudziesięciu wybranych wartości (szczegóły – w wymienionej nocie aplikacyjnej), z których najmniejsza to 2,08MHz, zastosowana w naszym przypadku.

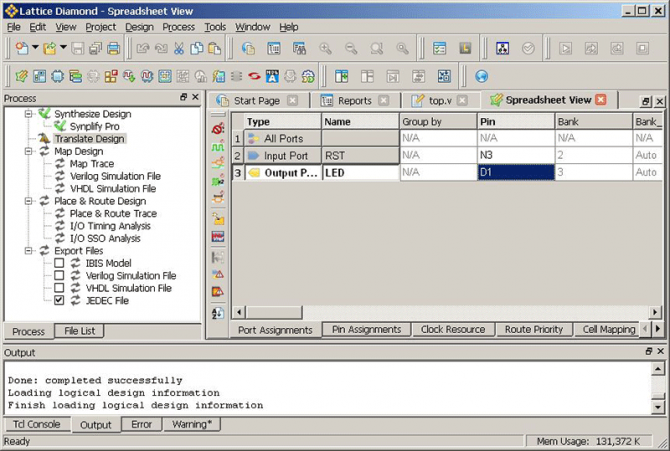

Rys. 15. Przypisanie numerów końcówek do portów wejścia/wyjścia

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii  Mieszacze aktywne – ćwiczenie z serii ADALM

Mieszacze aktywne – ćwiczenie z serii ADALM