Segger publikuje szablon Open Flashloader dla systemów RISC-V

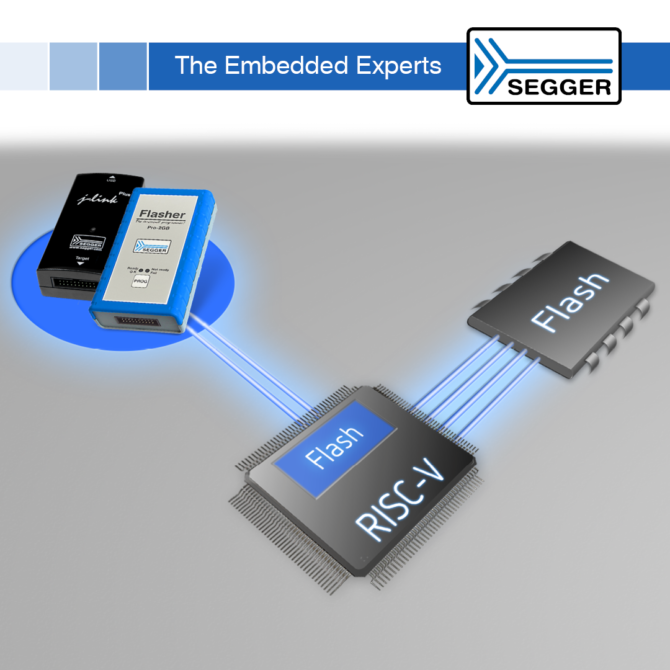

Segger opublikował szablon Open Flashloader dla systemów opartych o rdzeń RISC-V. Szablon można dopasować do każdego systemu RISC-V. Umożliwia on opracowanie kodu ładującego program do pamięci Flash (Flashloadera), który zużywa jedynie 2 kB pamięci RAM.

Open Flashloader to szablon opracowany przez firmę Segger, który umożliwia dodanie definicji mikrokontrolera lub układu SoC do narzędzi J-Link. Pozwala to więc na obsługę układów, których nie ma na oficjalnej liście procesorów wspieranych przez Segger. W szczególności dotyczy to układów we wczesnej fazie rozwoju lub objętych statusem poufności.

Wypełniony szablon umożliwia programatorom J-Link na bezpośrednie wgranie kodu do pamięci Flash mikrokontrolera lub układu SoC opartego o RISC-V. Zapewnia także rozwiązanie umożliwiające masową produkcję oparte o programatory z serii Flasher. Współpracuje z całym zestawem narzędzi programowych Segger obsługujących programowanie mikroprocesorów, takich jak J-Link Commander, debugger Ozone czy J-Flash.

Więcej informacji na stronie https://www.segger.com/products/debug-probes/j-link/technology/flash-download/#adding-support-for-new-devices-open-flashloader

Polska chce zwiększyć znaczenie sektora półprzewodników. Toczą się prace nad krajową polityką w tym obszarze

Polska chce zwiększyć znaczenie sektora półprzewodników. Toczą się prace nad krajową polityką w tym obszarze  Medicalgorithmics wesprze nowego partnera z Korei Południowej w ekspansji na rynku amerykańskim

Medicalgorithmics wesprze nowego partnera z Korei Południowej w ekspansji na rynku amerykańskim  PGZ i Frankenburg Technologies pogłębiają strategiczną współpracę w obszarze nowoczesnych systemów obronnych

PGZ i Frankenburg Technologies pogłębiają strategiczną współpracę w obszarze nowoczesnych systemów obronnych