Mikrokontrolery Microchip PIC18F04Q41 z rozbudowanymi peryferiami analogowymi

Microchip od dłuższego czasu promuje rozwiązania, w których prosty 8–bitowy rdzeń jest obudowany szeregiem niekonwencjonalnych układów peryferyjnych. Oprócz standardowych peryferii spotykanych w większości mikrokontrolerów (na przykład układów licznikowych, komunikacyjnych UART czy SPI itp.), są to również układy, które trudno spotkać w innych rozwiązaniach. Wspólną ich cechą jest możliwość pracy niezależnej od działania rdzenia oraz możliwość programowego, elastycznego łączenia cyfrowych sygnałów wejścia/wyjścia wewnątrz struktury mikrokontrolera za pomocą modułu konfigurowalnej logiki CLC (Configurable Logic Cell). Powstała cała rodzina tanich mikrokontrolerów ze znanym, prostym 8-bitowym rdzeniem PIC16F, potrafiąca wykonywać sprzętowo zadania wymagające sporej wydajności. Rola rdzenia sprowadza się do zaprogramowania i zainicjowania modułów peryferyjnych i wykonywania prostych zadań obliczeniowych, lub sterujących.

Pomysł był na tyle dobry, że Microchip zaczął go implementować w mikrokontrolerach z innymi swoimi rdzeniami. Przykładem takich działań jest rodzina PIC18-Q41 z rdzeniem PIC18. PIC18 to dalej rdzeń 8-bitowy, ale zoptymalizowany do programowania w języku wyższego rzędu (głównie języku C). W założeniach ma być wydajniejszy i przeznaczony do bardziej wymagających zastosowań niż PIC16F. PIC18-Q41 to rodzina produktów, w której położono również nacisk na analogowe układy peryferyjne, jednocześnie nie zaniedbując wspomnianych już peryferii cyfrowych. Podobnie jak w przypadku układów cyfrowych można tu w określonych granicach tworzyć programowane ścieżki sygnałów analogowych wewnątrz struktury mikrokontrolera i łączyć między sobą wejścia i wyjścia układów analogowych. Jednym z przykładów może być połączenie wyjścia wzmacniacza operacyjnego z wejściem przetwornika analogowo-cyfrowego.

Lista analogowych układów peryferyjnych jest dość spora i zawiera:

- Zaawansowany 12-bitowy przetwornik analogowo-cyfrowy ze sprzętowym modułem obliczeniowym,

- Dwa 8-bitowe przetworniki cyfrowo-analogowe,

- Wzmacniacz operacyjny,

- Dwa komparatory analogowe,

- Układ generowania precyzyjnego napięcia odniesienia,

- Układ detekcji przejścia sygnału analogowego przez zero.

Kluczowe funkcje mikrokontrolerów PIC18Q41

Inne kluczowe funkcje obejmują 16-bitowe PWM, bezpośredni dostęp do pamięci DMA, konfigurowalne komórki logiczne CLC i wiele interfejsów komunikacyjnych. PIC18-Q41 jest oferowany w obudowach 14- i 20-pinowych. Najważniejsze zasoby mikrokontrolerów PIC18-Q41 wskazano poniżej:

- Wbudowany oscylator o częstotliwości 64 MHz,

- Pamięć programu Flash do 64 KB,

- Pamięć danych SRAM do 4 KB,

- EEPROM o pojemności 512 B,

- Wzmacniacz operacyjny,

- Dwa 8-bitowe przetworniki cyfrowo analogowe DAC,

- 12-bitowy przetwornik ADCC z dodatkowymi funkcjami obliczeniowymi,

- Do 17 kanałów analogowych przetwornika ADCC,

- Cztery kanały DMA,

- Trzy 16-bitowe podwójne moduły PWM,

- Cztery moduły CLC,

- Trzy moduły CWG

- Dwa analogowe komparatory

- Interfejsy komunikacyjne UART, SPI i I2C

Układy analogowe

Układy analogowe to ważna część układów peryferyjnych mikrokontrolerów. Początkowo w mikrokontrolerach implementowano tylko komparatory analogowe i przetworniki analogowo-cyfrowe. Te układy miały przeciętne parametry i można było je stosować jedynie w mniej wymagających aplikacjach. Konstruktor, który potrzebował dokładnego przetwornika ADC z niskimi błędami przetwarzania musiał użyć zewnętrznego układu. Wraz z rozwojem technologii, parametry przetworników i innych układów analogowych wbudowanych w mikrokontrolery stawały się coraz lepsze, chociaż oczywiście dalej nie dorównywały wysokiej klasy układom zewnętrznym. Obecnie stosowane analogowe układy peryferyjne są na tyle dobre, że mogą być stosowane na przykład w torach pomiarowo-diagnostycznych aparatury medycznej, ale też w torach pomiarowych urządzeń końcowych IoT, układach sterowania silników elektrycznych, czy w przemysłowych układach sterowania. Na rysunku 1 pokazano kluczowe parametry przetwornika ADC rodziny PIC18-Q41.

Rysunek 1. Parametry przetwornika ADC przetwornika PIC18-Q41

Rysunek 1. Parametry przetwornika ADC przetwornika PIC18-Q41

Przetwornik analogowo-cyfrowy ADCC

Przetwornik analogowo-cyfrowy to chyba najczęściej implementowany w mikrokontrolerach układ analogowy. W rodzinie PIC18-Q41 zastosowano moduł przetwornika ADCC. To klasyczny przetwornik analogowo-cyfrowy uzupełniony o możliwość cyfrowej obróbki danych wyjściowych. Oczywiście sam proces obróbki próbkowanych sygnałów analogowych nie jest niczym nowym ani odkrywczym. Jednak do tego celu zazwyczaj konieczne są wydajne, specjalizowane rdzenie z odpowiednimi zasobami (pamięć, dodatkowe jednostki DSP itp.). W 8-bitowym rdzeniu PIC18 niczego takiego nie znajdziemy. Moduł ADCC ma kilka trybów pracy sprowadzających się do sprzętowego uśredniania sygnału i jeden tryb połączony z (również sprzętowym) filtrowaniem dolnoprzepustowym.

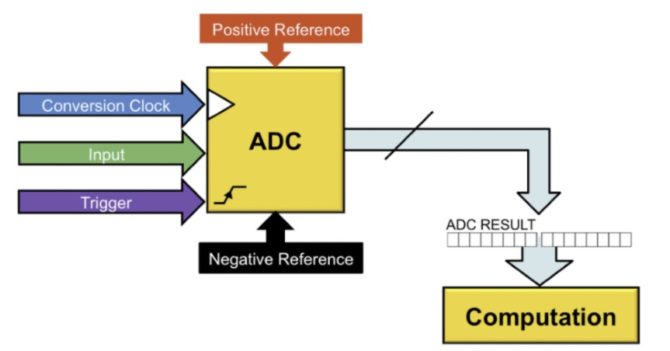

Konfigurowanie przetwornika ADCC polega na wyborze wejść sygnałów wejściowych, napięć odniesienia, częstotliwości taktowania, źródeł wyzwalania i trybów obróbki danych wyjściowych. Selektor sygnału wejściowego wybiera wyprowadzenia mikrokontrolera skonfigurowane jako wejścia analogowe lub sygnały wewnętrzne z wyjścia wbudowanego przetwornika cyfrowo-analogowego, wewnętrznego sensora temperatury, buforów FVR (źródeł napięcia odniesienia) lub wyjścia wzmacniacza operacyjnego. Układ wyzwalania konwersji również może pracować bez udziału CPU. Schemat blokowy przetwornika pokazano na rysunku 2.

Rysunek 2. Przetwornik analogowo-cyfrowy

Rysunek 2. Przetwornik analogowo-cyfrowy

Źródłem dodatniego napięcia odniesienia +Vref może być wewnętrzny układ programowanego precyzyjnego napięcia odniesienia FVR_buffer1, wyprowadzenie mikrokontrolera Vref+ lub też napięcie zasilania. Ujemnym napięciem odniesienia jest potencjał masy GND lub wyprowadzenie mikrokontrolera Vref-. Napięcie wejściowe z selektora jest najpierw zapamiętywane w obwodzie Sample And Hold, a potem próbkowane przez 12-bitowy konwerter SAR.

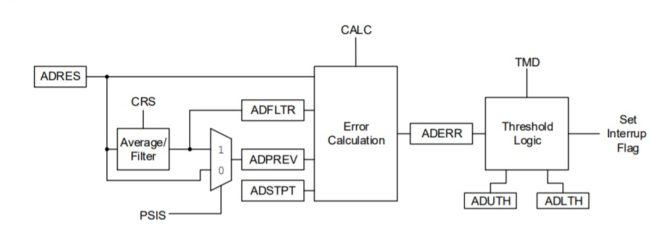

Jak już wiemy, w module ADCC dane wyjściowe po konwersji można poddawać dalszej obróbce – rysunek 3.

Tryby pracy ADCC

Moduł ADCC może po konwersji analogowo-cyfrowej poddawać dane wyjściowe procesowi cyfrowego filtrowania dolnoprzepustowego, uśredniania wyników i porównywania wyników z zadanymi progami.

Moduł można skonfigurować tak, aby na podstawie wyników obliczeń pobierał dodatkowe próbki lub zatrzymywał konwersję i zgłaszał przerwanie. Na rysunku 4 pokazano schemat struktury modułu obliczeniowego.

Rysunek 4. Struktura modułu obliczeniowego

Rysunek 4. Struktura modułu obliczeniowego

W module Error Calculation wyliczany jest błąd na podstawie danych wejściowych z rejestru ADFLT. Tryb obliczania tego błędu jest określony w rejestrze ADCALC, a wynik zapisywany w rejestrze błędu ADC Calculation Error (ADERR). Wartość ADERR jest porównywana z dwoma wartościami progowymi. W rejestrze ADUTH przechowywana jest górna wartość progu wyzwalania, natomiast w rejestrze ADLTH – dolna wartość progu wyzwalania. Spełnienie warunku równości powoduje generowanie przerwania.

Tryb podstawowy

ADCC w trybie podstawowym działa bardzo podobnie jak klasyczny przetwornik ADC. Dzięki funkcjom automatycznego wyzwalania konwersja analogowo-cyfrowa może być inicjowana przez oprogramowanie, inne urządzenia peryferyjne lub zewnętrzne źródła.

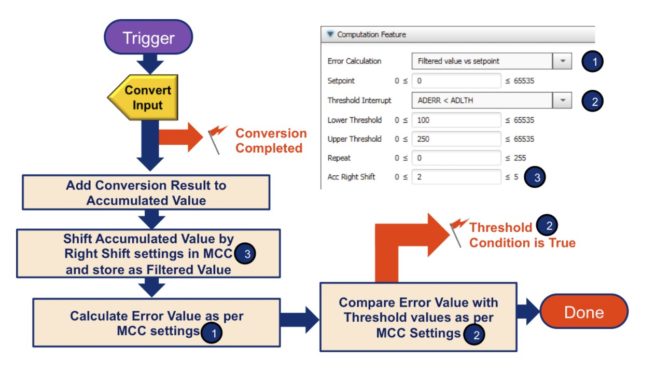

Tryb akumulacji (accumulate)

W trybie akumulacji każdy 12-bitowy wynik konwersji jest dodawany do rejestru akumulatora ADACC (ADC Accumulator Register). Jednocześnie następuje inkrementacja licznika konwersji ADCNT zawierającego ilość skumulowanych próbek. Wartość ADACC jest następnie przesuwana o wartość ACC Right Shift ustawiana w zakresie od 0 do 5 w konfiguratorze MCC konfigurującym moduł przetwornika ADCC. Wynik po przesunięciu zostaje przepisany do rejestru ADFLT (Filtered Value). Następnie na podstawie ustawień w oknie Error Calculation w oknie konfiguratora MCC (rejestr ADCALC) wyliczany jest sygnał błędu. W ostatnim kroku porównywana jest wartość wyliczonego błędu z wartością progów wyzwalania i po spełnieniu warunku równości zgłaszane jest przerwanie.

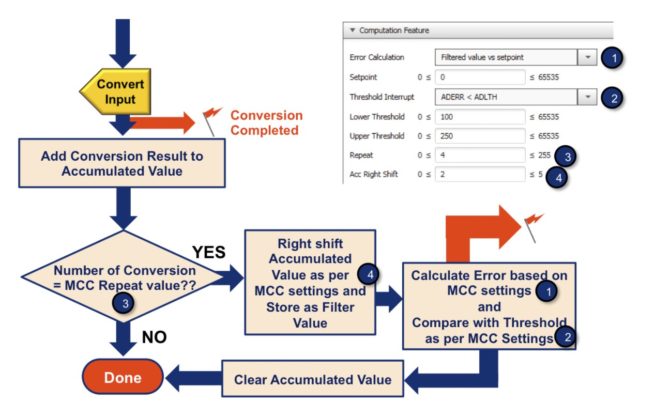

Na rysunku 5. zaprezentowano działanie trybu akumulacji.

Rysunek 5. Działanie trybu akumulacji

Rysunek 5. Działanie trybu akumulacji

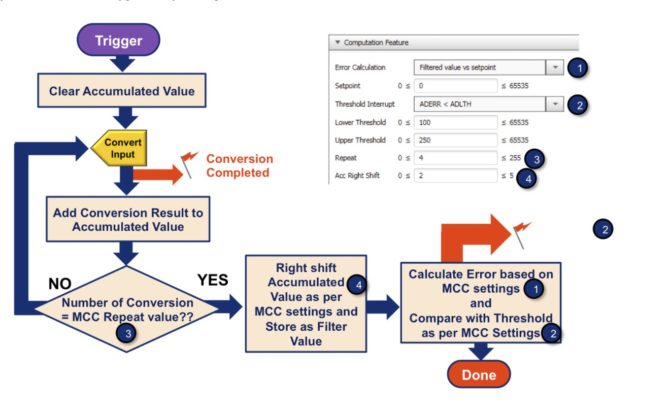

Tryb uśredniania

Ten tryb działa podobnie jak tryb akumulacji. Do rejestru akumulatora ADACC są dodawane kolejne próbki z przetwornika ADC, a rejestr ADCNT jest inkrementowany z każdą kolejną próbką. Rejestr ADFLTR również jest aktualizowany za pomocą przesuniętej w prawo wartości rejestru ADAC, a wartość ADCRS decyduje o liczbie przesunięć w prawo. Jednak w trybie uśredniania porównanie progu jest wykonywane, gdy ADCNT jest większe lub równe zdefiniowanej przez użytkownika wartości ADRPT. W tym trybie, gdy ADRPT = 2 ^ CRS, ostateczna skumulowana wartość zostanie podzielona przez liczbę próbek. Pozwala to na operację porównania progów dla średniej wszystkich zebranych próbek – rysunek 6.

Rysunek 6. Działanie trybu uśredniania

Tryb uśredniania serii

Ten tryb działa podobnie jak tryb uśredniania, z tą różnicą, że po wyzwoleniu konwersji próbkowanie odbywa się w sposób ciągły (automatyczne wyzwalanie) do momentu, kiedy wartość licznika ADCNT zrówna się z zawartością rejestru ADRPT. Otrzymujemy w ten sposób uśrednienie krótkiej serii próbek sygnału wejściowego.

Rysunek 7. Tryb uśredniania serii

Rysunek 7. Tryb uśredniania serii

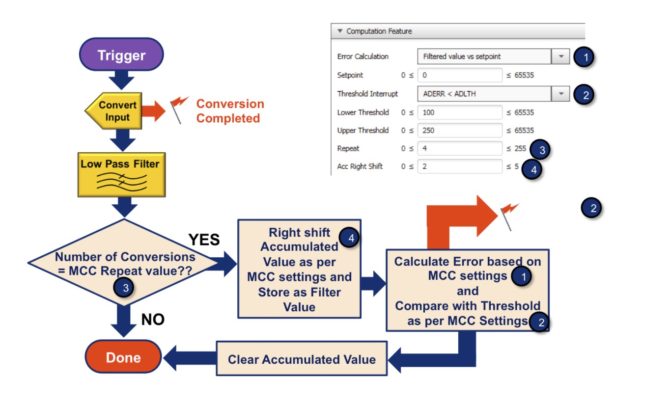

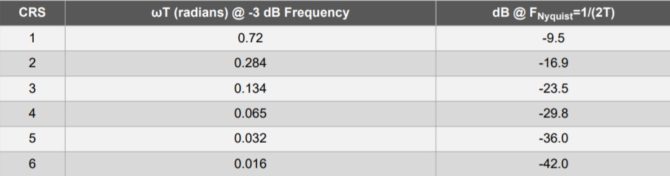

Tryb filtra dolnoprzepustowego

Ten tryb działa podobnie jak tryb uśredniania, czyli gromadzi próbki do momentu, kiedy zawartość licznika ADCNT jest równa wartości rejestru ADPRT. Wtedy uruchamia się porównanie progów dokładniej opisane w trybie akumulacji. Jednak zamiast prostej średniej wykonuje się operację filtrowania dolnoprzepustowego na wszystkich próbkach. Filtrowanie dolnoprzepustowe redukuje wpływ składowej szumu o wysokiej częstotliwości. W tym trybie bity ADCRS określają częstotliwość odcięcia filtra i jego tłumienie – rysunek 9.

Rysunek 8. Tryb filtra dolnoprzepustowego

Rysunek 8. Tryb filtra dolnoprzepustowego

Rysunek 9. Programowanie parametrów filtra: częstotliwości granicznej i tłumienia

Rysunek 9. Programowanie parametrów filtra: częstotliwości granicznej i tłumienia

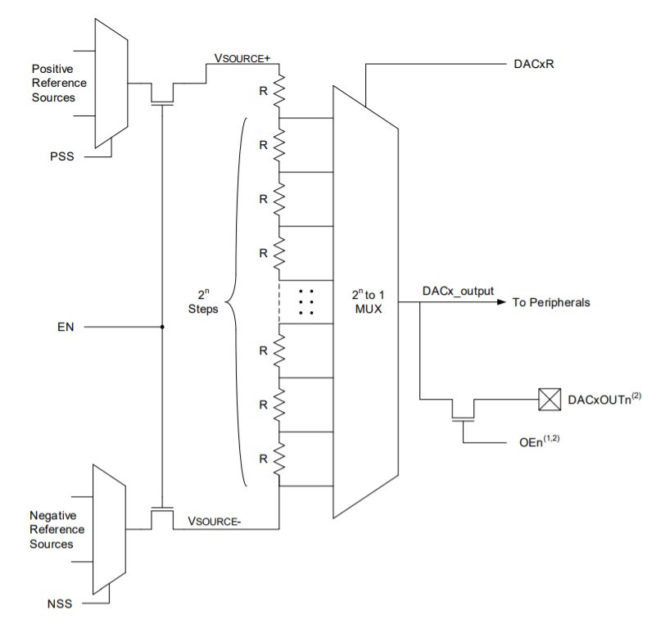

Przetwornik cyfrowo-analogowy

Przetwornik cyfrowo-analogowy wykonuje konwersję wartości cyfrowej na wielkość analogową, najczęściej napięcie lub prąd. W naszym przypadku moduł przetwornika DAC dostarcza napięcie wyjściowe, proporcjonalne do cyfrowej wartości wejściowej i napięcia odniesienia Vref. Na rysunku 10 pokazano schematycznie działanie modułu. Wyjście przetwornika cyfrowo-analogowego (DACx_output) może być źródłem napięcia odniesienia dla innych urządzeń peryferyjnych lub być przekierowane do wyprowadzeń mikrokontrolera.

Rodzina PIC18F04Q41 posiada dwa moduły DAC o rozdzielczości 8-bitowej. Moduł DAC1 oferuje buforowane wyjście i możliwość połączenia go z jednym z wyznaczonych wyprowadzeń wyjściowych mikrokontrolera. Wyjście modułu DAC2 nie ma bufora i nie można go bezpośrednio przekierować do wyprowadzenia. Można za to wewnętrznie połączyć go z modułami analogowego komparatora lub wzmacniacza operacyjnego.

Rysunek 10. Wewnętrzna budowa przetwornika DAC

Rysunek 10. Wewnętrzna budowa przetwornika DAC

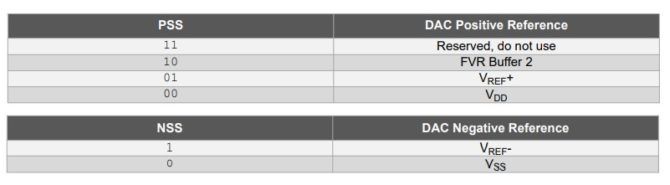

Dodatnie i ujemne odniesienia wejściowe (VREF + i VREF-) można wybrać się z kilku źródeł. Dodatnim napięciem odniesienia (referencyjnym) może być wyjście modułu generowania precyzyjnego napięcia odniesienia FVR Buffer2, napięcie podane na wyprowadzenie mikrokontrolera Vref+, lub napięcie zasilania VDD. Ujemne napięcie odniesienia to napięcie podane na wyprowadzenie mikrokontrolera Vref- lub masa zasilania – rysunek 11.

Rysunek 11. Wybór napięć odniesienia przetwornika DAC

Rysunek 11. Wybór napięć odniesienia przetwornika DAC

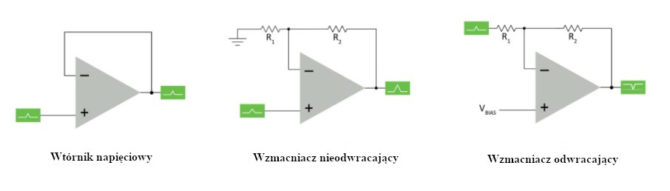

Wzmacniacz operacyjny

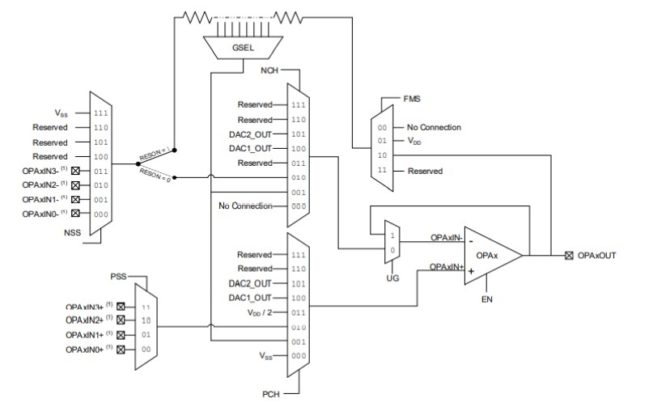

Moduł wzmacniacza operacyjnego zbudowano ze standardowego wzmacniacza operacyjnego o paśmie przenoszenia 5,5 MHz, współpracującego z programowanymi: selektorem wejść, konfiguratorem topologii wzmacniacza (odwracający, nieodwracający) i drabinką rezystancyjną określającą wzmocnienie. Wyjście wzmacniacza można połączyć z dedykowanym wyprowadzeniem mikrokontrolera lub wejściem przetwornika ADC. Źródłami sygnałów napięciowych podawanych na wejścia wzmacniacza mogą być:

- Multipleksowane wyprowadzenia mikrokontrolera OPAxINy- dla wejścia wzmacniacza OPAxIN1-,

- Multipleksowane wyprowadzenia mikrokontrolera OPAxINy+ dla wejścia wzmacniacza OPAxIN1+,

- Wyjścia przetworników cyfrowo-analogowych DAC1 lub DAC2,

- Napięcie o wartości Vdd lub Vdd/2 (dla wejścia OPAxIN1+).

Rysunek 12. Podstawowe konfiguracje pracy wzmacniacza operacyjnego

Rysunek 12. Podstawowe konfiguracje pracy wzmacniacza operacyjnego

Moduł można skonfigurować jako wtórnik napięciowy (wzmacniacz o wzmocnieniu 1), wzmacniacz odwracający z programowanym offsetem lub wzmacniacz odwracający. Programowa zmiana dzielnika rezystancyjnego (bity GSEL) umożliwia implementację wzmacniacza o programowanym wzmocnieniu (PGA).

Rysunek 13. Schemat blokowy modułu wzmacniacza operacyjnego

Rysunek 13. Schemat blokowy modułu wzmacniacza operacyjnego

Istnieje możliwość takiego skonfigurowania przetwornika ADCC, aby jedno z wejść nieodwracających OPAxIN+ wzmacniacza operacyjnego było wejściem napięcia poddawanego konwersji analogowo-cyfrowej. Wtedy automatycznie wyjście wzmacniacza wewnętrznie łączy się z wejściem przetwornika ADC. Umożliwia to wykorzystanie w torze sygnałowym przetwornika wszystkich możliwości wzmacniacza operacyjnego: wzmacnianie sygnału, w tym opcję wzmacniacza o programowanym wzmocnieniu (PGA) lub pracę jako wtórnik napięciowy.

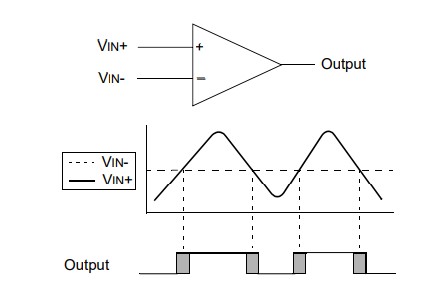

Moduł komparatora analogowego

Moduł komparatora analogowego porównuje dwie wartości napięć analogowych. Wynik porównania jest reprezentowany przez cyfrową informację dwustanową.

Idea działania pojedynczego komparatora z zależnością między poziomami wejść analogowych, a stanem wyjścia cyfrowego pokazano na rysunku 14.

Rysunek 14. Idea działania komparatora analogowego

Rysunek 14. Idea działania komparatora analogowego

Kiedy napięcie analogowe na wejściu VIN+ jest mniejsze niż napięcie analogowe na wejściu VIN-, na wyjściu komparatora jest stan niski. Natomiast, gdy napięcie analogowe na VIN+ jest większe niż napięcie analogowe na VIN-, na wyjściu komparator jest stan wysoki.

Obszary zaznaczone na szaro w sygnale wyjściowym reprezentują niepewność wyjścia wynikającą z czasu odpowiedzi komparatora i ewentualnych wahań sygnału wejściowego.

Moduł komparatora analogowego ma wbudowane funkcje:

- Programowalny wybór wejścia,

- Programowalna polaryzacja wyjścia,

- Wybudzenie ze stanu uśpienia SLEEP po zmianie stanu wyjścia,

- Możliwość wyboru napięcia odniesienia,

- Automatyczne wyzwalanie przetwornika ADC stanem wyjścia komparatora,

- Połączenia z innymi dostępnymi modułami (np. liczniki czasowe).

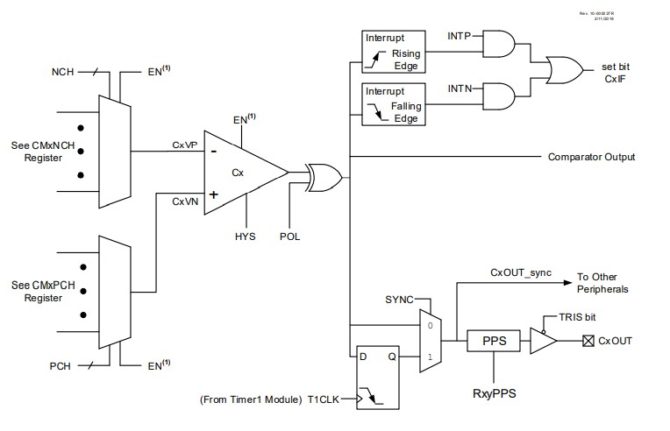

Moduł komparatora schematycznie pokazano na rysunku 15.

Rysunek 15. Moduł komparatora analogowego

Rysunek 15. Moduł komparatora analogowego

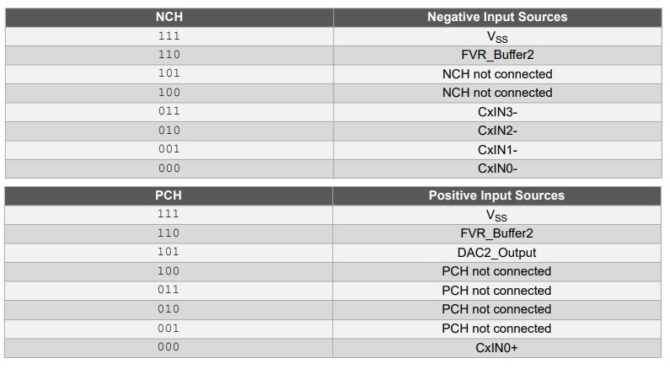

Na rysunku 16 zaprezentowano wybór źródeł napięć podawanych na wejścia CVP i CVN.

Rysunek 16. Wybór wejść komparatora analogowego

Rysunek 16. Wybór wejść komparatora analogowego

Sygnał wyjściowy z komparatora można zsynchronizować z działaniem modułu Timer1. Każde opadające zbocze wyjścia zegara powoduje przepisanie wartości wyjścia komparatora, a także przesłanie tego stanu na wyprowadzenie mikrokontrolera lub do innych układów peryferyjnych. Ten stan jest stabilny do kolejnego zbocza opadającego sygnału Timer1.

Moduł komparatora ma możliwość zgłaszania przerwania od zbocza narastającego lub opadającego pojawiającego się na wyjściu. Wyjście może służyć do wyzwalania konwersji ADC po odpowiednim zaprogramowaniu rejestru ADACT. Konwersja analogowo-cyfrowa wyzwoli się, gdy wyjście osiągnie stan wysoki.

Źródło napięcia odniesienia FVR

FVR to stabilne napięcie odniesienia, niezależne od napięcia zasilania mikrokontrolera VDD, z możliwością wyboru poziomów wyjściowych 1,024 V, 2,048 V lub 4,096 V. Wyjście FVR można skonfigurować tak, aby dostarczało napięcie odniesienia do analogowych urządzeń peryferyjnych, takich jak wymienione poniżej:

- Dodatnie napięcie odniesienia przetwornika ADC,

- Wejście przetwornika ADC,

- Wejście komparatora,

- Dodatnie napięcie odniesienia przetwornika DAC.

Uwaga: Wyjście odniesienia stałego napięcia nie może być wyższe niż napięcie zasilania VDD. Na przykład w mikrokontrolerze zasilanym napięciem +3,3V dostępne są tylko napięcia 1,024 V i 2,048 V.

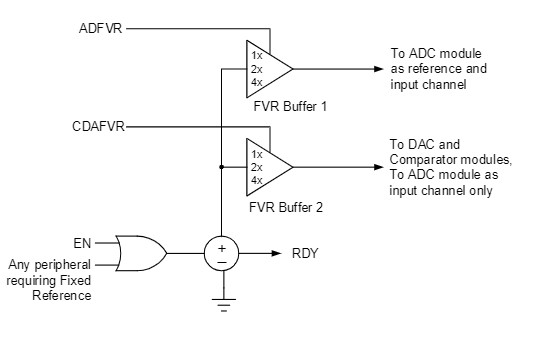

Wyjście precyzyjnego źródła napięcia 1,024 V jest kierowane przez dwa niezależne wzmacniacze z programowalnym wzmocnieniem. Każdy wzmacniacz można zaprogramować na wzmocnienie 1x, 2x lub 4x, aby wytworzyć trzy możliwe poziomy napięcia. Bity ADFVR są używane do włączania i konfigurowania ustawień wzmocnienia dla napięcia odniesienia dostarczanego do modułu ADC. Bity CDAFVR służą do włączania i konfigurowania ustawień wzmocnienia dla napięcia odniesienia dostarczanego do modułów DAC i komparatorów. Rysunek 17 przedstawia schemat blokowy modułu FVR. Po odblokowaniu (bitem EN) źródło zgłasza gotowość do pracy ustawiając bit RDY.

Rysunek 17. Schemat blokowy źródła napięcia odniesienia

Rysunek 17. Schemat blokowy źródła napięcia odniesienia

Wbudowane precyzyjne napięcie odniesienia bardzo upraszcza aplikacje analogowe. Jednak należy sobie zdawać sprawę, z tego, że FVR ma określoną dokładność w bardzo szerokim zakresie temperatur – rysunek 18.

Rysunek 18. Parametry źródła FVR

Rysunek 18. Parametry źródła FVR

Jeżeli aplikacja pomiarowa wymaga bardziej precyzyjnego źródła, należy użyć zewnętrznego układu i napięcie referencyjne podłączać przez wejście Vref+.

Moduł wykrywania przejścia przez zero (ZCD)

Moduł ZCD wykrywa przejście sygnału napięcia przemiennego przez zero. Jest to przydatna funkcja w układach monitorowania przebiegów prądu przemiennego, sterowania fazowego mocą, dokładnego długoterminowego pomiaru czasu itp.

W rzeczywistości moduł ZCD nie wykrywa dokładnie przejścia przez zero, ale przejście przez poziom napięcia równy napięciu referencyjnemu Zcpinv o wartości +0,75 V. Zewnętrzny mierzony sygnał źródłowy jest podłączany do wyprowadzenia ZCDxIN przez rezystor szeregowy ograniczający prąd wpływający do wyprowadzenia.

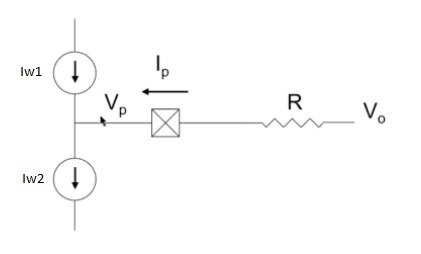

Działanie ZCD opiera się na sterowanych wewnętrznych układach prądowych. Kiedy przyłożone zewnętrzne napięcie Vp na wyprowadzeniu ZCDxIN jest wyższe niż napięcie odniesienia Zcpinv, moduł uruchamia źródło prądowe Iw1 wymuszające prąd o kierunku przeciwnym do Ip – rysunek 19. Powoduje to, że prąd płynący przez zewnętrzny rezystor R jest równy (Ip – Iw1), a napięcie Vp na ZCDxIN spada.

Kiedy przyłożone zewnętrzne napięcie jest niższe niż napięcie odniesienia Zcpinv, moduł uruchamia źródło prądowe Iw2 wymuszające prąd o kierunku zgodnym z Ip. Powoduje to, że prąd płynący przez rezystor R jest równy (Ip + Iw2) i napięcie Vp na ZCDxIN rośnie.

Zapewnia to stałe napięcie na wyprowadzeniu ZCDxIN w pewnych granicach określonych przez wydajności źródeł prądowych. Widać tu też jak ważne jest prawidłowe wyliczenie rezystancji szeregowej R. Szczegółowo opisano to w dokumentacji mikrokontrolera.

Rysunek 19. Zasada działania modułu ZCD

Rysunek 19. Zasada działania modułu ZCD

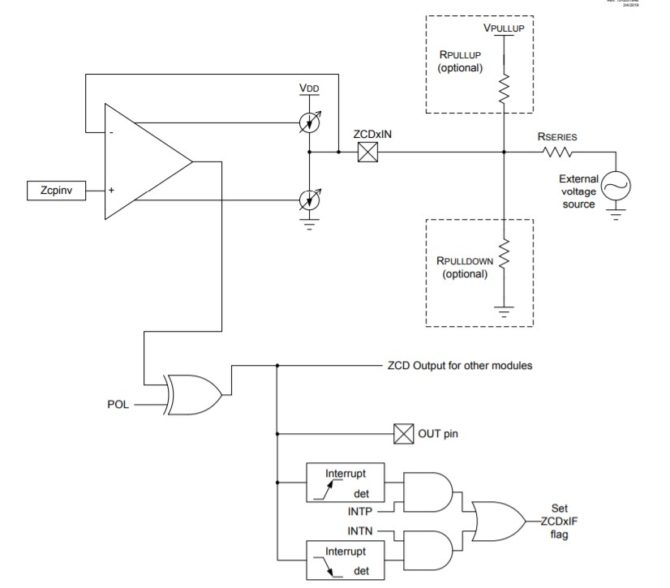

Na rysunku 20 pokazano schemat blokowy modułu ZCD.

Rysunek 20. Schemat blokowy modułu

Rysunek 20. Schemat blokowy modułu

Opcjonalne rezystory Rpullup i Rpulldown pozwalają na detekcję dużych napięć bez konieczności stosowania bardzo dużych rezystancji szeregowych.

Jak wiemy detekcja z przesuniętym poziomem wykrywania nie wykrywa dokładnego przejścia przez zero, ale przejście przez poziom określony przez napięcie odniesienia. Pokazano to na rysunku 21.

Rysunek 21. Wykrywanie przejścia przez zero

Rysunek 21. Wykrywanie przejścia przez zero

Sygnał z wyjścia modułu można podać na wyprowadzenie mikrokontrolera. Może też zgłaszać przerwania od opadającego lub narastającego zbocza.

Podsumowanie

Umieszczenie w strukturze mikrokontrolera wielu analogowych układów peryferyjnych, które dodatkowo można łączyć między sobą programowanymi wewnętrznymi ścieżkami sygnałów analogowych, pozwala na szybkie i tanie tworzenie aplikacji pracujących na styku analog–cyfra. Jest to o tyle istotne, że mimo szybkiej cyfryzacji, w wielu dziedzinach elektroniki ciągle istnieje potrzeba budowania torów analogowych. Integracja w strukturze mikrokontrolera wzmacniacza operacyjnego, źródła napięć referencyjnych, komparatorów czy przetworników ADC i DAC pozwala na znaczne uproszczenie systemu, umożliwia miniaturyzację i docelowo powoduje obniżenie ceny gotowego produktu.

Rodzina mikrokontrolerów PIC18F04Q41 to oczywiście nie tylko układy analogowe. Duża ilość interfejsów cyfrowych, wbudowane kanały DMA, spora jak na tego typu mikrokontrolery pamięć programu i danych, pamięć EEPROM, szeroki zakres napięć zasilających, szeroki zakres temperatur pracy powodują, że te układy można z powodzeniem stosować w bardzo wielu zastosowaniach. Wbudowane tryby oszczędzania energii: doze, idle, sleep, low-power i PMD (peripherial module disable) pozwalają na projektowanie aplikacji zasilanych bateryjnie.

Producent tradycyjnie zapewnia silne wsparcie projektowe w postaci gotowego modułu ewaluacyjnego, bezpłatnego środowiska projektowego MPLAB IDE z wtyczką MCC bardzo mocno upraszczającą konfiguracje wszystkich układów peryferyjnych mikrokontrolera. Dostępna jest bezpłatna wersja kompilatora języka C bez ograniczeń licencyjnych do zastosowania komercyjnego, ale okrojona z funkcji optymalizacyjnej kodu wynikowego.

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii  Mieszacze aktywne – ćwiczenie z serii ADALM

Mieszacze aktywne – ćwiczenie z serii ADALM