Jak uzyskać dokładne testy RF przy pomocy generatora sygnału DDS na Raspberry Pi

Jednym z najważniejszych aspektów, które należy wziąć pod uwagę podczas testowania sprzętu radiowego jest wybór konfigurowalnego, skalibrowanego i niezawodnego źródła sygnału. W tym artykule przedstawiono kompletną implementację syntezowanego generatora sygnału RF opartego o Raspberry Pi, który może generować pojedynczy ton (sinus) od 0 do 5,5 GHz z mocą wyjściową w zakresie od 0 dBm do –40 dBm. Proponowany system opiera się na architekturze bezpośredniej syntezy cyfrowej (ang. direct digital synthesis – DDS), a jego charakterystyka mocy wyjściowej w funkcji częstotliwości może być kalibrowana, zapewniając utrzymanie stabilności poziomu mocy w granicach ±0,5 dB w całym zakresie obsługiwanych częstotliwości.

Wstęp

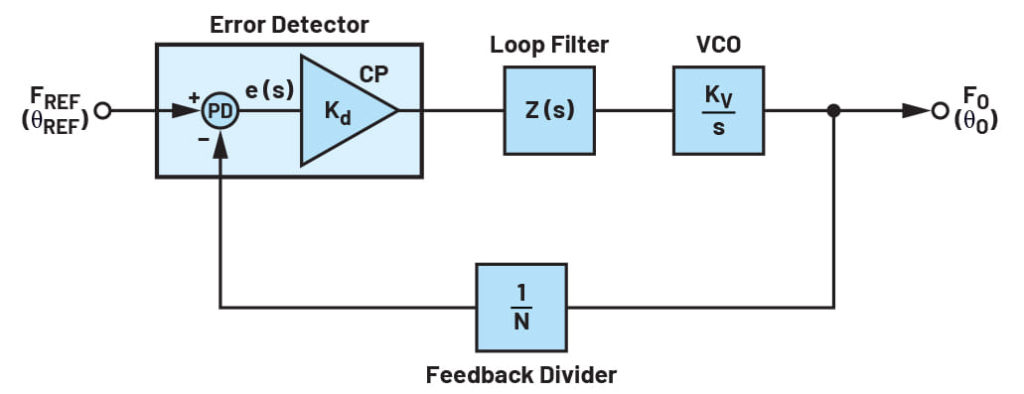

Generator sygnału RF, szczególnie na częstotliwości mikrofalowe, tradycyjnie był oparty o syntezatory z pętlą synchronizacji fazy (PLL)1. Pętla PLL umożliwia generowanie stabilnej wysokiej częstotliwości z niskiej częstotliwości odniesienia. Podstawowy model pętli PLL przedstawiono na rysunku 1. Model ten składa się z układu ze sprzężeniem zwrotnym zbudowanego z oscylatora sterowanego napięciem (VCO), który zmienia częstotliwość wyjściową, detektora błędów, który porównuje wejściową częstotliwość odniesienia z częstotliwością wyjściową oraz dzielnika częstotliwości. Mówi się, że pętla jest w stanie równowagi, gdy częstotliwość wyjściowa i faza dzielnika częstotliwości są równe częstotliwości i fazie wejściowego sygnału odniesienia2-5.

Rysunek 1. Podstawowy model pętli PLL

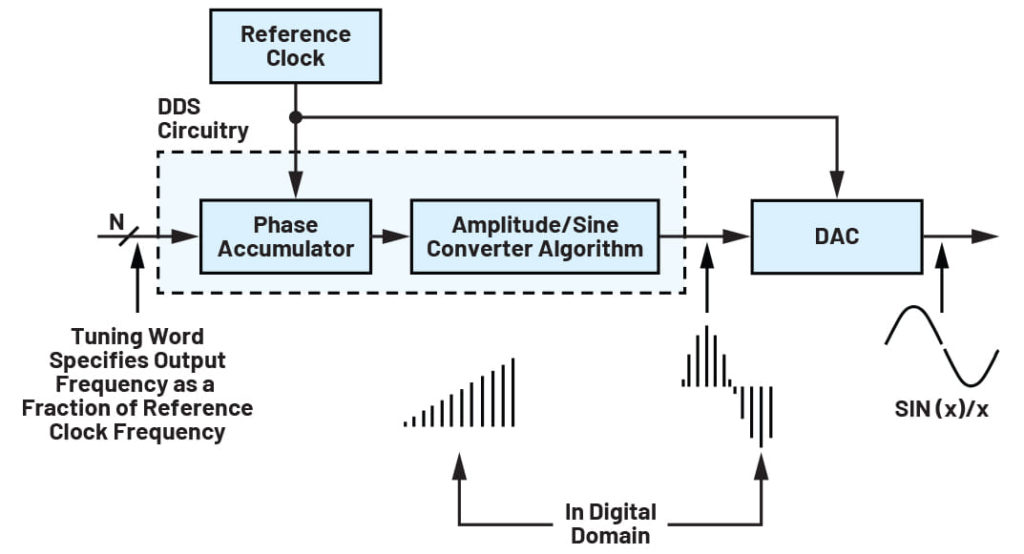

W niektórych zastosowaniach architektura DDS może stanowić alternatywę dla PLL jako syntezatora częstotliwości. Typowy generator sygnału oparty na DDS pokazano na rysunku 2. Do akumulatora fazy podawane jest słowo przestrajające (ang. tuning word), które określa nachylenie sygnału wyjściowego. Górne bity akumulatora przepuszczane są przez konwerter amplitudy-sinusoidę, a na koniec do przetwornika cyfrowo-analogowego. Architektura generatora DDS zapewnia wyraźną przewagę nad pętlą PLL. Na przykład cyfrowy akumulator fazowy DDS umożliwia znacznie dokładniejsze dostrajanie częstotliwości wyjściowej niż syntezator oparty na PLL.

Rysunek 2. Typowy generator sygnału oparty na DDS

Czas przełączania PLL zależy czasu synchronizacji pętli sprzężenia zwrotnego i czasu odpowiedzi VCO. Z natury jest on dłuższy niż w przypadku DDS, gdzie jest on ograniczony jedynie opóźnieniem przetwarzania cyfrowego. Jeśli chodzi o rozmiar płytki, to DDS zajmuje mniejszy obszar, co przekłada się na łatwość projektowania systemu, a jednocześnie eliminuje niektóre wyzwania związane z projektowaniem na częstotliwości radiowe6.

W poniższej sekcji omówiono ogólny projekt kompletnego generatora sygnału sinusoidalnego DDS CN0511, który pracuje w zakresie od 0 do 5,5 GHz. Następnie opiszemy architekturę generatora sygnału wektorowego i jego specyfikację. Kolejna sekcja skupi się na taktowaniu systemu, ponieważ opisuje wymagania częstotliwości odniesienia i połączenia obwodów pomiędzy zegarem, a resztą systemu. Omówiono także architekturę zasilania i układ systemu, opisując, w jaki sposób osiąga on wysoką wydajność energetyczną i akceptowalne rozpraszanie ciepła. Następna część dotyczy architektury oprogramowania i kalibracji. W tej sekcji wyjaśnione zostanie elastyczne sterowanie zapewniane przez oprogramowanie, a także sposób kalibracji mocy wyjściowej. Ostatnia sekcja opisuje ogólne parametry systemu, w tym szum fazowy, skalibrowaną moc wyjściową i wydajność cieplną.

Architektura systemu i rozważania projektowe

A: Ogólny projekt systemu

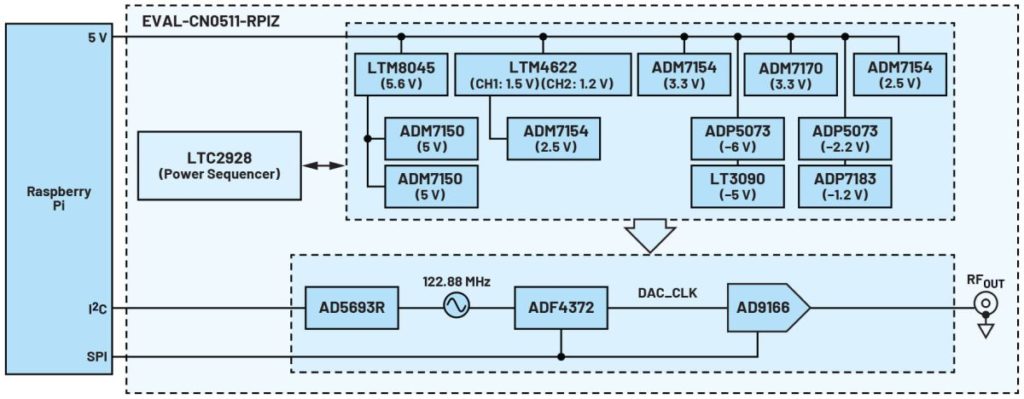

System pokazany na rysunku 3 to kompletny generator sygnału sinusoidalnego DDS od 0 do 5,5 GHz. Przetwornik DAC w architekturze Quad-Switch oraz wzmacniacz wyjściowy zapewniają wyjątkowo niskie zniekształcenia w całym zakresie częstotliwości pracy, a także dopasowanie do standardu 50 Ω.

Układ taktowania obejmuje oscylator referencyjny i pętlę PLL, co eliminuje potrzebę stosowania zewnętrznego źródła zegara. Zasilanie pochodzi z komputera Raspberry Pi, ale płytka zawiera także szereg stabilizatorów i przetwornic o niezwykle wysokim współczynniku tłumienia napięcia zasilania (ang. power supply rejection ratio – PSRR) oraz filtry, co pozwala zminimalizować wpływ konwerterów mocy na parametry RF systemu.

Rysunek 3. CN0511: Generator sygnału DDS oparty na Raspberry Pi

Rysunek 4. Zastosowany układ generatora wektorowego (AD9166) – schemat bloków funkcjonalnych

Rysunek 5. Stopień wyjściowy ADF4372 RF8x

Architekturę pokazaną na rysunku 3 można wykorzystać do różnych zastosowań, takich jak radar, automatyczne testowanie, generator funkcyjny i generator jednotonowego sygnału sinusoidalnego. W tym artykule zaimplementowano to ostatnie rozwiązanie. W poniższych podrozdziałach omówiono główne bloki systemu CN0511.

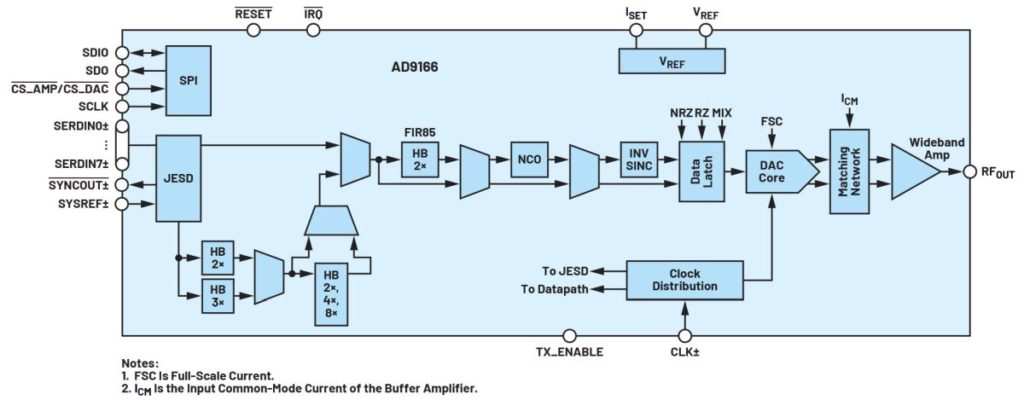

B: Wektorowy generator sygnału

Zastosowany generator sygnału (rysunek 4) składa się z przetwornika cyfrowo-analogowego o próbkowaniu 6 GSPS (tryb 1x NRZ), 8-liniowego interfejsu danych JESD204B 12,5 Gb/s, a także syntezera DDS z wieloma oscylatorami sterowanymi numerycznie (NCO). Zawiera również konfigurowalną cyfrową ścieżkę danych, która obejmuje filtry interpolacyjne, kompensację odwrotną funkcją SINC i miksery cyfrowe.

Układ pokazany na rysunku 4 wykorzystuje 48-bitowy programowalny przetwornik DAC z NCO, aby umożliwić cyfrowe ustawienie częstotliwości z bardzo dużą precyzją (rozdzielczość 43 μHz). Oscylator NCO dla tego przetwornika wymaga jedynie pracy linii zapisu interfejsu SPI z szybkością 100 MHz w celu szybkiej aktualizacji słowa przestrajającego częstotliwości. Interfejs SPI umożliwia także konfigurację i monitorowanie różnych bloków funkcjonalnych znajdujących się w tym przetworniku DAC. Linie JESD nie są używane w tym projekcie, a urządzenie działa wyłącznie w trybie NCO.

Generator ma zintegrowany wyjściowy wzmacniacz RF pracujący w trybie SE i dopasowany do impedancji 50 Ω, eliminując w ten sposób wymagające interfejsy obwodów wyjściowych. Tabela 1 przedstawia najważniejsze cechy AD9166 w różnych warunkach.

Tabela 1. Dane techniczne AD9166

| Parametr | Wartość | Uwagi |

| Szerokość Pasma | 0-9 GHz | |

| SFDR* | -83 dBc | Dla 51 MHz |

| -66 dBc | Dla 451 MHz | |

| -38 dBc | Dla 4051 MHz | |

| Pobór mocy | ~4 W | Dla 5000 Mhz |

| Szum fazowy | -134,8 dBc/Hz | Sygnał 3600 MHz, offset 10 kHz |

| Obudowa | BGA-324 (15 x 15 mm) |

*SFDR (Spurious-Free Dynamic Range): Moc najwyższej niepożądanej harmonicznej w stosunku do mocy sygnału podstawowego

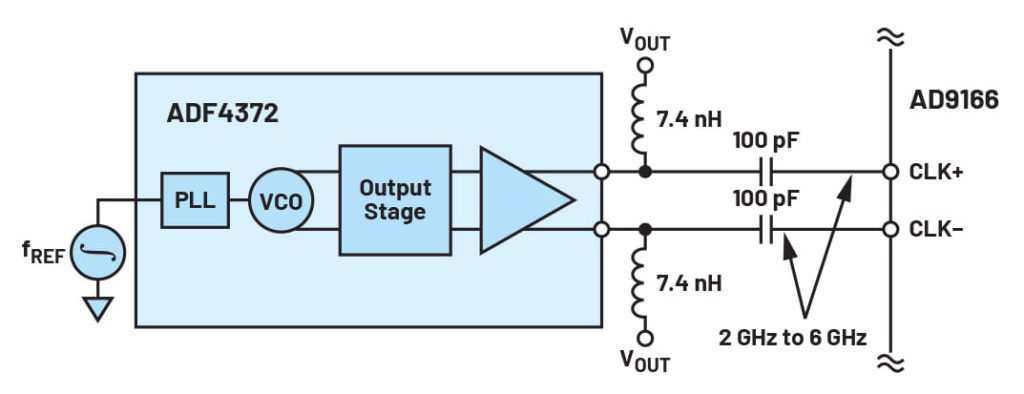

C: Taktowanie systemu

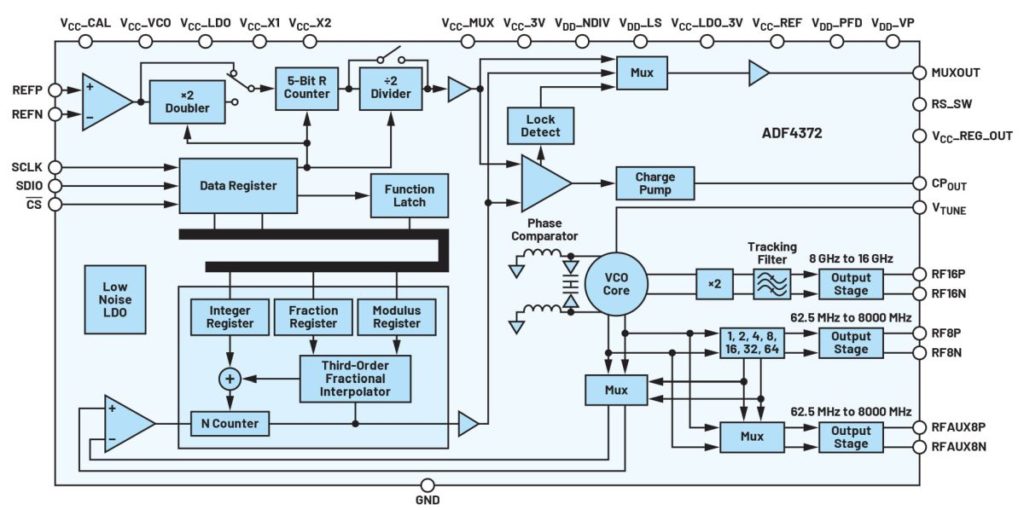

System przedstawiony na rysunku 2 wykorzystuje układ pętli PLL ADF4372 (rysunek 5) – szerokopasmowy syntezator ze zintegrowanym oscylatorem VCO. Umożliwia on implementację syntezatorów z całkowitą lub ułamkową pętlą PLL, z zewnętrznym filtrem pętli i częstotliwością odniesienia. Dodatkowo częstotliwość VCO jest połączona z obwodem dzielenia przez 1, 2, 4, 8, 16, 32 lub 64, co pozwala użytkownikowi generować niskie częstotliwości wyjściowe, jak 62,5 MHz przy RF8x.

Parametry źródła zegara, taka jak szum fazowy i charakterystyka impulsu, a także jego interfejs do szybkiego przetwornika DAC, bezpośrednio wpływają na parametry dynamiczne systemu. Dlatego szum fazowy i inna zawartość widma są modulowane bezpośrednio na sygnał wyjściowy. Aby osiągnąć możliwe najmniejsze zakłócenia od częstotliwości referencyjnej (tzw. Integer Boundary Spurs) i szumu fazowego, układ ADF4372 wykorzystuje niesymetryczny referencyjny sygnał wejściowy, który jest następnie mnożony w celu wytworzenia zegara dla szybkiego przetwornika DAC, jak pokazano na rysunku 6.

Rysunek 6. Połączenie obwodu pomiędzy układami ADF4372 i AD9166.

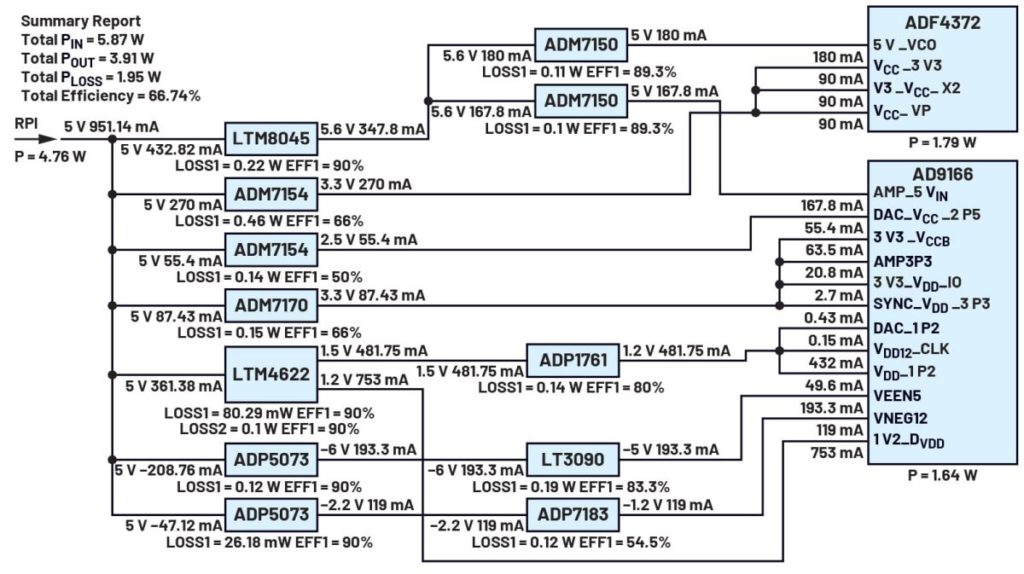

D: Architektura zasilania

Schemat zasilania dla płytki CN0511, pokazany na rysunku 7, wykorzystuje konwertery impulsowe LTM8045, LTM4622 i ADP5073, co w zależności od obciążenia pozwala osiągnąć nawet 90% sprawności. Do zasilania przetwornika DAC, wzmacniacza, PLL i VCO wybrano stabilizatory LDO, tj. ADM7150, ADM7154 i ADP1761, ze względu na ich bardzo niski poziom szumów i wysoki PSRR, co pozwoli uzyskać najniższy możliwy szum fazowy.

Zastosowany układ sekwencera zasilania LTC2928 powoduje, że szybki przetwornik DAC jest włączany we odpowiednim momencie, co pozwala uniknąć jego uszkodzenia.

Sekwencer monitoruje i zarządza czterema szynami napięciowymi, kontrolując moment włączenia napięcia oraz nadzorcze szyny, w tym monitoruje i raportuje spadki napięcia i przepięcia.

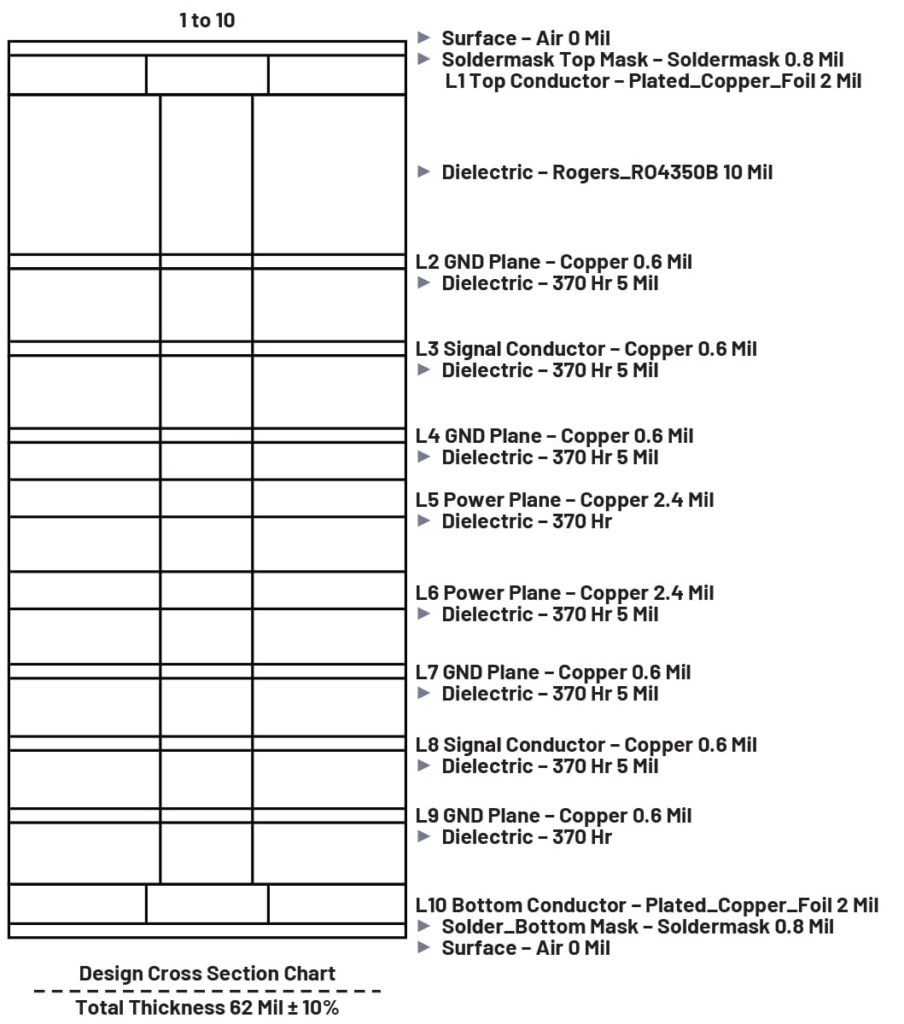

E: Rozmieszczenie elementów

W przypadku, gdy wymagana jest najwyższa wydajność i wysokie częstotliwości wyjściowe, wybór materiałów na płytki drukowane (PCB) znacząco wpływa na wyniki. Rysunek 8 przedstawia zalecany układ PCB CN0511, w którym zastosowano materiał dielektryczny Rogers 4350 na warstwach zawierających ścieżki RF, co pozwala zminimalizować tłumienie dla sygnałów powyżej 3 GHz, co zapewnia również najlepszą integralność sygnału na wyjściu RF.

Rysunek 7. Schemat zasilania systemu

Rysunek 8. Zalecany przekrój PCB i kolejność warstw.

Wydajność cieplna jest bezpośrednio powiązana z konstrukcją PCB i środowiskiem pracy. Aby poprawić wydajność cieplną konstrukcji, na podkładce termicznej PCB zastosowano przelotki termiczne.

Architektura oprogramowania i kalibracja

A: Oprogramowanie sterujące

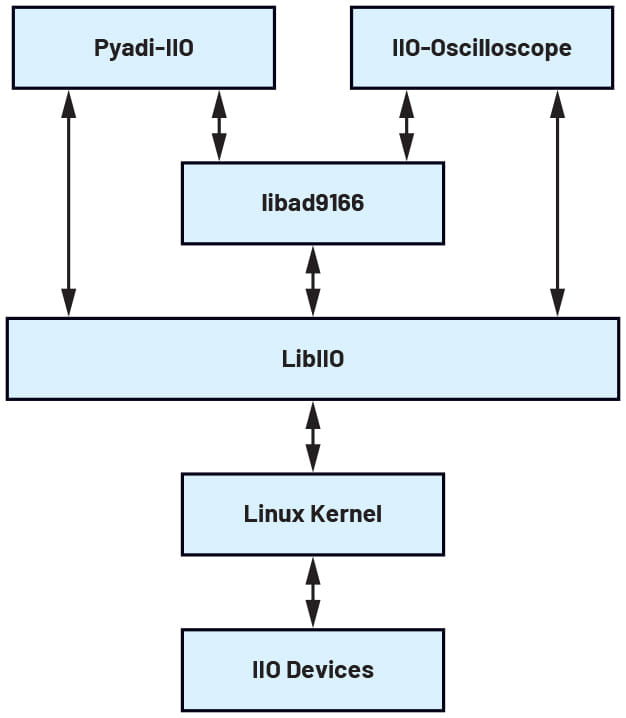

W każdym zastosowaniu obejmującym generator sygnału sterowanie oprzyrządowaniem powinno być łatwe i elastyczne. CN0511 można uznać za układ plug and play, ponieważ wymaga tylko jednej karty SD z obrazem Kuiper Linux podłączonej do Raspberry Pi. Obraz Kuiper Linux zawiera całe niezbędne oprogramowanie potrzebne do sterowania generatorem sygnału. Istnieją dwie metody zmiany mocy wyjściowej i częstotliwości: można użyć modułu PyADI-IIO do napisania kodu lub skorzystać z graficznego interfejsu użytkownika (GUI) IIO Oscilloscope do określenia żądanego sygnału wyjściowego.

PyADI-IIO to moduł Python dla sprzętu ADI z obsługą przemysłowych sterowników wejścia/wyjścia (IIO). Zapewnia uproszczone i łatwe w użyciu metody i atrybuty Pythona pozwalające na kontrolowanie sprzętu. Płytką można sterować za pomocą bardzo prostych komend, które można uruchomić lokalnie lub zdalnie. Za pomocą pętli for i opóźnień można stworzyć dowolnego typu przemiatanie częstotliwości w celu pomiaru innego sprzętu.

IIO-Oscilloscope to wieloplatformowa aplikacja GUI, w której użytkownik określa amplitudę i częstotliwość mocy wyjściowej.

Obydwa moduły, PyADI-IIO i IIO-Oscilloscope, otrzymują również stan czujników temperatury złącza: jeden wewnątrz układu PLL, a drugi wewnątrz układu scalonego generatora wektorowego. Rysunek 9 przedstawia te dwa moduły oprogramowania, a także inne komponenty potrzebne do komunikacji z płytą CN0511 (libAD9166, LibIIO i jądro Linuxa). Biblioteka libAD9166 jest wymagana do dokładnego sterowania mocy wyjściowej i jest już zawarta na obrazie Kuiper Linux. Teoria dotycząca sposobu przeprowadzania kalibracji jest dalej omawiana w części B: Kalibracja mocy wyjściowej.

Rysunek 9. Schemat blokowy elementów oprogramowania potrzebnych do komunikacji z urządzeniem poprzez PyADI-IIO i IIO-Oscilloscope.

B: Kalibracja mocy wyjściowej

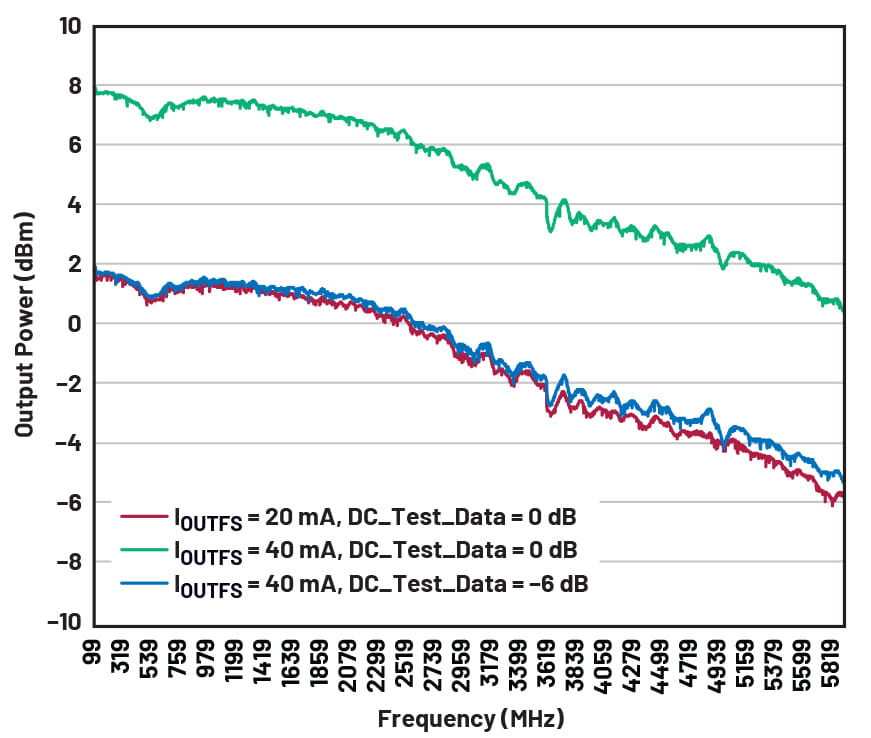

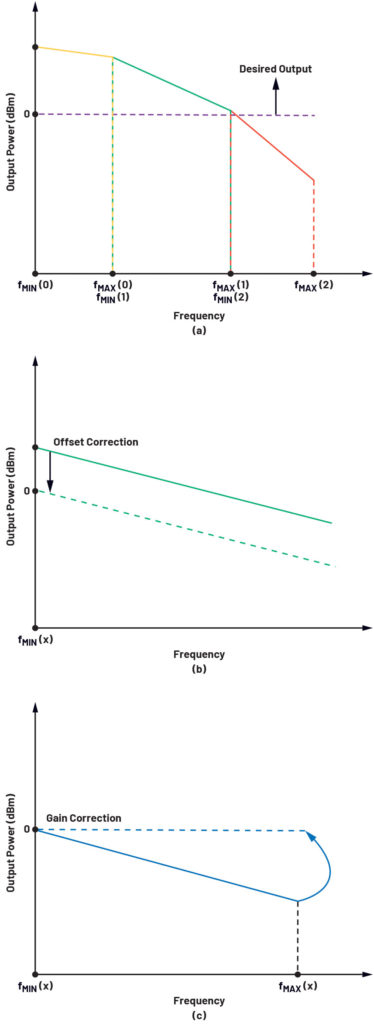

W generatorach sygnału krytyczne jest, aby pasmo urządzenia było możliwie płaskie. W omawianym systemie charakterystyka mocy wyjściowej w funkcji częstotliwości jest głównie wyznaczana przez moc wyjściową generatora. Wraz ze wzrostem częstotliwości impedancja wyjściowa maleje. Ta zmiana impedancji wyjściowej, razem z nawet najmniejszym niedopasowaniem impedancji przy obciążeniu, bezpośrednio wpływa na moc wyjściową. Zmierzona nieskalibrowana charakterystyka mocy wyjściowej znajduje się na rysunku 10. Aby skorygować ten spadek, można przeprowadzić kalibrację oprogramowania w funkcji mocy wyjściowej względem częstotliwości.

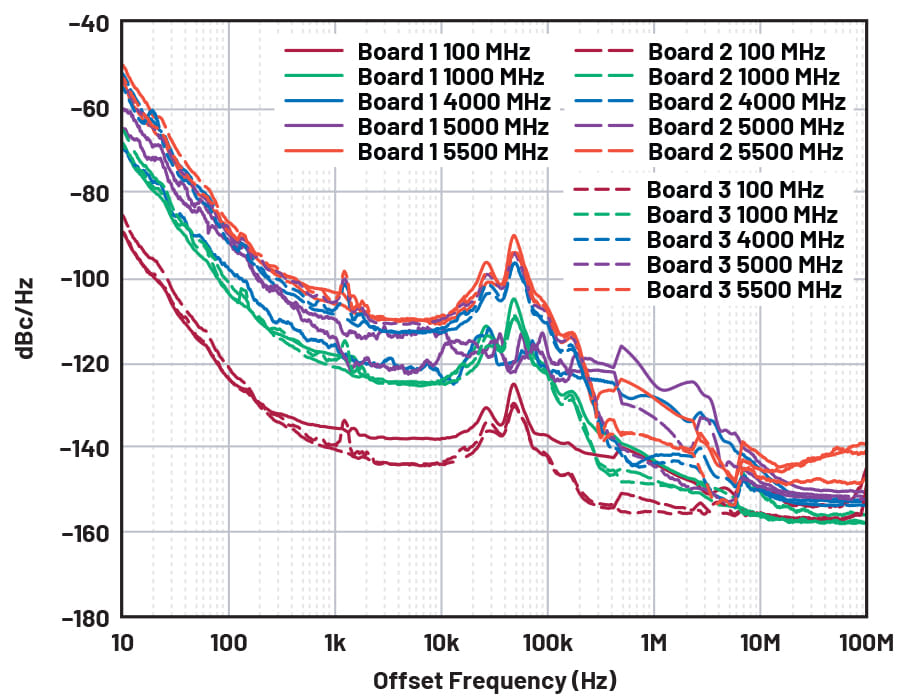

Korekcję mocy wyjściowej umożliwia sterowanie dwóch rejestrów AD9166: 10-bitowy rejestr ustawiający maksymalny punkt skali prądu, Ioutfs_reg (adresy 0x42 i 0x41) oraz 16-bitowy rejestr, który ustawia aktualny prąd maksymalny od 0 do ustawionej wartości maksymalnej, Iout_reg (adresy 0x14E i 0x14F). Te dwa rejestry kontrolują prąd wyjściowy przetwornika DAC, który jest także wejściem dla wzmacniacza wewnątrz AD9166 (rysunek 3).

Ioutfs_reg oferuje zakres dynamiki maksymalnej mocy wyjściowej około 10 dBm, co jest idealną wartością do korekty niepożądanej charakterystyki z rysunku 10.

Rysunek 10. Moc wyjściowa w funkcji częstotliwości: wartość nieskalibrowana

Z pomiarów wynika, że każda płytka PCB wykazywała mniej więcej ten sam kształt charakterystyki pokazanej na rysunku 10, z wyjątkiem różnicy przesunięcia. Mając to na uwadze opracowano dwie procedury kalibracji. Pierwsza procedura jest wykonywana tylko raz i pozwala uzyskać parametry potrzebne do skorygowania kształtu charakterystyki, natomiast druga koryguje błąd przesunięcia pomiędzy każdą płytką i jest uruchamiana jako test produkcyjny. Obie procedury kalibracji są wykonywane poprzez pomiary wyjściowe, obliczenia i korekty rejestrów na podstawie obliczeń.

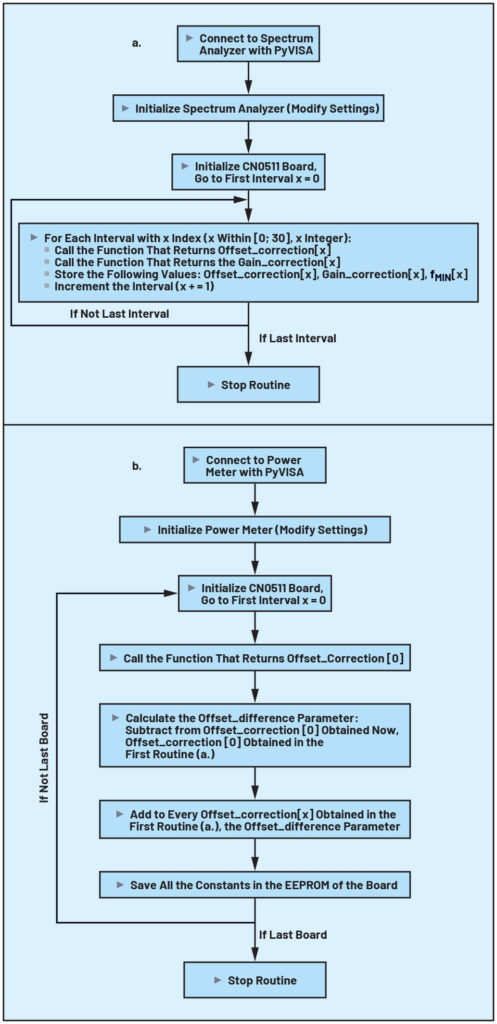

Główny zamysł pierwszej procedury kalibracji przedstawiono na rysunku 11. Po pierwsze, cała charakterystyka z rysunku 10 jest dzielona na wiele przedziałów, które można aproksymować odcinkami liniowymi od fmin[x] do fmax[x], gdzie x jest wartością z przedziału x ∈ [0, 31] oraz jest liczbą całkowitą i wartością dodatnią. Do rzeczywistego projektu wybrano 31 przedziałów, ale na rysunku 11a pokazano tylko trzy przedziały dla lepszej widoczności. Dla każdego przedziału należy uzyskać dwie stałe: jedną dla korekcji przesunięcia, Offset_correction (Rysunek 11b) i jedną dla korekcji wzmocnienia, Gain_correction (Rysunek 11c). Aby śledzić interwały, należy również zapisać parametr fmin[x].

Rysunek 11. Wizualizacja procedur kalibracyjnych: (a) podział charakterystyki na wiele segmentów; (b) korekta przesunięcia dla każdego segmentu; (c) korekta nachylenia dla każdego segmentu.

Rysunek 12a przedstawia schemat pseudokodu, który pokazuje, jak działa pierwsza procedura kalibracji. Aby zrealizować ten algorytm, potrzebny jest bardzo dokładny analizator widma do pomiaru mocy wyjściowej (użyto Keysight E5052B/R&S FSUP). Parametry wynikające z pierwszej procedury (rysunek 12a) są wykorzystywane w drugiej procedurze kalibracji, którą pokazano na rysunku 12b.

Rysunek 12. Schemat pseudokodu dla: (a) pierwszej procedury kalibracji, która jest uruchamiana tylko raz; (b) drugiej procedury kalibracji, która uruchamiana jest na każdej płytce CN0511.

Druga procedura kalibracji (rysunek 12b) jest wykonywana dla każdego egzemplarza płytki PCB w teście produkcyjnym i dodaje tę samą stałą do parametru Offset_correction dla każdego interwału. Na koniec drugiej procedury zmodyfikowane parametry Offset_Correction[x], a także Gain_correction[x] i fmin[x] są zapisywane w EEPROM płytki dla każdego interwału. Parametry te są wykorzystywane w oprogramowaniu podczas dalszej pracy płytki.

Aby ustawić skalibrowaną moc wyjściową, w oprogramowaniu wykorzystuje się równanie 1 do obliczenia wartości rejestru Ioutfs_reg potrzebnej do regulacji mocy wyjściowej przy częstotliwości fx. Jest to częstotliwość w przedziale x: fx ∈ [fmin[x], fmax[x]) i jest liczbą rzeczywistą dodatnią, a fmin[x] jest minimalną częstotliwością przedziału o indeksie x.

Jak widać w równaniu 1, na płytce muszą być zapisane trzy parametry, aby umożliwić korekcję sygnału wyjściowego dla każdego przedziału x: Offset_correction[x], Gain_correction[x] i fmin[x].

Parametry generatora sygnału

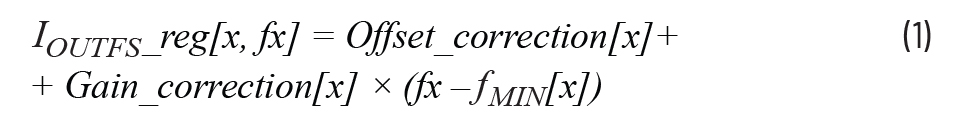

A: Skalibrowana moc wyjściowa

Rysunek 13 przedstawia przy kilku różnych poziomach mocy wyjściowej jak płaskie może być pasmo CN0511. Dla dowolnej mocy wyjściowej ustawionej w zakresie od 0 dBm do –40 dBm dokładność wynosi ±0,5 dBm w całym paśmie, od 0 do 5,5 GHz.

Rysunek 13. Skalibrowana moc wyjściowa w funkcji częstotliwości

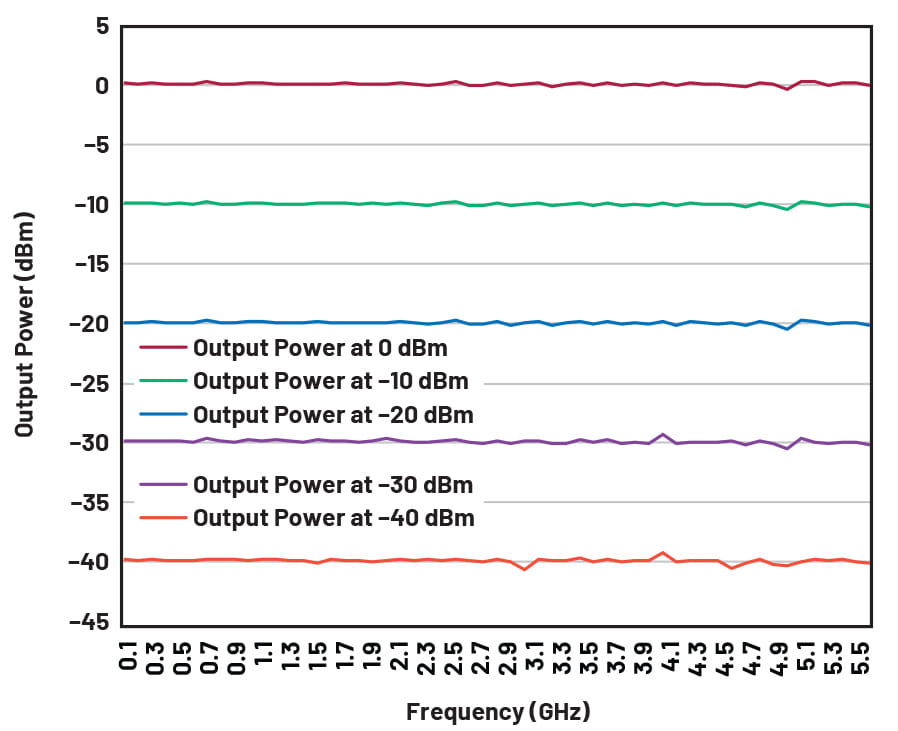

B: Szum fazowy

Jakość źródła zegara, jak również jego interfejs do AD9166 bezpośrednio wpływają na moc szumów fazowych. Szum fazowy i zakłócenia przy danym przesunięciu częstotliwości źródła zegara są bezpośrednio przenoszone na sygnał wyjściowy. Wykresy pokazane na rysunku 14 przedstawiają zmierzony szum fazowy w funkcji przesunięcia częstotliwości. Wszystkie dane zebrano przy mocy wyjściowej ustawionej na maksimum. Jako zegar odniesienia wykorzystano wbudowany, sterowany napięciem oscylator kwarcowy CMOS o częstotliwości 122,88 MHz.

Rysunek 14. Poziom szumu fazowego systemu

C: Wydajność cieplna

Szybki przetwornik cyfrowo-analogowy może wygenerować nawet 4 W mocy. Aby zmniejszyć opór cieplny i umożliwić bezpośrednie chłodzenie układu, wykorzystuje on odsłoniętą obudowę. Do odprowadzania ciepła z obudowy służy radiator z wentylatorem. Po zamontowaniu radiatorów układ LTM4622 pokazuje temperaturę maksymalnie 60,6°C przy temperaturze otoczenia wynoszącej 25°C.

Podsumowanie

W artykule zaproponowano projekt generatora sygnału o wysokiej częstotliwości, niskich zniekształceniach i niskim poziomie szumów. Prezentowany system jest implementacją taniego syntezatora sygnału RF wykorzystującego szybką architekturę DDS opartą na przetworniku DAC. Wykorzystując generator wektorowy oparty na technice DDS, proponowany system ma kilka zalet w porównaniu ze zwykłą pętlą PLL, takich jak prostota, niskie zniekształcenia, wysoka rozdzielczość, niemal natychmiastowe przełączanie częstotliwości, modulacja fazy i amplitudy.

Zalety architektury DDS dają możliwość regulacji i kalibracji mocy wyjściowej oraz dostrajania częstotliwości wyjściowej. Procedura kalibracji zapewnia użytkownikowi dokładność rzędu ±0,5 dBm w zakresie od 0 do 5,5 GHz i zakres dynamiki od 0 dBm do –40 dBm – co jest niemal idealnym rozwiązaniem dla instrumentu laboratoryjnego.

Podziękowania

Dziękujemy wszystkim inżynierom ADI, którzy zapewnili cenne wsparcie techniczne przy powstawaniu tego artykułu.

Bibliografia

1. Paul R. Gray, Paul J. Hurst, Stephen H. Lewis, i Robert G. Meyer. Analysis and Design of Analog Integrated Circuits. Wiley, Styczeń 2009.

2. Mike Curtin i Paul O’Brien. “Phase-Locked Loops for High Frequency Receivers and Transmitters.” Analog Dialogue, Vol. 33, No. 3, Lipiec 1999.

3. VCO Designers Handbook. Mini-Circuits Corporation, 1996.

4. Leon W. Couch. Digital and Analog Communications Systems. Macmillan Publishing Company, 1990.

5. Peter Vizmuller. RF Design Guide. Artech House, 1995.

6. Jim Surber i Leo McHugh. “Single-Chip Direct Digital Synthesis vs. the Analog PLL.” Analog Dialogue, 30, No. 3, Lipiec 1996.

EVAL-CN0511-RPIZ User Guide. Analog Devices, Styczeń 2023.

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485