Renesas opracowuje technologię TCAM 3 nm łączącą wysoką gęstość pamięci i niskie zużycie energii dla układów SoC stosowanych w motoryzacji

Renesas Electronics Corporation, dostawca rozwiązań półprzewodnikowych, wprowadził konfigurowalną trójskładnikową pamięć (TCAM) opartą na procesie 3 nm FinFET. Zapewnia ona wyższą gęstość, niższe zużycie energii i zwiększone bezpieczeństwo funkcjonalne, dzięki czemu nadaje się do zastosowań motoryzacyjnych.

Wraz z szybkim rozwojem technologii 5G oraz przetwarzania w chmurze/na obrzeżach sieci, ruch sieciowy nadal gwałtownie rośnie, napędzając popyt na duże i zróżnicowane konfiguracje TCAM, takie jak 256-bitowe × 4096 wpisów. Konwencjonalne skalowanie oparte wyłącznie na makrach sprzętowych zwiększa powierzchnię obwodową, ze względu na większą liczbę banków i repeaterów oraz utrudnia zamknięcie czasowe, jednocześnie zwiększając moc wyszukiwania. Zastosowania motoryzacyjne wymagają ponadto wyższego poziomu bezpieczeństwa, aby spełnić normy takie jak ISO 26262.

Zintegrowane podejście oparte na makrach sprzętowych i programowych – elastyczna konfiguracja

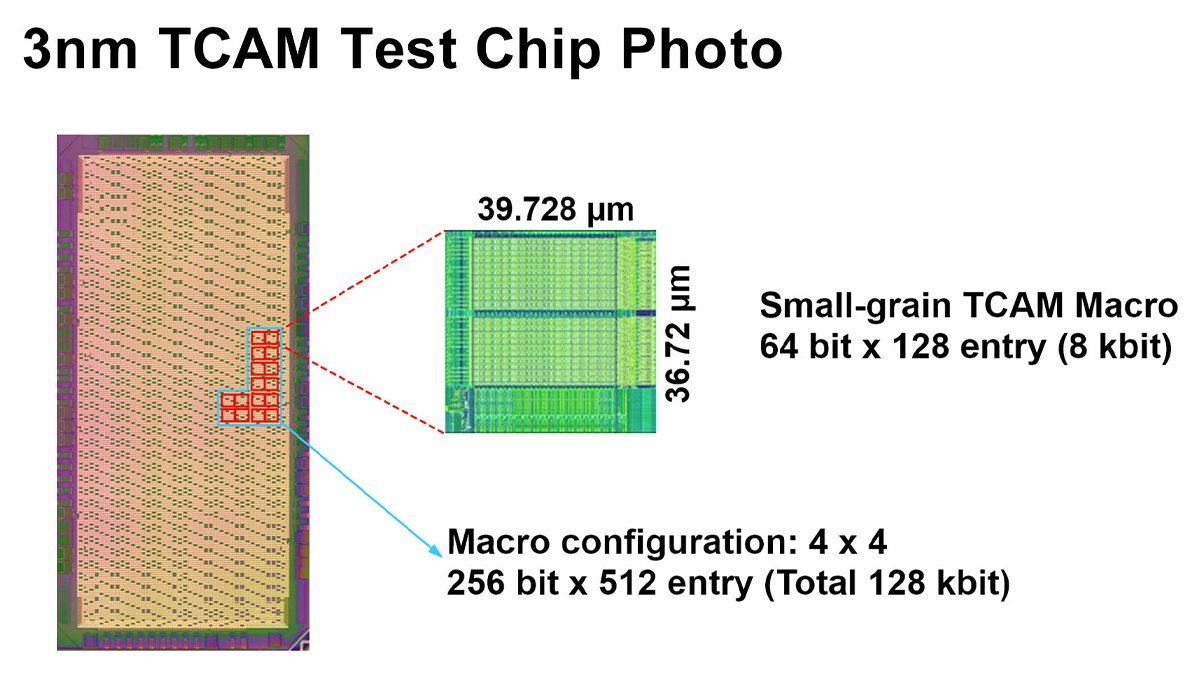

Nowo opracowane makra sprzętowe TCAM są obsługiwane przez kompilator pamięci o drobnej ziarnistości — szerokość klucza wyszukiwania wynosi od 8 do 64 bitów, a głębokość wpisu od 32 do 128. Większe konfiguracje (np. 256 bitów × 4096 wpisów) są realizowane poprzez połączenie tych makr sprzętowych z automatycznym generowaniem makr programowych za pomocą narzędzi, aby zapewnić konfigurowalne pojedyncze makro, które obejmuje szeroki zakres zastosowań na jednym układzie scalonym. Pozwala to osiągnąć gęstość pamięci wynoszącą 5,27 Mb/mm².

Wykrywanie wszystkich niezgodności i wyszukiwanie potokowe na poziomie makra

Każde makro sprzętowe zawiera układ wykrywania wszystkich niezgodności [1] i wykonuje dwuetapowe wyszukiwanie potokowe. Na podstawie wyniku pierwszego etapu drugi etap może być kontynuowany lub zatrzymany, aby uniknąć niepotrzebnego zużycia energii. Na przykład w konfiguracjach 64–256 bitów × 512 wpisów podejście to zmniejsza zużycie energii podczas wyszukiwania:

- Do 71,1% w przypadku wyszukiwania potokowego w kolumnach (z podziałem kluczy, klucze >64-bitowe)

- Do 65,3% w przypadku wyszukiwania potokowego w wierszach (bez podziału kluczy, klucze ≤64-bitowe)

W konfiguracji 256-bitowej × 512 wpisów projekt zapewnia niskie zużycie przy energii wyszukiwania wynoszącej 0,167 fJ/bit, a rozproszone obciążenie czasowe umożliwia zegar wyszukiwania 1,7 GHz. Wynikowa wartość TCAM (gęstość × prędkość ÷ energia) osiąga 53,8, przewyższając wyniki poprzednich prac.

Zwiększone bezpieczeństwo funkcjonalne w zastosowaniach motoryzacyjnych (podzielona magistrala danych i dedykowana pamięć SRAM)

Ponieważ komórki bitowe TCAM dla tego samego adresu są fizycznie sąsiadujące, podwójny błąd bitowy spowodowany błędami miękkimi nie może być skorygowany przez konwencjonalny SECDED ECC [2]. Renesas stosuje dwie techniki:

- Rozdzielenie nieparzystych/parzystych magistrali danych dla danych użytkownika i parzystości ECC w celu zwiększenia fizycznego oddzielenia komórek pamięci, przekształcając potencjalne błędy dwubitowe w możliwe do skorygowania błędy jednobitowe.

- Dedykowana pamięć SRAM dla parzystości ECC z dekoderem adresów niezależnym od TCAM, poprawiającym wykrywalność w przypadku wybrania nieprawidłowego adresu podczas zapisu TCAM.

Środki te znacznie poprawiają bezpieczeństwo wymagane w kontekście motoryzacyjnym. Elastyczne szerokości kluczy i głębokości wpisów TCAM, w połączeniu z oszczędnością energii i bezpieczeństwem funkcjonalnym sprawiają, że nadaje się on nie tylko do zastosowań motoryzacyjnych, ale także do urządzeń przemysłowych i konsumenckich, w których niezbędna jest szybka wymiana danych między czujnikami a procesorami.

[1] Wykrywanie wszystkich niezgodności: obwód, który w pierwszym etapie wyszukiwania określa, czy wszystkie wpisy są niezgodne, i kontroluje, czy zostanie wykonany drugi etap.

[2] SECDED (Single Error Correction, Double Error Detection): schemat ECC, który koryguje błędy jednobitowe i wykrywa błędy dwubitowe.

Renesas wprowadził mikrokontrolery RA4C1 oparte na procesorze Arm® Cortex®-M33 80MHz

Renesas wprowadził mikrokontrolery RA4C1 oparte na procesorze Arm® Cortex®-M33 80MHz  Renesas wprowadza 64-bitowy procesor MPU RZ/G3E do wysokowydajnych systemów HMI wymagających przyspieszenia AI i przetwarzania brzegowego

Renesas wprowadza 64-bitowy procesor MPU RZ/G3E do wysokowydajnych systemów HMI wymagających przyspieszenia AI i przetwarzania brzegowego  Renesas wprowadza mikrokontrolery do zastosowań w urządzeniach z jednym silnikiem, takich jak elektronarzędzia, sprzęt AGD i inne

Renesas wprowadza mikrokontrolery do zastosowań w urządzeniach z jednym silnikiem, takich jak elektronarzędzia, sprzęt AGD i inne