Renesas opracowuje technologie SoC dla wielodomenowych komputerów pokładowych w samochodach SDV

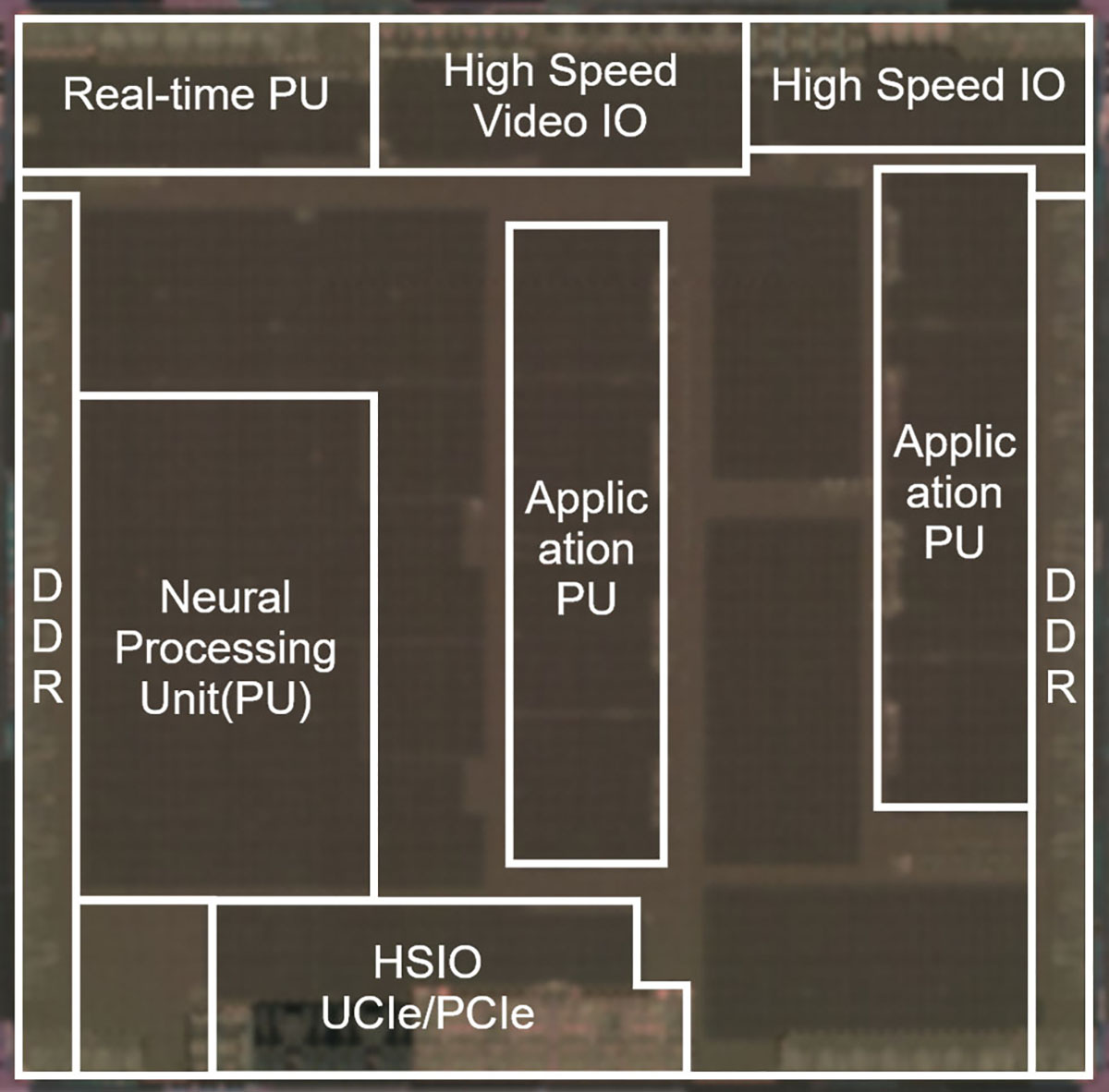

Dostawca rozwiązań półprzewodnikowych opracował trzy technologie System-on-Chip (SoC) dla wielodomenowych elektronicznych jednostek sterujących (ECU) stosowanych w motoryzacji. Charakteryzują się one zaawansowanymi możliwościami przetwarzania AI i funkcjami chipletów, stanowiąc podstawową platformę technologiczną dla architektur elektrycznych/elektronicznych (E/E) nowej generacji w motoryzacji.

W erze pojazdów definiowanych programowo (SDV) samochodowe układy SoC wymagają zaawansowanej wydajności, aby móc jednocześnie obsługiwać wiele aplikacji i oferować skalowalność dzięki chipletom. Muszą również spełniać wymagania dotyczące bezpieczeństwa funkcjonalnego samochodowych układów SoC.

Ponieważ wielodomenowe układy SoC zasilające centralne procesory stają się coraz większe i bardziej złożone, utrzymanie jakości na poziomie samochodu staje się coraz trudniejsze. Wraz ze wzrostem wydajności zaawansowanych układów SoC wzrasta również zużycie energii, co sprawia, że poprawa efektywności energetycznej i bezpieczeństwa ma kluczowe znaczenie. Aby sprostać tym wymaganiom, firma Renesas opracowała następujące nowe technologie:

Architektura chipletów wspierająca bezpieczeństwo funkcjonalne

Aby spełnić wymagania bezpieczeństwa funkcjonalnego układów SoC dla motoryzacji, firma Renesas opracowała nową, autorską architekturę, która wspiera ASIL D nawet w konfiguracji chipletów. Dzięki połączeniu standardowego interfejsu UCIe typu die-to-die z opatentowanym mechanizmem RegionID architektura zapobiega zakłóceniom zasobów sprzętowych, nawet gdy jednocześnie działa wiele aplikacji, zapewniając w ten sposób wolność od zakłóceń (FFI).

Konwencjonalne interfejsy UCIe nie posiadają funkcji przesyłania identyfikatorów RegionID między matrycami. Firma Renesas opracowała metodę mapowania identyfikatorów RegionID do fizycznej przestrzeni adresowej, kodowania ich w regionie UCIe i przesyłania. Umożliwia to bezpieczną kontrolę dostępu poprzez jednostkę zarządzania pamięcią (MMU – Memory Management Unit) i rdzenie czasu rzeczywistego oraz spełnia wymagania bezpieczeństwa funkcjonalnego w chipletach. Ponadto, dzięki utrzymaniu przepustowości od procesorów do magistrali pamięci, interfejs UCIe został potwierdzony w testach jako osiągający wysoką prędkość transmisji 51,2 GB/s, zbliżającą się do górnej granicy prędkości transferu wewnątrz układu SoC. Technologia ta zapewnia zarówno skalowalność, jak i bezpieczeństwo dla wysokowydajnych układów SoC stosowanych w motoryzacji.

Przetwarzanie AI i jakość na poziomie motoryzacyjnym dla systemów SDV

Firma Renesas stworzyła projekt układu SoC 3 nm, który poprawia wydajność jednostek przetwarzania neuronowego (NPU) do przetwarzania AI, zachowując jednocześnie jakość na poziomie motoryzacyjnym. W ostatnich latach jednostki NPU stały się większe, a ich powierzchnia wzrosła 1,5-krotnie w porównaniu z poprzednimi generacjami. Doprowadziło to do zwiększenia opóźnienia zegara między poszczególnymi obwodami. Aby rozwiązać ten problem, firma Renesas przeprojektowała architekturę zegara, dzieląc generatory impulsów zegara (CPG), które w poprzednich projektach były jednostkami na poziomie modułu, i umieszczając mini-CPG (mCPG) na poziomie podmodułu. Znacznie zmniejsza to opóźnienie zegara i spełnia wymagania dotyczące synchronizacji.

Jednak wielowarstwowe mCPG komplikują synchronizację zegara testowego, która ma kluczowe znaczenie dla osiągnięcia zerowej liczby defektów w zastosowaniach motoryzacyjnych. Firma Renesas zintegrowała obwody testowe z hierarchiczną architekturą CPG i ujednoliciła ścieżkę sygnału dla zegarów użytkownika i zegarów testowych. Nowa konstrukcja synchronizuje również mCPG wyższego i niższego poziomu w ramach jednego źródła zegara w trybie testowym. Umożliwia to ujednoliconą regulację fazy. W rezultacie firma była w stanie osiągnąć jakość zgodną z oczekiwaniami zerowej liczby defektów, nawet w przypadku wielkoskalowych układów SoC, zapewniając wysoką niezawodność wymaganą dla układów SoC nowej generacji przeznaczonych do samochodów SDV.

Kontrola i monitorowanie zasilania dla poprawy wydajności energetycznej i bezpieczeństwa

Aby osiągnąć wysoki poziom wydajności wymagany w układach SoC dla motoryzacji, przy jednoczesnej poprawie wydajności energetycznej i bezpieczeństwa, Renesas opracował zaawansowaną technologię zarządzania zasilaniem, która wykorzystuje ponad 90 domen. Umożliwia ona precyzyjną kontrolę zasilania, od kilku miliwatów do kilkudziesięciu watów, w zależności od warunków pracy. Ponadto firma Renesas podzieliła przełączniki zasilania (PSW) na pierścieniowe i rzędowe, aby zmniejszyć spadki IR (spadki napięcia) związane ze wzrostem gęstości prądu wynikającym z mniejszych geometrii procesowych. Po włączeniu zasilania pierścieniowe PSW tłumią prądy rozruchowe. Następnie rzędowe PSW wyrównują impedancję w domenie. Razem zmniejszają one spadki IR o około 13% w porównaniu z konwencjonalnymi konstrukcjami.

Aby spełnić normy bezpieczeństwa funkcjonalnego ASIL D, konfiguracja dual core lock step (DCLS) steruje rdzeniami głównymi i kontrolnymi za pomocą niezależnych przełączników zasilania i kontrolerów. Dzięki tej konstrukcji, nawet jeśli jedna strona ulegnie awarii, można ją wykryć dzięki działaniu lockstep. Ponadto dla każdego sygnału bramki PSW wykonywane jest monitorowanie pętli zwrotnej, dzięki czemu w przypadku awarii wykrywane są stany wyłączenia. Do monitorowania napięcia wykorzystywany jest cyfrowy miernik napięcia (DVMON), który jest bardzo odporny na dryft temperaturowy. Poprawia to tolerancję starzenia o 1,4 mV. Technologie te umożliwiają tworzenie wysokowydajnych układów SoC dla motoryzacji, które zapewniają zarówno energooszczędność, jak i bezpieczeństwo.

Nowe technologie wykorzystywane są w układzie SoC R-Car X5H firmy Renesas przeznaczonym do wielodomenowych komputerów pokładowych w samochodach.

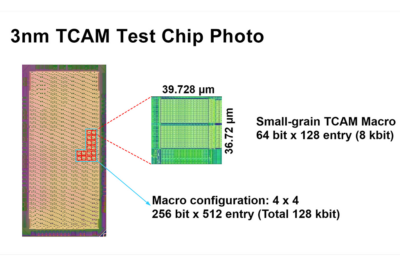

Renesas opracowuje technologię TCAM 3 nm łączącą wysoką gęstość pamięci i niskie zużycie energii dla układów SoC stosowanych w motoryzacji

Renesas opracowuje technologię TCAM 3 nm łączącą wysoką gęstość pamięci i niskie zużycie energii dla układów SoC stosowanych w motoryzacji  Renesas wprowadził mikrokontrolery RA4C1 oparte na procesorze Arm® Cortex®-M33 80MHz

Renesas wprowadził mikrokontrolery RA4C1 oparte na procesorze Arm® Cortex®-M33 80MHz  Tria rozszerza portfolio SMARC o nowy moduł oparty na procesorze Renesas RZ/G3E do zastosowań HMI

Tria rozszerza portfolio SMARC o nowy moduł oparty na procesorze Renesas RZ/G3E do zastosowań HMI