NanoIC otwiera dostęp do pierwszych w historii hybrydowych połączeń między-układowych; zestaw do projektowania (PDK) połączeń typu RDL i D2W

Dzięki linii pilotażowej NanoIC, europejskiej inicjatywie koordynowanej przez imec i dedykowanej przyspieszeniu innowacji w technologiach chipów wykraczających poza 2 nm, możliwe stało się wprowadzenie na rynek dwóch pierwszych zaawansowanych zestawów do projektowania procesów połączeń (PDK – Process Development Kit):

- zestaw z warstwą redystrybucji połączeń o dużej precyzji <20 um, tzw. RDL (Redistribution Layer),

- zestaw hybrydowych połączeń typu chip -płytka półprzewodnikowa, w tym wypadku krzemowa, tzw. połączenia D2W (Die-To-Wafer).

Powyższe zestawy projektowania PDK udostępniają zaawansowane możliwości montażu dla uniwersytetów, start-upów oraz innowacyjnych firm branżowych, stanowiąc ważny krok w kierunku zapewnienia wysokiej gęstości i energooszczędnych połączeń pomiędzy chipami.

W miarę jak przemysł półprzewodników zmierza w kierunku coraz bardziej złożonych systemów, zaawansowane pakowanie stało się kluczowym czynnikiem wspierającym ten postęp. Zamiast jedynie zamykać pojedyncze układy scalone, dzisiejsze technologie pakowania łączą wiele układów scalonych (chipletów) w ściśle zintegrowane systemy, w których wydajność, energooszczędność i przepustowość zależą od efektywności współdziałania tych komponentów. Umożliwiając łączenie chipletów z dużą gęstością, zaawansowane pakowanie stanowi podstawę dla kolejnej generacji wysokowydajnych komputerów, akceleratorów AI i aplikacji intensywnie przetwarzających dane.

Aby umożliwić uniwersytetom, start-upom, małym i średnim firmom oraz innym przedsiębiorstwom przemysłowym przekształcenie tych koncepcji w praktyczne projekty, NanoIC wprowadza na rynek pierwszą wersję swoich hybrydowych zestawów projektowych (PDK) do projektowania warstw redystrybucji (RDL) i hybrydowych procesów łączenia chipów z płytką (D2W). Te zestawy PDK, zbudowane na linii pilotażowej NanoIC, zapewniają projektantom wczesny dostęp do zasad projektowania i sprawdzonych bloków konstrukcyjnych niezbędnych do integracji układów scalonych z układami o wysokiej gęstości.

RDL o dużej precyzji: prowadzenie ścieżek połączeń o wysokiej gęstości na podłożach polimerowych.

Warstwa redystrybucji o dużej precyzji (RDL) wprowadza nowy sposób uzyskiwania połączeń między układami scalonymi przy użyciu podłoży polimerowych. Tradycyjnie podłoża te nie umożliwiały wykonywania bardzo cienkich linii / połączeń, co ograniczało ich zastosowanie w zaawansowanych systemach obudowywania układów scalonych. Technologia Imec, opracowana w ramach projektu NanoIC, pokonuje tę barierę, umożliwiając połączenia o wyjątkowo dużej precyzji w polimerowym systemie RDL. Dzięki szerokościom linii i odstępom między nimi do 1,3 mikrona oraz skoku o gęstości do 20 mikronów, układ RDL zapewnia projektantom dostęp do połączeń, które mogą zwiększyć prędkość komunikacji nawet o 40% i zmniejszyć zużycie energii na bit nawet o 15% w interfejsie UCIe-Advanced typu „dwu-układ”. W rezultacie RDL o wysokiej rozdzielczości staje się atrakcyjną opcją integracji dla szerokiej gamy nowych aplikacji, od zastosowań motoryzacyjnych i obliczeń o wysokiej wydajności po architekturę GPU nowej generacji.

Hybrydowe połączenie D2W PDK: ultra-gęste połączenia 3D między układami scalonymi

Hybrydowe połączenie D2W wprowadza drugą, wydajną technikę integracji, umożliwiając niezwykle kompaktowe, bezpośrednie połączenia między układami scalonymi z wykorzystaniem trzeciego wymiaru. Zamiast polegać na tradycyjnych połączeniach miedzianych, łączenie hybrydowe tworzy bezpośrednie połączenia między układem CMOS a interfejsem obudowy. Eliminuje to pasożytnicze efekty związane z połączeniami miedzianymi i umożliwia niskostratne, energooszczędne ścieżki komunikacyjne.

Dzięki możliwości tworzenia bardzo gęstych połączeń o dużej przepustowości między układami scalonymi, hybrydowe połączenie D2W jest szczególnie przydatne w aplikacjach AI, zaawansowanych platformach obliczeniowych i wysokowydajnych architekturach GPU.

Ważny krok w kierunku pełnej funkcjonalności produkcji masowej

Dzięki tej wersji imec staje się pierwszym na świecie producentem łatwo dostępnych technologii połączeń i zestawów do ich projektowania PDK o tych poziomach integracji i wymiarach. Ta „wersja wstępna” zapewnia projektantom niezbędne narzędzia do rozpoczęcia oceny technologii: systematyczne tworzenie układów, automatyczne i niestandardowe planowanie połączeń oraz weryfikację reguł projektowych.

– To przełomowy zestaw PDK. Daje badaczom, start-upom i firmom niezbędne narzędzia do rozpoczęcia projektowania, testowania pomysłów i przekazywania opinii. W miarę rozwoju zestawy będą ewoluować od projektowych do gotowych do produkcji narzędzi z możliwością produkcji masowej. Umożliwią projektantom przetestowanie układu stworzonego za ich pomocą i jego fizyczną produkcję na linii pilotażowej, co pozwala na zweryfikowanie koncepcji w krzemie, a nie tylko w symulacji – wyjaśnia Nicolas Pantano, kierownik zespołu architektów demonstracyjnych w imec.

Wprowadzając na rynek te dwa zestawy PDK do wykonywania zaawansowanych połączeń między-układowych, NanoIC rozszerza swoją ofertę do pięciu publicznie dostępnych zestawów do projektowania. Po wcześniejszych wersjach PDK N2, A14 i eDRAM, wprowadzenie narzędzi PDK do projektowania hybrydowych połączeń RDL i D2W o dużej precyzji stanowi kolejny kamień milowy w budowaniu kompletnego zestawu narzędzi projektowych, wykraczającego poza narzędzia do projektowania chipów w technologiach 2 nm, obejmującego logikę, pamięć, a teraz także technologie połączeń.

Aby wesprzeć praktyczne badania, NanoIC organizuje również dedykowane warsztaty poświęcone projektowaniu, z wykorzystaniem narzędzi PDK RDL i D2W, które odbędą się 27 maja 2026 roku. Informacje dostępne są na stronie NanoIC.

Grzegorz Kamiński: Taka informacja prasowa wymaga komentarza. Wiele osób czytając ten tekst nie będzie wiedziało i rozumiało, co tak naprawdę oferuje imec. A ponieważ portal jest skierowany do szerokiego grona elektroników, a w tym gronie nastąpiła daleko idąca specjalizacja, zresztą jak w wielu dziedzinach naszego życia, to pozwolę sobie na dodanie poniższego komentarza.

Obecnie przy najbardziej zaawansowanych technologiach półprzewodnikowych o rozmiarach krytycznych 2nm trudno będzie o dalszy postęp. Dlatego coraz większe znaczenie mają technologie hybrydowego montażu chipów w tzw. chiplety. Jednocześnie te technologie umożliwiają budowanie systemów z chipów wykonanych w różnych technologiach, podobnie jak projektujemy schemat systemu na PCB. Wtedy nie zastanawiamy się w jakiej technologii jest dany układ scalony, ale tak planujemy schemat, by poszczególne układy scalone mogły ze sobą współpracować.

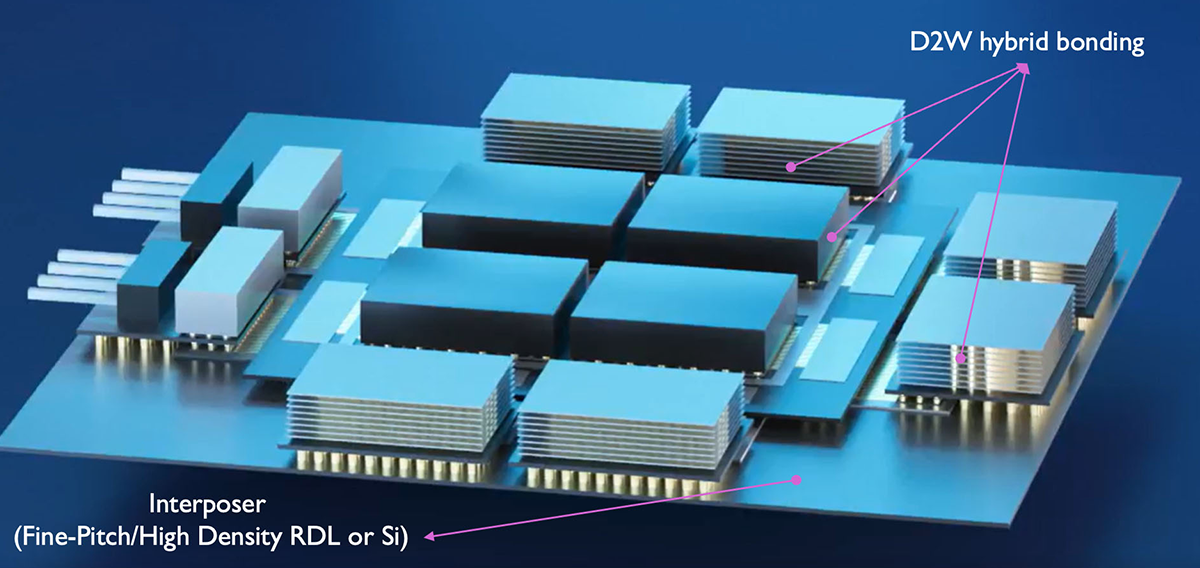

Zaawansowany montaż chipletów wykonuje się teraz w dwóch zasadniczych technologiach określanych 2.5D i 3D.

Porównanie montażu 2.5D i 3D

Montaż 2.5D polega na umieszczeniu wielu układów scalonych znajdujących się obok siebie na podłożu zwanym interposer, dzięki czemu możemy kierować sygnałami między poszczególnymi układami scalonymi.

Interposer to warstwa pośrednia (lub podłoże) umieszczona między układem scalonym (chipem) a obudową lub innym układem scalonym, która ułatwia ich połączenie elektryczne i mechaniczne. Można go sobie wyobrazić jako pomost umożliwiający prowadzenie połączeń o dużej gęstości, który umożliwia efektywną komunikację wielu układów scalonych. Można zapytać dlaczego tego nie zrobić na PCB. W większości przypadków trudno jest połączyć bezpośrednio chip do PCB i nie ma możliwości, by na PCB uzyskać gęstość połączeń < 20um.

Do tego właśnie potrzebna jest nam warstwa pośrednicząca.

Co to jest RDL?

RDL w półprzewodnikach oznacza Redistribution Layer (warstwę redystrybucyjną). Jest to metalowa warstwa połączeń dodawana podczas zaawansowanego pakowania, która przekierowuje punkty wejścia/wyjścia układu scalonego do różnych lokalizacji, ułatwiając ich połączenie z obudową lub innymi układami scalonymi.

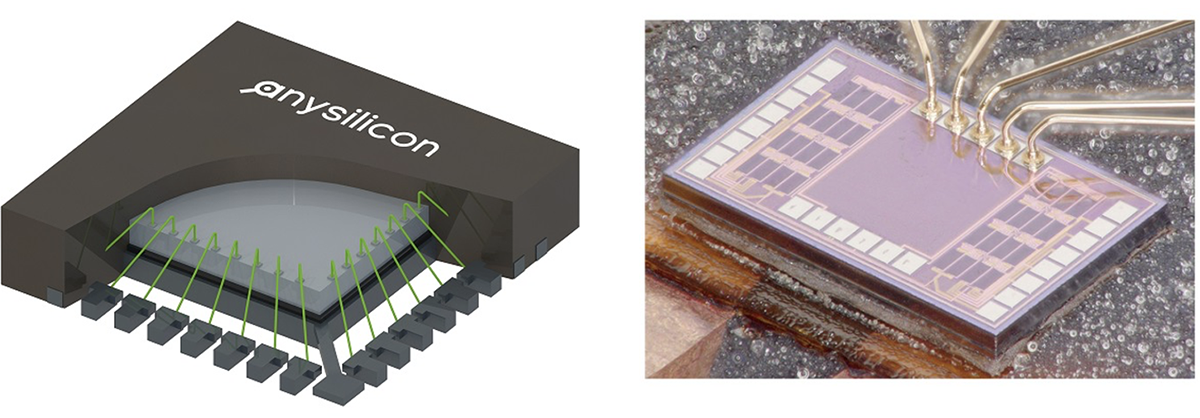

Większość produkowanych układów scalonych ma pady do wykonania połączeń zewnętrznych na obrzeżu układu:

Standardowe rozmieszczenie padów na układzie scalonym na obrzeżu chipu do wykonania połączeń z obudową. Pady to te kwadratowe elementy na obrzeżu układu scalonego | źródło: anysilicon i Yole Group

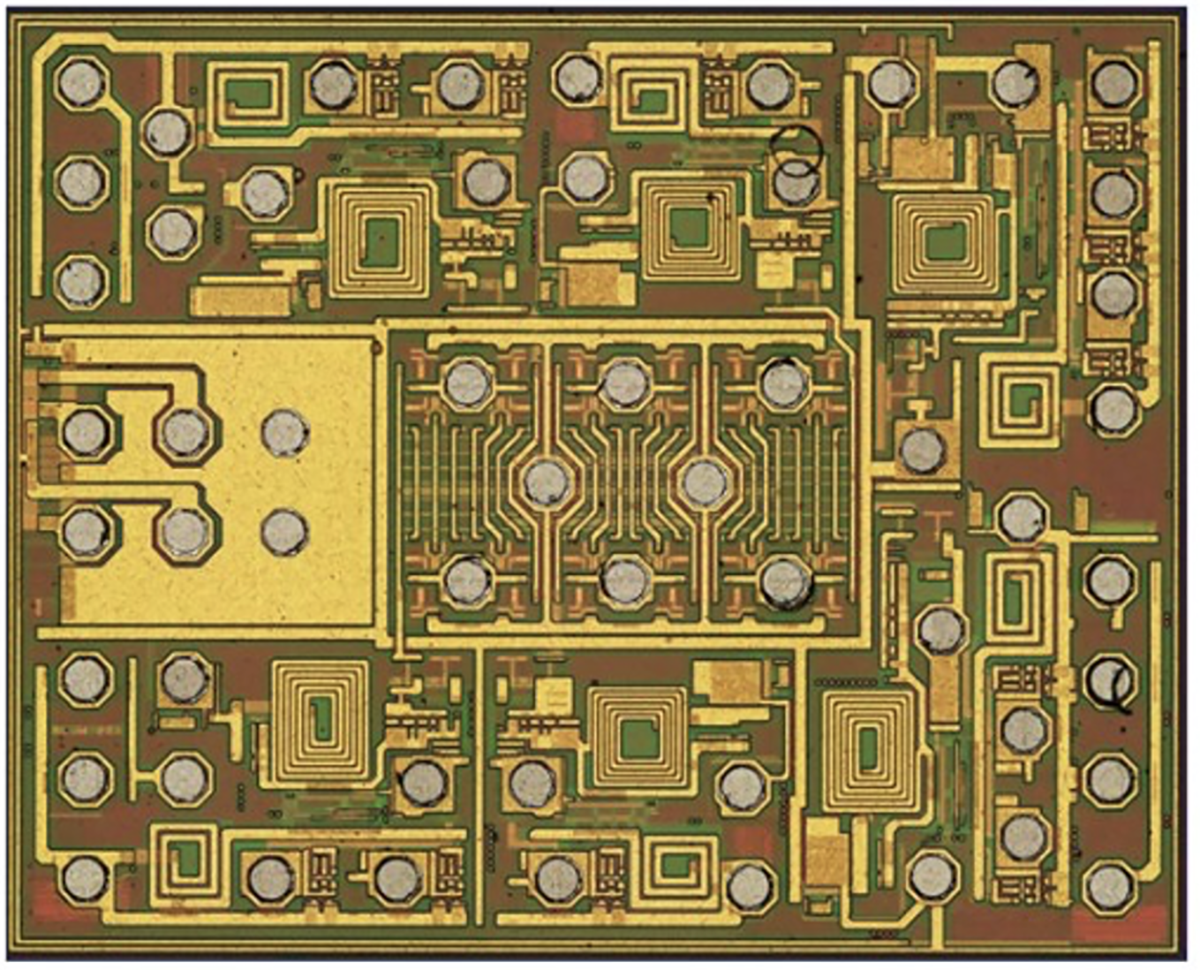

Dla układów z wyprowadzeniami do obudowy typu BGA z “micro-bump” pady mogą być rozmieszczone prawie w dowolnym miejscu na chipie:

Okrągłe “pady” widoczne na chipie do wykonania połączeń typu micro-bump | źródło : Yole Group

Oprogramowanie i technologia RDL stworzone przez imec umożliwia takie przekonfigurowanie wyprowadzeń, by ułatwić połączenie różnych chipów układów scalonych. Ta technika znajduje zastosowanie głównie w montażu 2.5D.

Co to jest D2W?

W zaawansowanych technologiach montażu chipów półprzewodnikowych, D2W oznacza łączenie chipu z płytką półprzewodnikową, najczęściej krzemową (Die-To-Wafer). Jest to proces produkcyjny, w którym pojedyncze chipy układu scalonego są montowane na innym chipie, ale jeszcze przed pocięciem płytki na poszczególne chipy, w celu utworzenia układu wielowarstwowego. Podobny proces łączenia chipu do chipu nazywa się D2D (Die-To-Die), a proces łączenia całych płytek to W2W (Wafer-To-Wafer). Technologia D2W jest używana w zaawansowanym montażu 3D.

Wyżej wspomniane technologie umożliwiają integrację wielu układów scalonych w tzw. chiplet i budowę zintegrowanych całych systemów.

Tłumaczenie i komentarz z wyjaśnianiami: Grzegorz Kamiński

Imec odkrywa sposób na zwiększenie wydajności fotolitografii EUV: wtrysk tlenu podczas wygrzewania po naświetlaniu fotorezystu metalowo-tlenkowego

Imec odkrywa sposób na zwiększenie wydajności fotolitografii EUV: wtrysk tlenu podczas wygrzewania po naświetlaniu fotorezystu metalowo-tlenkowego  Imec przedstawia 7-bitowy przetwornik analogowo-cyfrowy typu slope o częstotliwości 175 GS/s z masywnym przeplotem czasowym

Imec przedstawia 7-bitowy przetwornik analogowo-cyfrowy typu slope o częstotliwości 175 GS/s z masywnym przeplotem czasowym  NanoIC – pilotażowa linia produkcyjna układów scalonych poniżej 2 nm – oficjalnie otwarta w belgijskim imec

NanoIC – pilotażowa linia produkcyjna układów scalonych poniżej 2 nm – oficjalnie otwarta w belgijskim imec