Imec tworzy konsorcjum uniwersyteckie zajmujące się chipami nowej generacji

Centrum badań i innowacji w dziedzinie zaawansowanych technologii półprzewodnikowych w belgijskim Leuven, uruchomiło pierwsze tego rodzaju konsorcjum z udziałem 26 europejskich grup uniwersyteckich, które będą wspólnie pracować nad planem rozwoju technologii wykraczającym poza skalowanie CMOS (CMOS 2.0) [Complementary Metal-Oxide-Semiconductor]. Inicjatywa ta skoncentruje się na automatyzacji projektowania i badaniach nad architekturą chipów nowej generacji. Konsorcjum będzie korzystać z linii pilotażowej NanoIC, przekształcając wiedzę akademicką w innowacje ukierunkowane na przemysł. W przyszłości powstaną podobne konsorcja zajmujące się zaawansowanymi materiałami i alternatywnymi systemami obliczeniowymi.

Większa elastyczność projektowania chipów nowej generacji

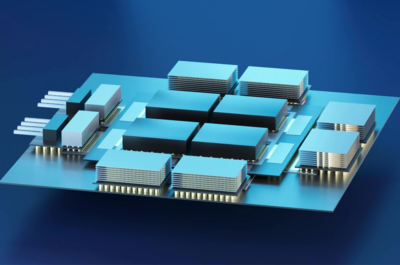

CMOS 2.0 odnosi się do nowego paradygmatu wprowadzonego przez imec, który rozszerza zestaw narzędzi do produkcji chipów poza tradycyjne skalowanie tranzystorów i związane z tym wyzwania. CMOS 2.0 zapewnia większą elastyczność projektowania dzięki wykorzystaniu technologii układania płytek o drobnej ziarnistości w celu poprawy łączności w chipie i zapewnienia większej heterogeniczności technologicznej systemu. Efektem będą dostosowane do potrzeb chipy składające się z wielu warstw ułożonych w trójwymiarowej strukturze, które realizują inteligentnie podzielone funkcje. W ten sposób CMOS 2.0 zapewni zaawansowane, wszechstronne platformy ułożone w stosy 3D, które przesuwają granice wydajności obliczeniowej.

Wprowadzenie tego nowego paradygmatu będzie miało głęboki wpływ na sposób projektowania i optymalizacji architektur obliczeniowych pod kątem przyszłych obciążeń i zastosowań. CMOS 2.0 jest kluczowym czynnikiem wyróżniającym realizację energooszczędnych systemów obliczeniowych nowej generacji i ma wpływ na szeroką gamę zastosowań, od procesorów ogólnego przeznaczenia po wysokowydajne systemy obliczeniowe AI, a nawet dalej, do wbudowanych aplikacji AI na obrzeżach sieci.

Potrzeba wymiany doświadczeń i 26 doktoratów

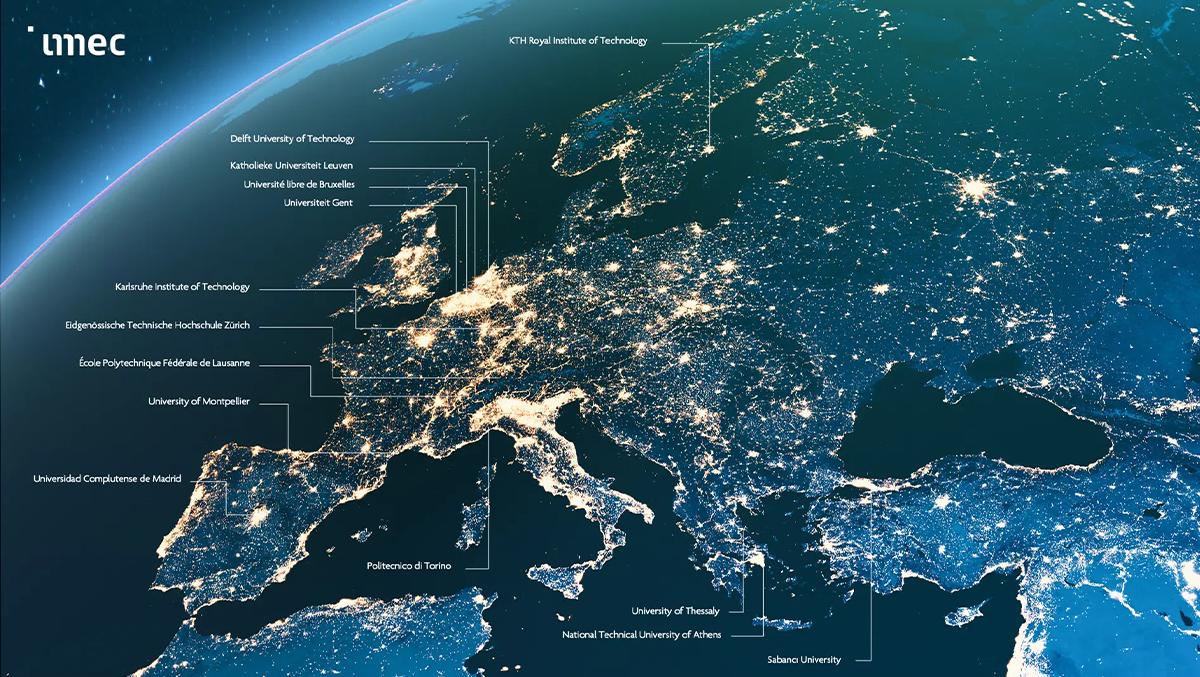

Te strategicznie ważne badania wymagają wzajemnej wymiany doświadczeń między różnymi obszarami ekosystemu. W ramach konsorcjum CMOS 2.0 imec sfinansuje 26 doktoratów. Doktoranci pozostaną na swoich macierzystych uczelniach, w ramach swoich grup badawczych, co pozwoli im czerpać z uzupełniających się dziedzin wiedzy i stymulować wymianę doświadczeń. Uczestniczące w projekcie uczelnie oraz imec wspólnie opracują niezbędną wiedzę specjalistyczną, która stanowi podstawę platform technologicznych CMOS nowej generacji i związanych z nimi architektur obliczeniowych. Ponadto współpraca ta będzie wspierać rozwój kadr i umiejętności w Europie, aby sprostać obecnym i przyszłym potrzebom przemysłu.

– Atrakcyjność koncepcji CMOS 2.0 jest oczywista, ale przeszkody są równie istotne. Wykorzystanie zalet zarówno łączności, jak i heterogenicznej integracji, które umożliwia trójwymiarowe układanie płytek, zmieni każdy etap projektowania i architekturę chipów. Wymaga to połączenia wiedzy specjalistycznej, ścisłej współpracy i koordynacji. Po raz pierwszy imec w zorganizowany sposób zgromadził taką sieć najlepszych europejskich zespołów uniwersyteckich, aby kierować ich wkładem w przyszłą mapę drogową półprzewodników. Cieszymy się, że możemy dalej łączyć wkład akademicki w naszych programach ukierunkowanych na przemysł, aby Europa znalazła się w czołówce badań nad zaawansowanymi technologiami obliczeniowymi – powiedziała Sahar Sahhaf, dyrektor ds. rozwoju partnerstw akademickich.

– To konsorcjum badawcze uniwersytetów ma na celu wprowadzenie technologii CMOS 2.0 do całego procesu projektowania, od automatyzacji projektowania elektronicznego (EDA) aż po architekturę systemową. Jego celem jest pobudzenie szerszego środowiska badawczego i akademickiego do badań nad różnymi aspektami rewolucji CMOS 2.0. Imec odgrywa wyjątkową i kluczową rolę, łącząc badania akademickie z potrzebami przemysłu oraz rozszerzając plan działania w zakresie skalowania technologii dzięki CMOS 2.0 – Mehdi Tahoori, dyrektor techniczny:

Szczególna rola lini pilotażowej NanoIC – szybszy transfer wiedzy i technologii

Szczególne znaczenie ma obecność pilotażowej linii NanoIC prowadzonej przez imec w Leuven i jej decydująca rola we wzmacnianiu konsorcjum akademickiego CMOS 2.0. Najnowocześniejsze narzędzia są osadzone w silnym, opartym na współpracy ekosystemie partnerów przemysłowych. Doktoranci mogą wcześnie zapoznać się z technologiami półprzewodnikowymi nowej generacji, takimi jak logika, pamięć i technologie 3D, dzięki zestawom do projektowania procesów (PDK), które pozwolą im rozwinąć myślenie na poziomie systemowym, zazwyczaj pojawiające się znacznie później w karierze naukowej lub przemysłowej. W ten sposób wypełnia lukę między środowiskiem akademickim a przemysłem, ułatwiając szybki transfer wiedzy i zaawansowanych technologii z laboratoriów badawczych na rynek, wzmacniając w ten sposób przemysł europejski.

Źródło: imec

Konsorcjum uniwersyteckie CMOS 2.0 składa się z 16 uczelni:

- National Technical University of Athens

- Delft University of Technology

- École Polytechnique Fédérale de Lausanne (EPFL)

- Eidgenössische Technische Hochschule Zürich

- Karlsruhe Institute of Technology

- Katholieke Universiteit Leuven

- KTH Royal Institute of Technology

- LIRMM,

- University of Montpellier,

- CNRS

- Politecnico di Torino

- Sabancı University

- Universidad Complutense de Madrid

- Universiteit Gent

- Université libre de Bruxelles

- University of Thessaly

NanoIC otwiera dostęp do pierwszych w historii hybrydowych połączeń między-układowych; zestaw do projektowania (PDK) połączeń typu RDL i D2W

NanoIC otwiera dostęp do pierwszych w historii hybrydowych połączeń między-układowych; zestaw do projektowania (PDK) połączeń typu RDL i D2W  Imec odkrywa sposób na zwiększenie wydajności fotolitografii EUV: wtrysk tlenu podczas wygrzewania po naświetlaniu fotorezystu metalowo-tlenkowego

Imec odkrywa sposób na zwiększenie wydajności fotolitografii EUV: wtrysk tlenu podczas wygrzewania po naświetlaniu fotorezystu metalowo-tlenkowego  NanoIC – pilotażowa linia produkcyjna układów scalonych poniżej 2 nm – oficjalnie otwarta w belgijskim imec

NanoIC – pilotażowa linia produkcyjna układów scalonych poniżej 2 nm – oficjalnie otwarta w belgijskim imec