Grzegorz Kamiński: Może 2 nm technologiczne są większe od 2 nm metrycznie?

Wiele razy słyszałem od różnych ekspertów, że tak naprawdę w tranzystorze technologii 2 nm wszystkie kluczowe wymiary są większe od 2 nm. Widziałem także zdjęcie z firmy ASML produkującej najbardziej zaawansowane maszyny do naświetlania w fotolitografii ze wzorem Rayleigha:

gdzie:

- NA to apertura numeryczna i jej największa wartość dla najlepszych maszyn EUV z ASML wynosi 0,55

- k1 to parametr zależny od wielu czynników a jego minimalna wartość teoretyczna wynosi 0,25. W praktyce w maszynach ASML ta wartość to 0,31-0,33.

- λ – długość fali światła używana w maszynach do fotolitografii. W tych do EUV jest to 13,5nm.

Łatwo policzyć, że teoretycznie minimalna wartość CD = 6 nm, a praktyczna – i taka też jest podawana przez firmę ASML – to 8 nm.

Zdjęcie z firmy ASML ze wzorem Rayleigha na ścianie

Wzór Rayleigha w fotolitografii definiuje teoretyczną granicę rozdzielczości (minimalny wymiar krytyczny, CD – Critical Dimension) układu optycznego, czyli to, jak małe elementy można odwzorować na płytce krzemowej.

Karta ze strony internetowej firmy ASML z kluczowymi parametrami maszyny High-NA EUV typu EXE 5200B

To skłoniło mnie do zadania pytania: Skoro firma podaje że CD to 8 nm, to dlaczego jednocześnie pisze, że ta maszyna jest do technologii sub-2nm?

Czy technologia 2 nm to czysty marketing?

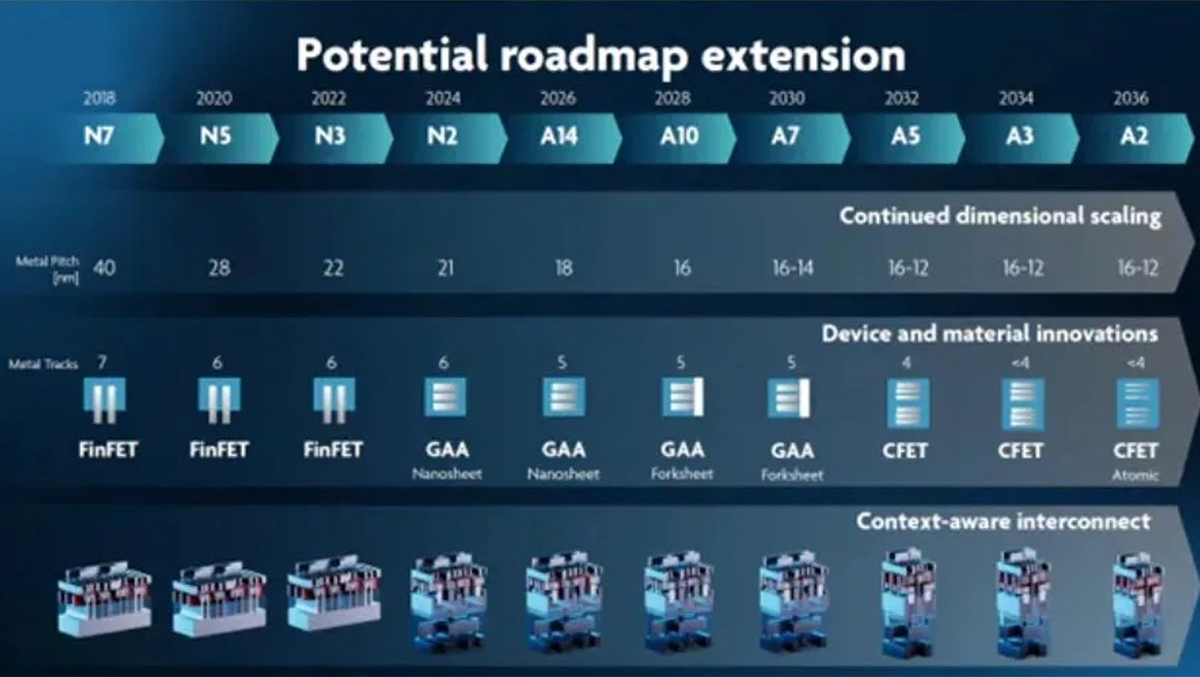

Wg. definicji podanej powyżej, nie jest możliwe odwzorowanie rozmiarów mniejszych niż 8 nm. To do końca nie jest prawda, bo sam pisałem na łamach tego portalu o fotolitografii i jak przełamać tą barierę, np. przez tzw. techniki wielokrotnej ekspozycji ( ang. multi-patterning exposure ). Mimo wszystko jednak to nie jest proste, by na maszynie o minimalnej rozdzielczości 8 nm uzyskać wspomniane 2 nm. A tak naprawdę, to czy rzeczywiście je uzyskujemy? Jest wiele źródeł które mówią że 3 lub 2 nm to tylko marketing a nie rzeczywistość. Moim zdaniem to nie jest czysty marketing, ale też wymiary minimalne także nie są wymagane na poziomie 2 nm. Pewnie niektórzy stwierdzą, że znowu naukowcy czy producenci nas oszukują by zwiększyć swoje zyski. A prawda leży pośrodku, jak zwykle. Wiele marketingu jest w opisie nowych technologii o coraz to mniejszych rozmiarach, ale ma to także swoje głębokie uzasadnienie naukowe i techniczne. Prosty przykład: jak opisać technologie dla tranzystora MOSFET wykonanego w technologii np. 22 nm i tranzystora GAA o tych samych wymiarach? Technologia dla tranzystora GAA jest opisywana mniejszymi wartościami w nanometrach niż dla tranzystora MOSFET w technologii 22 nm. Dlaczego? By móc porównać obie technologie i sprowadzić je do wspólnego mianownika. Konkluzja: zmiana konstrukcji tranzystorów wpłynęła na nazewnictwo technologii. Dobrze ilustruje to rysunek poniżej:

Kamienie milowe obejmujące rozwój tranzystorów GAA i tranzystorów CFET w 2032 r. Odstęp między ścieżkami metalizacji, połączeń pozostanie na poziomie 12–16 nm | źródło: imec, 2024

Tranzystory FinFET i GAA, a w przyszłości CFET powodują, że mówimy już o technologiach sub-nanometrowych (A14 oznacza rozmiar charakterystyczny technologii 1,4nm), ale to są tylko nazwy kolejnych technologii, a nie rzeczywiste rozmiary.

A tak na marginesie, to mamy 2026 i dopiero w tym roku, a na szerszą skalę w 2027 będą dostępne układy scalone wykonane w technologii N2 i A18 (nie pokazanej na tym rysunku). A14 to raczej rok 2028/29, a więc mamy 2-3 lata opóźnienia w stosunku do jeszcze niedawno publikowanych planów rozwoju technologii. To pokazuje, jak trudno jest uzyskać dalszy postęp.

Do technologii na poziomie 22 nm były i są używane standardowe tranzystory lateralne (poziome) MOSFET. W takim przypadku określenie technologii było jednoznacznie kojarzone z najbardziej charakterystyczną cechą takiego tranzystora, czyli długością kanału. Technologia 65 nm oznacza, że długość kanału tranzystora wynosi 65 nm, a technologia 22 nm oznacza dokładnie to samo. Ponieważ tranzystory FinFET i GAA mają inną konstrukcję, to używanie dalej długości kanału np. tranzystorów FinFET do określania nazwy technologii przestało mieć sens, ponieważ tranzystor FinFET o długości kanału 22 nm zachowuje się inaczej, tak jak tranzystor o mniejszej długości kanału. Z tego powodu do określania technologii wprowadzono pojęcie węzła (ang. node). Nie wiem, czy jest inne dobre polskie określenie dla słowa węzeł. To dało możliwość porównywania technologii z różnymi tranzystorami np. FinFET czy GAA. To dlatego w technologii o węźle 10 nm z tranzystorem FinFET, długość kanału i wszystkie wymiary krytyczne mogą być i są większe od wspomnianych 10 nm.

Nowe nazewnictwo w technologii

Tak naprawdę, do technologii 90 nm i o większych rozmiarach, wszystkie elementy tranzystora były przeskalowywanie wg tego samego współczynnika. Czyli dla długości kanału, szerokości metalizacji i odstępów między ścieżkami metalizacji czy wielkości kontaktów metalizacji np. do drenu itd., przy przejściu z 130 nm na 90 nm, technologia była przeskalowywana wg. współczynnika 90/130 = 0,69. Dla technologii 65 nm to przeskalowywanie jest wykonywane wg. różnych współczynników, w zależności od elementu układu scalonego. Inny jest współczynnik skalowania dla kontaktów a inny dla szerokości ścieżek metalizacji. I dlatego, oprócz konstrukcji tranzystorów, ten fakt miał wpływ na wprowadzenie pojęcia węzeł i pewnej umowności w nazewnictwie technologii. Te nowe nazwy technologii to jak określenie kolejnej generacji. Mówimy o Wi-Fi 5 i Wi-Fi 6 i wiemy, że są to kolejne generacje i co w nich zostało zmienione. Tak samo jest w technologiach półprzewodnikowych, ale te nanometry wprowadzają pewne zamieszanie i do końca nie wiemy czy jest mowa o generacji technologii czy o rzeczywistych rozmiarach.

Jak widać wiele czynników spowodowało, że nazwa technologii np. 2 nm nie ma już tak bezpośredniego związku rzeczywistymi wymiarami.

Dla starszych technologii rozmiar ≈ fizyczny wymiar tranzystora (długość kanału), a dla nowych mamy pojęcie “węzeł” (jak ktoś zna lepsze tłumaczenie to proszę je podać) = etykieta kolejnej generacji procesu technologicznego, opisująca ogólną zdolność/poziom technologii, a nie konkretny wymiar.

No i w tym miejscu można by zakończyć ten wywód, ale wydaje mi się, że dobrze by było jeszcze wyjaśnić, skąd się wzięły i dlaczego powstały nowe konstrukcje tranzystorów. To też jest dobry temat na kolejny artykuł.

Kolejne kryterium technologii – liczba milionów tranzystorów na mm2

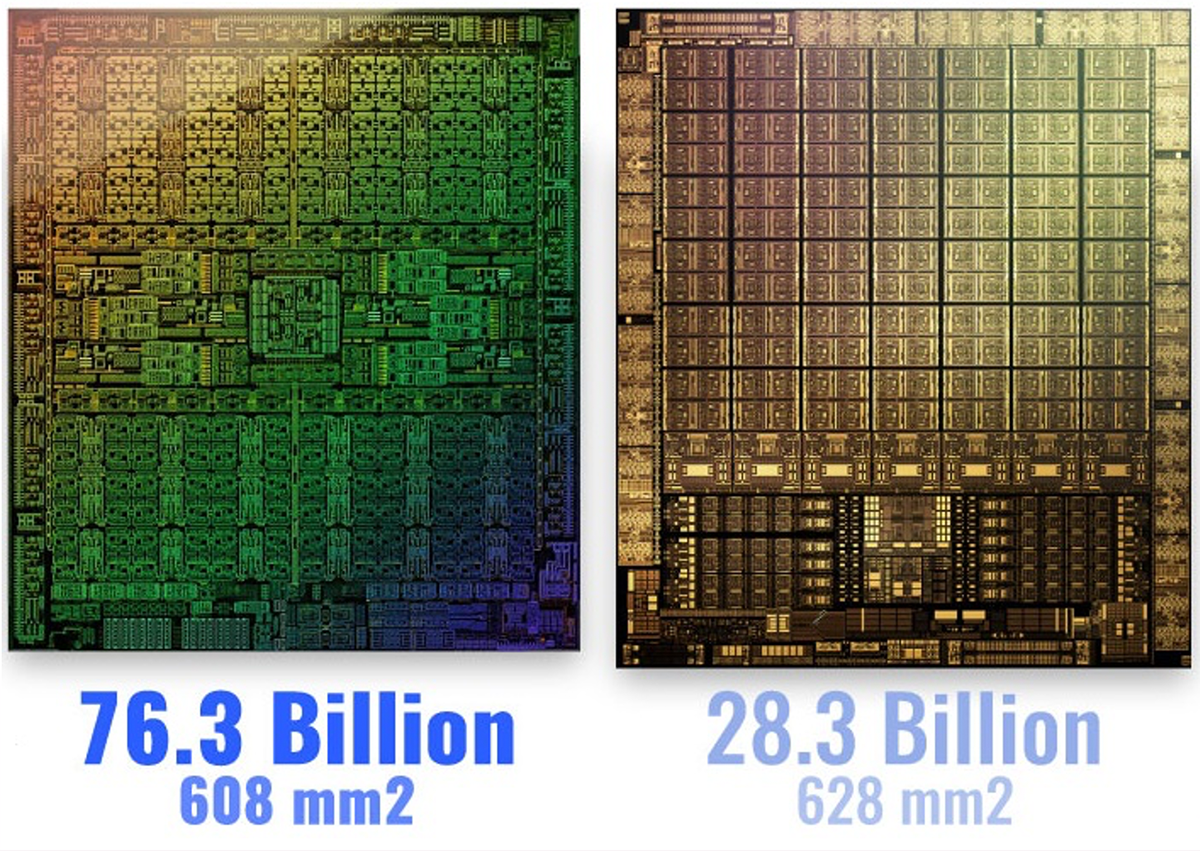

Już kilka razy odwoływałem się do zdjęcia poniżej:

Zdjęcia chipów procesorów dla kart graficznych RTX4000 (z lewej) i dla RTX3060 (z prawej)

- RTX4000 wykonany w technologii 5 nm, zawiera 125 mln tranzystorów na 1 mm2

- RTX3060 wykonany w technologii 8 nm, zawiera tylko 45 mln tranzystorów na 1 mm2

Kryteria technologii to:

- możliwość skalowania

- ilość tranzystorów na jednostkę powierzchni

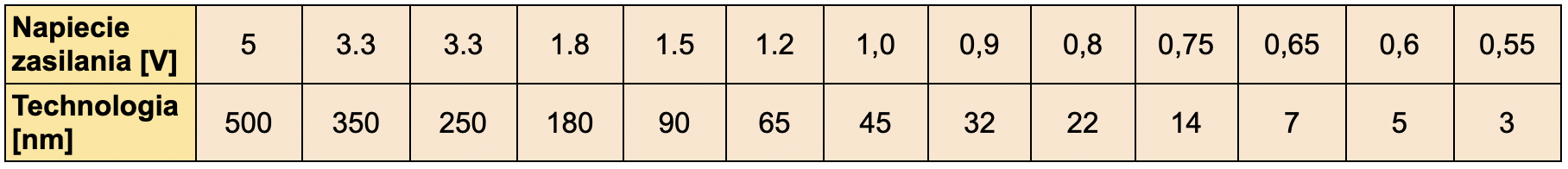

- brakuje trzeciej wartości czyli napięcia zasilania

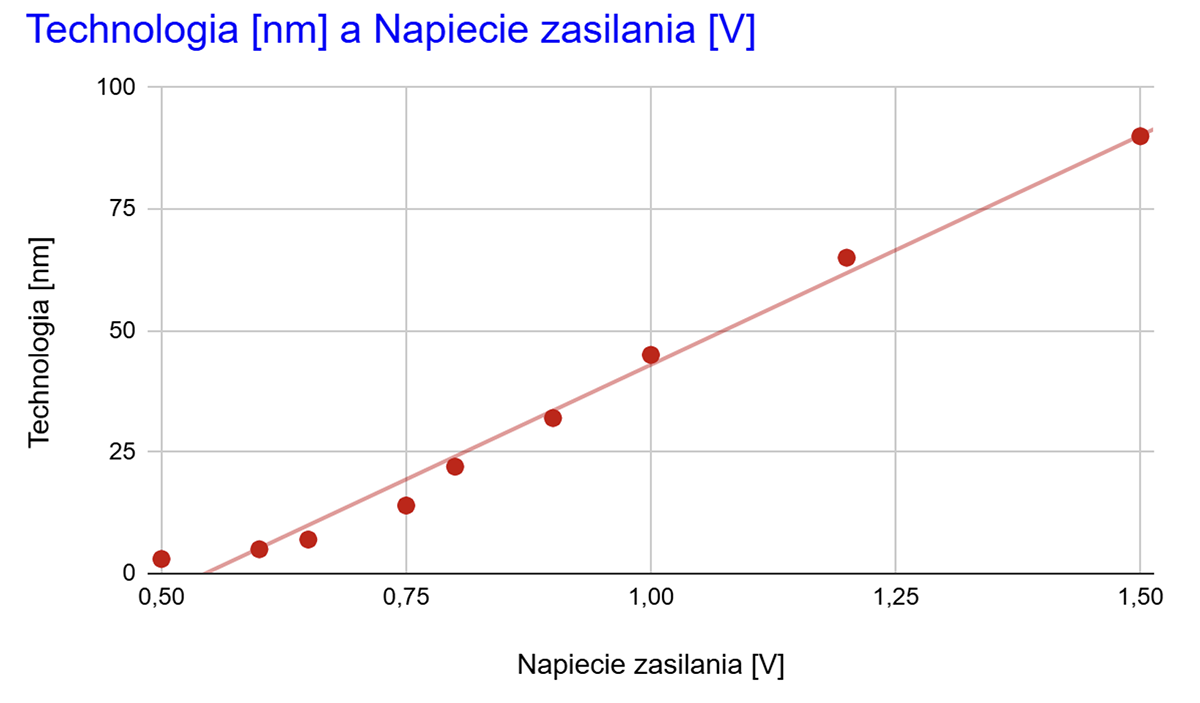

Tabela i wykres poniżej pokazują, jak zmieniało się napięcie zasilania wraz z postępem technologicznym:

Technologia a napięcie zasilania dla technologii tylko do 90 nm

Jak wynika z wykresu, przy skalowaniu tylko liniowym już dawno napięcie zasilania musiałoby być znacznie niższe niż stosowane obecnie.

Mimo, że stale uzyskujemy postęp technologiczny, to już z obniżaniem napięcia zasilania musimy się zatrzymać, bo w przeciwnym razie nie będziemy mogli skutecznie kontrolować tych napięć. Rozrzut technologiczny np. dla napięcia progowego tranzystora osiągnąłby wartość napięcia zasilania, a to uniemożliwiłoby jakąkolwiek kontrolę działania układu scalonego.

Kolejny problem to moc, a co za tym idzie wydzielanie ciepła w układzie. Gęstość upakowania komponentów rośnie i trzeba poradzić sobie z odprowadzaniem ciepła. Ten czynnik także ogranicza skalowanie rozmiarów w dół.

Pewnie można by jeszcze wymienić kilka innych czynników powodujących, że pojęcie „technologia 2 nm” nie oznacza, iż fizycznie/metrycznie wymiary elementów tranzystora mają wspomniane 2 nm. Zwykle fizyczne rozmiary oscylują w zakresie 10-20 nm, ale jakie to ma znaczenie? Technologia nazywa się 2 nm, by móc kolejne generacje układów scalonych porównywać ze sobą.

Grzegorz Kamiński: Trzech czy czterech dostawców najbardziej zaawansowanych chipów?

Grzegorz Kamiński: Trzech czy czterech dostawców najbardziej zaawansowanych chipów?  Grzegorz Kamiński: Lead Time z punktu widzenia producenta podzespołów półprzewodnikowych

Grzegorz Kamiński: Lead Time z punktu widzenia producenta podzespołów półprzewodnikowych  Grzegorz Kamiński: Serce fabryki podzespołów półprzewodnikowych – cleanroom

Grzegorz Kamiński: Serce fabryki podzespołów półprzewodnikowych – cleanroom