Freescale Kinetis L – Corteksy (prawie) nie potrzebujące prądu

Metod minimalizacji poboru mocy zasilającej przez mikrokontrolery jest kilka. Od doboru technologii zaczynając, na odpowiednich algorytmach pracy kończąc. Rewelacyjnymi osiągnięciami w zakresie optymalizacji poboru mocy przez mikrokontrolery z rdzeniem ARM Cortex-M0+ i ARM Cortex-M4 może poszczycić się Renesas, jeden z najbardziej liczących się producentów elementów elektronicznych. Rodzina układów Kinetis L została opracowana specjalnie dla aplikacji o szczególnie ostrych wymaganiach dotyczących poboru prądu. Układy te są idealną drogą migracji z mikrokontrolerów 8-bitowych do nieporównywalnie wydajniejszych ARM-ów.

KL0 – podstawowa linia MCU rodziny Kinetis L

Mikrokontrolery Kinetis L tworzą jedną rodzinę, w której wyróżniono kilka linii charakteryzujących się nieco odmiennymi parametrami i funkcjonalnością, spełniającymi jednak podstawowe wymagania stawiane całej rodzinie. Pierwszą z nich – KL0 – tworzą najprostsze układy, nadające się doskonale do rozpoczęcia pracy z rodziną Kinetis L. Ważną ich cechą, jako środka migracji do mikrokontrolerów nowej generacji jest kompatybilność wyprowadzeń z 8-bitowymi mikrokontrolerami rodziny S08P. Wszystkie narzędzia wykorzystywane do tworzenia aplikacji, zarówno sprzętowe, jak i programowe, są takie same, jak układów następnych, bardziej zaawansowanych linii.

Grupa mikrokontrolerów KL0 zawiera układy z pamięcią Flash od 8 kB, produkowanych w obudowach QFN24 4×4 mm, aż po układy z pamięcią 32 kB w obudowach LQFP48. Wszystkie mikrokontrolery linii KL0 zawierają podstawowe peryferia (rys. 1) i charakteryzują się ultra niskim poborem mocy.

Rys. 1. Schemat blokowy mikrokontrolera Kinetis L KL0

KL1 – linia MCU Kinetis L przeznaczona do typowych zastosowań

Mikrokontrolery tej grupy zachowują kompatybilność sprzętową i programową z innymi układami rodziny Kinetis L, dysponują jednak większymi pamięciami i bardziej rozbudowanymi peryferiami analogowymi oraz komunikacyjnymi w porównaniu z KL0. Są to mikrokontrolery zgodne z rodziną K10 bazującą na rdzeniu ARM Cortex-M4. Schemat blokowy układów grupy K1 przedstawiono na rys. 2. Dostępne są mikrokontrolery z pamięcią od 32 do 256 kB, produkowane w obudowach QFN32 5×5 mm i LQFP80.

Rys. 2. Schemat blokowy mikrokontrolera Kinetis L KL1

Dwukierunkowy przełącznik GaN klasy 650 V do falowników energii słonecznej, centrów danych AI i innych zastosowań

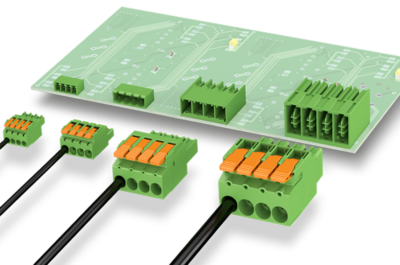

Dwukierunkowy przełącznik GaN klasy 650 V do falowników energii słonecznej, centrów danych AI i innych zastosowań  Nowe generacje złączy: innowacyjne metody połączeń w elektronice

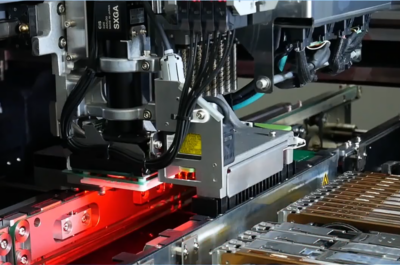

Nowe generacje złączy: innowacyjne metody połączeń w elektronice  Zaawansowane urządzenia do montażu SMT na przykładzie automatu P&P RS-2 – analiza technologiczna i zastosowania w nowoczesnej produkcji elektroniki

Zaawansowane urządzenia do montażu SMT na przykładzie automatu P&P RS-2 – analiza technologiczna i zastosowania w nowoczesnej produkcji elektroniki