Testowanie – Kiedy „Boundary-Scan” ma sens?

Gdzie tkwi problem?

Czy współczesna elektronika upraszcza się, czy też komplikuje? Przewrotnie można pokusić się o stwierdzenie, że nie ma jednoznacznej odpowiedzi na tak postawioną kwestię. Z jednej strony stosujemy coraz bardziej skomplikowane, coraz szybsze układy scalone i na ich bazie tworzymy coraz bardziej zaawansowane technicznie aplikacje. Z drugiej strony porównując płytki elektroniczne dzisiejszych urządzeń, zbudowane na małej powierzchni z kilku dosłownie kostek, z dawnymi konstrukcjami wielkości szafy mamy wrażenie prostoty. Z jednej strony składamy urządzenia z gotowych sprawdzonych zintegrowanych „klocków”. Z drugiej strony przestajemy panować nad tym jak te „klocki” w środku działają. Produkując urządzenia elektroniczne musimy jednak te współczesne „proste” konstrukcje testować. I tu znowu z jednej strony przy wysokim uzysku produkcyjnym układów scalonych mamy w zasadzie gwarancje prawidłowego działania całych bloków funkcjonalnych i wydawać by się mogło niewiele poza tym do weryfikacji, a z drugiej mamy piętrzące się trudności przy realizacji jakichkolwiek testów. Wielowarstwowe obwody drukowane, obudowy BGA, gęstość upakowania ścieżek i wyprowadzeń wykluczają tradycyjne środki jak klasyczne przyrządy pomiarowe, testery ostrzowe itp. Albo nie ma możliwości dotarcia do punktu pomiarowego, albo człowiek nie jest w stanie ogarnąć takiej ilością sygnałów. Co robić? Ograniczać się tylko do optycznej weryfikacji jakości montażu? Ograniczać się tylko do sprawdzenia funkcjonalnego urządzenia – działa nie działa? Taka praktyka jest już zbyt często stosowana i praktycznie testowanie jest przerzucane na klienta końcowego. On coraz częściej po zakupie znajduje wady ukryte towaru i udaje się do serwisu po wymianę podzespołów lub upgrade oprogramowania. Nikogo to już nie oburza o ile nie grozi poważnym niebezpieczeństwem. Nawet w wydawać by się mogło newralgicznym przemyśle samochodowym co chwila mamy do czynienia z wezwaniami do serwisu. Są jednak obszary elektroniki gdzie błąd jest niedopuszczalny, gdzie często producent musi wydać certyfikat mając pewność, że urządzenie zostało w pełni przetestowane. Maksymalne pokrycie testami staje się więc kluczowym zadaniem na produkcji urządzeń elektroniki lotniczej, wojskowej, medycznej, samochodowej, kolejowej itp. W tych obszarach trzeba mieć maksymalną pewność, że urządzenie będzie działało prawidłowo również w rzadko występujących i często nie testowanych sytuacjach awaryjnych. W artykule zaprezentowano technologię (B-S) zwaną też ścieżką krawędziową. Jest to metoda testowania pakietów i urządzeń elektronicznych na wszystkich etapach procesu produkcji – w fazie projektowania i w fazie wytwarzania. Jest to metoda pozwalająca zautomatyzować procesy generowania testów, ich realizacji i diagnostyki uszkodzeń. Jest to, uniwersalna technologia, której wdrożenie w firmie wprowadza nową jakość testowania dla różnych produkowanych urządzeń.

Retoryczne są pytania, czy jesteśmy w stanie na produkcji w pełni zweryfikować urządzenie i czy istnieje jakaś jedna uniwersalna metoda testowania urządzeń elektronicznych? Niestety zawsze trzeba stosować różne komplementarne działania, a planować je już na etapie projektowania aby nie tworzyć nietestowalnych urządzeń. Prezentowany też nie jest lekarstwem na całe zło. Na pewno nie zastąpi dobrze zaprojektowanego dedykowanego dla danej aplikacji testu funkcjonalnego wykonywanego często w oparciu o specjalnie zaprojektowane stanowisko i specjalnie wykonane przyrządy. Nie zastąpi też testerów optycznych AOI i rentgenowskich AXI. Testy funkcjonalne mają jednak ograniczone możliwości diagnostyki, a optyczne i rentgenowskie pozwalają tylko zweryfikować jakość lutowania. stanowi znakomite uzupełnienie tych klasycznych metod, w szczególności przy braku dostępu do punktów pomiarowych (obudowy BGA, druki wielowarstwowe). jest bowiem uniwersalną technologią automatycznego generowania, przeprowadzania testów i diagnozowania uszkodzeń, która po wdrożeniu bez dodatkowych inwestycji może być stosowana w kolejnych projektach. to nowa jakość w firmie i wyższa jakość jej produktów.

IEEE1149.1

Tytułowa norma to klucz do stosowania . Praktycznie możemy bowiem rozważać tę technologię, gdy w projekcie mamy co najmniej 2-3 układy scalone kompatybilne z tym standardem. Są to najczęściej mikrokontrolery (np. ARM) i programowalne struktury logiczne PLD i FPGA. Od razu trzeba też rozwiać wątpliwości i stwierdzić, że już pojedyncze układy IEEE1149.1 pozwalają testować szerszy zakres niż one same, a mianowicie pozwalają testować całe ich otoczenie. Mylna jest często wyrażana opinia – „Boundary-Scan jest nie dla nas bo mamy na pakiecie tylko pojedyncze kompatybilne układy”.

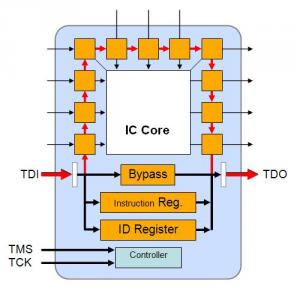

Rys.1. Struktura układu scalonego

z mechanizmem Boundary-Scan

Kompatybilność z normą IEEE1149.1 oznacza, że układ jest wyposażony w mechanizm , który z punktu widzenia pojedynczego układu pozwala buforować tzn. odłączać/przyłączać poszczególne wyprowadzenia od/do struktury układu i konfigurować je w rejestr szeregowy z wejściem TDI i wyjściem TDO. Te komórki buforowe są sterowane wewnętrznie przez tzw. TAP (Test Access Port) za pośrednictwem linii TMS, TCK i rejestru IR (Instruction Register). Każdy taki układ na pakiecie jest identyfikowany poprzez ID i może być włączony w łańcuch testowy na pakiecie. Przy czym w trakcie testów poszczególne układy mogą być pomijane w łańcuchu poprzez rejestr BYPASS.

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  Niewidzialna przewaga. Jak technologia zmienia polską armię

Niewidzialna przewaga. Jak technologia zmienia polską armię