Optymalizacja zasilania układów FPGA

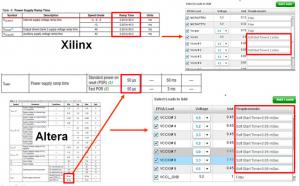

FPGA Power Architect uwzględnia przy tworzeniu projektów również wymaganie odnośnie łagodnego rozruchu.

Rys. 4.

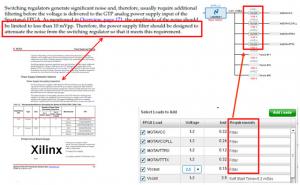

Urządzenia FPGA wymagają filtrowania sygnału na poszczególnych szynach zasilających w celu zminimalizowania przydźwięków. Powyższe wymagania są uwzględniane w projekcie.

Rys. 5.

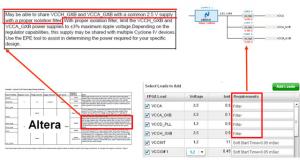

Inne niepowtarzalne możliwości jak np. możność współdzielenia szyny zasilającej po dodaniu odpowiedniego filtra są również uwzględnione w procesie projektowania.

Rys. 6.

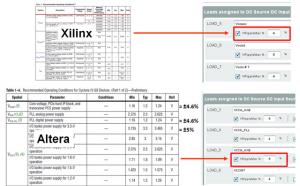

Ograniczenia układów FPGA takie jak całkowita tolerancja napięciowa są również uwzględnione i udostępnione użytkownikowi do konfiguracji.

Rys. 7.

Dołożyliśmy starań by tworzenie zoptymalizowanego zasilacza było tak proste jak to możliwe przy uwzględnieniu wszystkich wymagań dla poszczególnych szyn zasilających wybrany układ.

Pierwszym krokiem jest wybranie z listy preferowanego układu FPGA. Wybór ten powoduje automatyczne wczytanie specyfikacji zasilania oraz szablonu szyn zasilania. Użytkownik może zmieniać charakterystyki poszczególnych szyn oraz np. włączać lub wyłączać poszczególne moduły wejścia/wyjścia.

Szyny zasilające, które pozostaną po kliknięciu zielonego przycisku Add Loads będą podstawą do następnego kroku – konfiguracji źródeł zasilania.

Rys. 8.

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485