NXP PCA9515: ekspander magistrali I2C/SMbus

Układ PCA9515 jest scalonym ekspanderem magistrali I2C i SMbus. Jego zadanie polega na usunięciu części ograniczeń związanych z liczbą układów, które mogą być dołączone jednocześnie do linii magistrali oraz z maksymalną długością linii SCL i SDA.

Magistrala I2C jest powszechnie stosowana we współczesnych urządzeniach elektronicznych, w których spełnia zazwyczaj rolę lokalnej magistrali komunikacyjnej. Do współpracy z magistralą I2C (i jej nieco zmodyfikowaną wersją o nazwie SMbus) jest przystosowanych wiele typów układów peryferyjnych oraz wszystkie współczesne mikrokontrolery i mikroprocesory.

| Jak łączyć różnonapięciowe magistrale I2C? Dostępny jest opis projektu dostępny opis projektu interfejsu pozwalającego łączyć segmenty magistral I2C zasilane napięciami o różnych wartościach. |

Właściwości układu PCA9515:

|

Najpoważniejszym ograniczeniem „rozmiarów” magistrali jest jej maksymalna pojemność obciążająca jej linie, będąca sumą pojemności ścieżek i pojemności wejściowej dołączonych układów. Dopuszczalna łączna pojemność obciążająca to 400 pF i parametr ten ogranicza zarówno maksymalną długość samej magistrali I2C jak i liczbę układów scalonych, które mogą być do niej dołączone. Układ PCA9515 pozwala zminimalizować to ograniczenie, pełniąc rolę mostka separującego główną magistralę od dodatkowych gałęzi, dzięki czemu układy dołączane do nowych gałęzi magistrali nie obciążają magistrali głównej. Ponieważ układ PCA9515 jest „przeźroczysty” dla sygnałów I2C i nie wymaga żadnego dodatkowego adresowania, układy obydwu części widzą się tak, jakby były dołączone do logicznie jednej samej magistrali I2C.

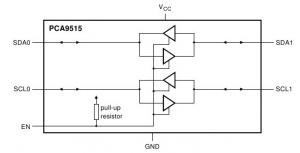

Na rysunku 1 przedstawiono wewnętrzną strukturę układu PCA9515, a na rysunku 2 schemat elektryczny testowanego zestawu. Układ wyposażono w dwa dwukierunkowe kanały: jeden dla linii SDA i jeden dla linii SCL. Sygnał zegarowy SCL magistrali jest generowany tylko przez układ nadrzędny master a dzięki dwukierunkowości linii SCL w układzie PCA9515, system w którym zastosowano ten układ może mieć kilka masterów dołączonych w dowolnych miejscach systemu. Pewnym ograniczeniem aplikacyjnym prezentowanego układu jest brak możliwości kaskadowego łączenia kolejnych układów PCA9515 jeden za drugim. Można natomiast podłączyć kilka układów PCA9515 do głównej magistrali I2C (równolegle).

Rys. 1. Schemat blokowy układu PCA9515

| SMbus a I2C Magistrala SMBus (System Management Bus) jest odporniejszą na zakłócenia wersją magistrali szeregowej I2C z wprowadzoną w protokole komunikacyjnym kontrolą błędów i awizowaniem hosta. Magistrala I2C została początkowo opracowana przez Philipsa (obecnie NXP) do łączności pomiędzy układami scalonymi, a SMBus przez firmę Intel do komunikacji w zarządzaniu pracą systemów komputerowych. W warstwie sprzętowej SMBus przewidziano trzecią linię sygnałowa – SMBAlert – która pozwala układom podrzędnym zgłaszać przerwania do hosta systemowego. |

Rys. 2. Schemat elektryczny zestawu testowego

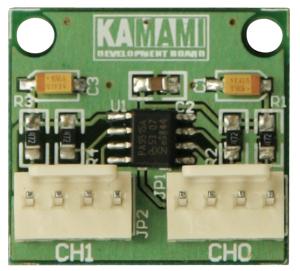

Na fotografii 3 pokazano wygląd zmontowanego zestawu testowego. Wartości rezystorów R1…R4 należy dobrać zgodnie z wytycznymi przedstawionymi w dokumencie SMbus and I2C Design lub nocie aplikacyjnej AN255 firmy NXP (do pobrania na końcu artykułu).

Fot. 3. Wygląd zestawu testowego z układem PCA9515

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii