Freescale Coldfire i Kinetis od środka

System zegarowy

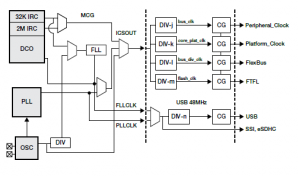

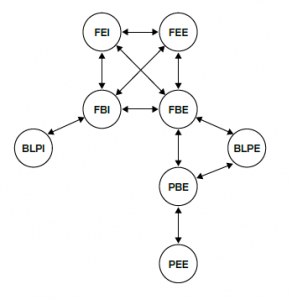

System zegarowy generuje sygnały zegara konieczne do taktowania rdzenia, peryferiów platformy (USB, DMA) i innych peryferiów ogólnego przeznaczenia. Sercem tego systemu jest wielozadaniowy generator zegara (Multi-purpose Clock Generator, MCG), który steruje procesem generacji zegarów. Osobny układ podziału zegara pozwala na ułamkowe dzielenie pojedynczych sygnałów zegarowych i ich optymalizację pod kątem pracy z mniejszym zużyciem energii. W zależności od źródła sygnału zegarowego i wymaganych szybkości zegarów systemowych, MCG może pracować w jednym z ośmiu trybów. Diagram stanów przedstawiony na rysunku 30 pokazuje te tryby, a ich dokładny opis zaprezentowano w tabeli 11.

Rys. 29. Schemat blokowy systemu zegarowego

Rys. 30. Diagram stanów generatora MCG

Tab. 11. Zestawienie podstawowych zalet systemu zegarowego

| Kluczowe cechy | Korzyści dla użytkownika |

| Wewnętrzne źródła referencyjne niskiej i wysokiej częstotliwości do generacji zegara systemowego | Przy pominięciu zewnętrznego kwarcu projektowany system może być tańszy |

| Możliwość pracy z pętlą PLL lub FLL (Frequency-Locked Loop) | MCG można używać w trybie PLL lub FLL. Tryb PLL pozwala osiągnąć niższy jitter |

| Układy zabezpieczania przed rozsynchronizowaniem (loss-of-lock) lub stratą sygnału zegarowego (loss-of-clock) | W zależności od stanu źródła zegarowego MCG może zostać wystawione przerwanie lub nastąpić reset systemu |

Tab. 12. Opis trybów pracy generatora zegara MCG

| Tryb | Opis |

| FLL Engaged Internal (FEI) | W tym trybie, wyjście MCGOUT jest wyprowadzane z zegara FLL (DCOCLK), sterowanego wewnętrznym zegarem referencyjnym (32 kHz IRC*). Pętla FLL ustawi DCO zgodnie ze współczynnikiem FLL, kontrolowanym za pomocą bitów DRS[1:0] i DMX32, mnożąc jego wartość przez wartość częstotliwości wewnętrznej (32 kHz). W trybie FEI, jeśli mikrokontroler pracuje w trybie low-power, pętla PLL jest wyłączona, chyba że ustawiony jest PLLCLKEN. |

| FLL Engaged External (FEE) | W tym trybie, wyjście MCGOUT jest wyprowadzane z zegara FLL (DCOCLK), sterowanego zewnętrznym zegarem referencyjnym. Pętla FLL ustawi częstotliwość DCO zgodnie ze współczynnikiem FLL, kontrolowanym za pomocą bitów DRS[1:0] i DMX32, mnożąc jego wartość przez wartość zewnętrznej częstotliwości referencyjnej, zgodnie z ustawieniami MCGC1[FRDIV] i MCGC2[RANGE]. W trybie FEE, jeśli mikrokontroler pracuje w trybie low-power, pętla PLL jest wyłączona, chyba że ustawiony jest PLLCLKEN. |

| FLL Bypassed Internal (FBI) | W tym trybie, wyjście MCGOUT jest wyprowadzane z zegara FLL (DCOCLK), sterowanego albo wolnym (32 kHz IRC), albo szybkim (2 MHz IRC) wewnętrznym zegarem referencyjnym, co wybierane jest za pomocą bitu IRCS. Pętla FLL jest włączona, ale jej wyjście nie jest używane. Tryb ten jest przydatny, aby pozwolić pętli FLL uzyskać docelową częstotliwość, podczas gdy MCGOUT jest sterowane z zegara wewnętrznego wybranego za pomocą IRCS. Zegar FLL (DCOCLK) jest sterowany wolnym zegarem wewnętrznym (32 kHz IRC), a częstotliwość zegara DCO jest ustalana zgodnie z mnożnikiem, ustawianym za pomocą bitów DRS[1:0] i DMX32 (jego wartość jest mnożona przez częstotliwość wewnętrznego zegara referencyjnego). W trybie FBI, jeśli mikrokontroler pracuje w trybie low-power, pętla PLL jest wyłączona, chyba że ustawiony jest PLLCLKEN. |

| FLL Bypassed External (FBE) | W tym trybie, wyjście MCGOUT jest wyprowadzane z zewnętrznego zegara referencyjnego. Pętla FLL jest włączona, ale jej wyjście nie jest używane. Tryb ten jest przydatny, aby pozwolić pętli FLL uzyskać docelową częstotliwość, podczas gdy MCGOUT jest sterowane z zewnętrznego zegara referencyjnego. Zegar FLL (DCOCLK) jest sterowany zegarem zewnętrznym, a częstotliwość zegara DCO jest ustalana zgodnie z mnożnikiem, ustawianym za pomocą bitów DRS[1:0] i DMX32 (jego wartość jest mnożona przez częstotliwość wewnętrznego zegara referencyjnego). W trybie FBE, jeśli mikrokontroler pracuje w trybie low-power, pętla PLL jest wyłączona, chyba że ustawiony jest PLLCLKEN. |

| PLL Engaged External (PEE) | W tym trybie, wyjście MCGOUT jest wyprowadzane z zegara PLL, sterowanego zewnętrznym zegarem referencyjnym. Częstotliwość zegara PLL jest ustalana zgodnie ze współczynnikiem, ustawianym za pomocą bitu MCGC6[VDIV], przez który mnożona jest zewnętrzna częstotliwość referencyjna, co ustawia się przez MCGC5[PRDIV]. Jeśli mikrokontroler pracuje w trybie low-power, pętla FLL jest wyłączona. |

| PLL Bypassed External (PBE) | W tym trybie, wyjście MCGOUT jest wyprowadzane z zewnętrznego zegara referencyjnego. Pętla PLL jest włączona, ale jej wyjście nie jest używane. Tryb ten jest przydatny, aby pozwolić pętli PLL uzyskać docelową częstotliwość, podczas gdy MCGOUT jest sterowane z zewnętrznego zegara referencyjnego. Częstotliwość zegara PLL jest ustalana zgodnie ze współczynnikiem, ustawianym za pomocą bitu MCGC6[VDIV], przez który mnożona jest zewnętrzna częstotliwość referencyjna, co ustawia się przez MCGC5[PRDIV]. Jeśli mikrokontroler pracuje w trybie low-power, pętla FLL jest wyłączona. |

| Bypassed Low-Power Internal (BLPI) | W tym trybie, wyjście MCGOUT jest wyprowadzane z wewnętrznego zegara referencyjnego. Pętle FLL i PLL są wyłączone (nawet jeśli bit PLLCLKEN jest ustawiony na 1). |

| Bypassed Low-Power External (BLPE) | W tym trybie, wyjście MCGOUT jest wyprowadzane z zewnętrznego zegara referencyjnego. Pętle FLL i PLL są wyłączone (nawet jeśli bit PLLCLKEN jest ustawiony na 1). |

*IRC – Internal Reference Clock (wewnętrzny zegar referencyjny)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485