Freescale Coldfire i Kinetis od środka

Interfejsy zewnętrzne

Rodziny mikrokontrolerów Kinetis obsługują wiele zewnętrznych interfejsów, takich jak: kontroler DRAM, zewnętrzny interfejs magistralowy FlexBus czy kontroler pamięci Flash typu NAND. Mikrokontrolery ColdFire+ rodzin Qx i Jx są z kolei wyposażone w zewnętrzny interfejs magistralowy Mini FlexBus.

Kontroler DRAM

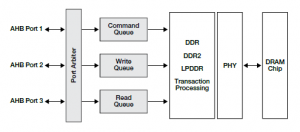

Kontroler pamięci DRAM umożliwia użytkownikom podłączenie do mikrokontrolera pamięci DRAM o dużej pojemności. Oznacza to, że projektowane systemy nie są ograniczone pojemnością wewnętrznej pamięci SRAM, co otwiera wiele nowych możliwości. Podstawowe charakterystyki tego bloku to:

- umożliwienie mikrokontrolerowi pracy w zastosowaniach wymagających dostępu do dużych ilości pamięci – obsługa do 512 MB pamięci zewnętrznej,

- 8- i 16-bitowe zewnętrzne magistrale danych,

- maksymalna częstotliwość (zegara/danych) 150/300 MHz,

- obsługa pamięci typów: DDR, DDR2 i LPDDR,

- praca asynchroniczna dzięki niezależnej pętli PLL,

- obsługa dynamicznego „zakończenia w układzie” (On-Die Termination, ODT), zarówno w urządzeniu hostującym, jak i w samej pamięci DRAM,

- obsługa jednej linii chip select i do ośmiu banków pamięci,

- obsługa pakietów (burst) 16- i 32-bajtowych, niezależne taktowanie linii bajtu (byte lane) i bardzo szybkie odzyskiwanie synchronizacji, pozwalające na uproszczenie schematu płytki,

- obsługa trybów oszczędzania energii.

Rys. 40. Kontroler pamięci DRAM

Magistrale Mini FlexBus oraz FlexBus

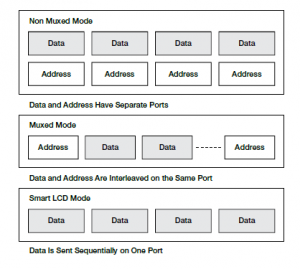

Interfejs Mini FlexBus, w który wyposażone są układy rodziny ColdFire+, został zaprojektowany do podłączenia maksymalnie dwóch urządzeń zewnętrznych. Interfejs FlexBus, występujący w mikrokontrolerach Kinetis pozwala natomiast na podłączenie maksymalnie sześciu urządzeń. Każda z wersji ma porty 8-, 16- i 32-bitowe, z konfiguracją pozwalającą na multipleksację adresów i magistral danych lub jej brak. Podstawowe cechy tych interfejsów to:

- transfery wieloliniowe: bajt, słowo 2-bajtowe (word), słowo 4-bajtowe (longword) lub 16-bajtowe,

- programowalne transfery pakietowe (burst) lub bez pakietowania (burst-inhibited), do ustawienia osobno dla każdej linii chip select i każdego kierunku transmisji,

- automatyczne potwierdzenia (Auto-acknowledge):

- główny licznik oczekiwania (wait state counter) odliczający maks. do 63 taktów zegara,

- opcjonalny drugi licznik oczekiwania,

- przydatne przy komunikacji z pamięciami typu burst mających długi czas dostępu do pierwszej porcji danych, ale potrafiących następne dane dostarczać szybciej,

- programowalny czas ustalania adresu w odniesieniu do potwierdzenia żądania chip select,

- programowalny czas utrzymania adresu w odniesieniu do odrzucenia żądania chip select i kierunku transmisji.

Tab. 15. Zestawienie najważniejszych cech magistrali FlexBus i kontrolera DRAM

| Peryferium | Kluczowe cechy | Korzyści dla użytkownika |

| FlexBus | Transfery: 8-, 16-, 32- i 128-liniowe | Zwiększenie przepustowości |

| Programowalne transfery pakietowe (burst) lub bez pakietowania (burst-inhibited), do ustawienia osobno dla każdej linii chip select i każdego kierunku transmisji | Zoptymalizowane ścieżki ruchu dla każdego klienta podłączonego do magistrali | |

| Automatyczne potwierdzenia (Auto-acknowledge) | Zwiększenie elastyczności i obniżenie kosztów, dzięki możliwości bezpośredniego podłączania wielu różnych urządzeń zewnętrznych | |

| Programowalny czas ustalania adresu | ||

| Programowalny czas utrzymania adresu | ||

| Kontroler DRAM | Obsługa pamięci DDR, DDR2 i LPDDR | Możliwość osiągnięcia kompromisu między wydajnością a zużyciem energii |

| Praca asynchroniczna dzięki niezależnej pętli PLL | Możliwość niezależnego ustawienia częstotliwości pracy pamięci DRAM | |

| Obsługa pakietów (burst) 16- i 32-bajtowych, niezależne taktowanie linii bajtu (byte lane) i bardzo szybkie odzyskiwanie synchronizacji | Uproszczenie schematu płytki drukowanej i doboru elementów | |

| Obsługa trybów low-power | Zmniejszenie całkowitego zużycia energii systemu |

FlexBus obsługuje połączenia z:

- pamięciami Flash,

- inteligentnymi wyświetlaczami LCD,

- układami FPGA,

- pamięciami SRAM,

- pamięciami PROM,

- pamięciami EPROM,

- pamięciami EEPROM.

Rys. 41. Tryby pracy magistrali FlexBus

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485