Freescale Coldfire i Kinetis od środka

Tab. 9. Zestawienie podstawowych zalet peryferiów analogowych

| Peryferium | Kluczowe cechy | Korzyści dla użytkownika |

| 16-bitowy przetwornik A/C |

|

|

|

|

|

| 12-bitowy przetwornik C/A |

|

|

|

|

|

| Szybki komparator |

|

|

|

|

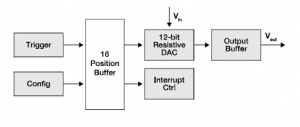

Przetwornik cyfrowo-analogowy

12-bitowy przetwornik C/A (DAC) wystawia na wyjście napięcie po podaniu na wejście wartości cyfrowej. Jego podstawowe cechy to:

- wyjście wyprowadzane na zewnętrzny pin lub do innych peryferiów procesora,

- możliwość pracy w trybach zatrzymania mikrokontrolera (Stop),

- kilka trybów pracy: swing, jednorazowy odczyt (one-time scan) oraz tryb normalny (normal),

- wiele źródeł żądania przerwania sprzętowego: najwyższa lub najniższa pozycja (top/bottom positions), albo znak wodny (watermark).

Rys. 22. Schemat blokowy przetwornika C/A

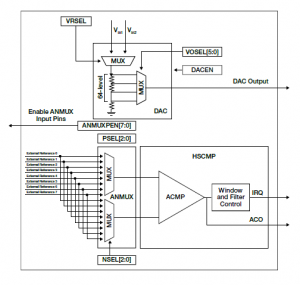

Komparator analogowy

Wbudowany analogowy komparator (High-Speed Comparator, HSCMP) umożliwia wystawienie szybkiego przerwania podczas obserwacji sygnału wewnętrznego lub zewnętrznego. Podstawowe cechy tego modułu to:

- możliwość pracy w całym zakresie napięć zasilania,

- programowalna kontrola histerezy,

- wewnętrzny 6-bitowy przetwornik C/A,

- wewnętrzny multiplekser sygnałów wejściowych, dający większą elastyczność.

Rys. 23. Schemat blokowy wbudowanego komparatora (HSCMP)

Źródło napięcia odniesienia

Źródło napięcia odniesienia (Voltage Reference, VREF) ma za zadanie dostarczać na wyjście napięcie o dokładnej wartości, ustawiane za pomocą 8-bitowego rejestru z krokiem 0,5 mV. Podstawowe cechy tego źródła:

- peryferia mogące używać VREF to: ADC, DAC oraz HSCMP,

- zewnętrzne układy mają dostęp do VREF poprzez nóżkę voltage reference output (VREFO),

- możliwość pracy w trybie wysokiej mocy (dla zastosowań zewnętrznych),

- dobra stabilność temperaturowa – wahania poniżej 33 ppm/°C w zakresie 0° – 50°C.

Rys. 24. Krzywa zależności napięcia odniesienia [V] od temperatury [°C]

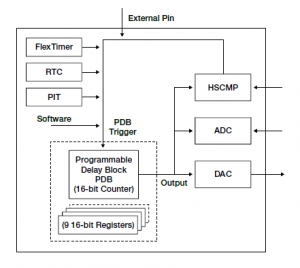

Programowalny blok opóźniający

Programowalny blok opóźniający (Programmable Delay Block, PDB) pozwala na synchronizację taktowania między wieloma wewnętrznymi lub zewnętrznymi peryferiami. Przykładowe zastosowania tego modułu, to:

- przy sterowaniu silnikami BLDS, aby zmierzyć wsteczną siłę elektromotoryczną (CEMF) za pomocą HSCMP, blok PDB synchronizuje go kilka mikrosekund po zboczu narastającym PWM z FlexTimera i tworzy w ten sposób okno analizy próbki (sample window mode),

- przy sterowaniu silnikami, PDB mierzy napięcia i prądy, aby synchronizować PWM FlexTimera i przetwornik A/C,

- w zastosowaniach pomiarowych, PDB mierzy zarówno prąd, jak i napięcie za pomocą ADC, zsynchronizowanego z jednym z timerów,

- w zastosowaniach medycznych, PDB stanowi sprzętowy wyzwalacz dla przetwornika A/C, a przy tym daje wskaźnikowi bufora DAC wyprzedzenie na ustalenie stanu sygnału.

Rys. 25. Schemat blokowy programowalnego bloku opóźniającego (PDB)

![Rys. 24. Krzywa zależności napięcia odniesienia [V] od temperatury [°C]](/wp-content/uploads/artykuly/Freescale_Coldfire_i_Kinetis_od_srodka/rys24.do_artykulow.png)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485