Projektowanie systemów cyfrowych z wykorzystaniem izolatorów

Tab. 1. Przegląd samodzielnych i przeznaczonych do określonych zastosowań izolatorów

| Charakterystyki przełączania dla Vcc1 = Vcc2 = 5 V | |||||||

| Typ izolatora | ISO | Próg wejściowy | Przepus- towość [Mbps] |

Maksymalne opóźnienie propagacji [ns] | Wahania zegara między kanałami [ns] | Typowy czas narastania [ns] | |

| Single | 721/722 | TTL | 100 | 24 | – | 1 | |

| M | CMOS | 150 | 16 | – | 1 | ||

| Dual | 7220/7221 | A | TTL | 1 | 457 | 15 | 1 |

| B | 5 | 70 | 3 | 1 | |||

| C | 25 | 42 | 1 | 1 | |||

| M | CMOS | 150 | 16 | 1 | 1 | ||

| Triple | 7230/7231 | A | TTL | 1 | 95 | 2 | 2 |

| C | 25 | 42 | 2 | 2 | |||

| M | CMOS | 150 | 23 | 1 | 2 | ||

| Quad | 7240, 7241, 7242 | A | TTL | 1 | 95 | 2 | 2 |

| C | 25 | 42 | 2 | 2 | |||

| M | CMOS | 150 | 23 | 1 | 2 | ||

| 7240 | CF | TTL | 25 | 42 | 2 | 2 | |

| RS-485 Half Duplex | 3082 | TTL | 0.2 | 1.3 (XTR) | – | 900 (XTR) | |

| 125 (RCV) | (RCV) | ||||||

| 15 | TTL | 1 | 340 (XTR) | – | 185 (XTR2) | ||

| 100 (RCV) | 2 (RCV) | ||||||

| 3088 | TTL | 20 | 45 (XTR) | – | 7 (XTR1) | ||

| 125 (RCV) | 1 (RCV) | ||||||

| RS-485 Full Duplex | 3080 | TTL | 0.2 | 1.3 (XTR) | – | 900 (XTR) | |

| 125 (RCV) | (RCV) | ||||||

| 35 | TTL | 1 | 340 (XTR) | – | 185 (XTR2) | ||

| 100 (RCV) | 2 (RCV) | ||||||

| 3086 | TTL | 20 | 45 (XTR) | – | 7 (XTR1) | ||

| 125 (RCV) | 1 (RCV) | ||||||

| Profibus Half-\Duplex | 1176 | – | 40 | 40 (XTR) | 1 | 3 (XTR) | |

| 55 (RCV) | 2 (RCV) | ||||||

Spośród pięciu klas szybkości izolatorów, A, B, C, CF oraz M, tylko wersje A, B, C i CF zawierają wewnętrzne dolnoprzepustowe filtry szumów na wejściach danych i z tego powodu zaleca się ich stosowanie w środowiskach pełnych zakłóceń. Wersja M, charakteryzująca się wysoką szybkością, wymaga zewnętrznego filtru wejściowego podczas stosowania w środowisku, w którym występują zakłócenia. Można to osiągnąć poprzez włączenie kondensatora między wejście a masę odpowiedniego urządzenia. Wartość pojemności można określić ze wzoru Cf = 1/(2π fmax x Rs), gdzie fmax to maksymalna częstotliwość sygnału, a Rs jest impedancją wyjściową jego źródła.

Projektowanie płytki PCB

Materiał PCB

Dla płytek z układami cyfrowymi pracującymi z transferami poniżej 150 Mbps (lub czasami narastania i opadania wyższymi, niż 1 ns) i długościami ścieżek do 10 cali, można do wykonania płytki drukowanej wykorzystać standardowe szkło epoksydowe FR-4 (Flame Retardant 4). Materiał ten spełnia standard Underwriters Laboratories UL84-V0 i jest preferowany ponad tańsze alternatywy ze względu na mniejsze straty dielektryka na wysokich częstotliwościach, mniejszą absorpcję wilgoci, większą wytrzymałość i sztywność, a także niską palność i zdolność do samogaszenia.

Stos warstw

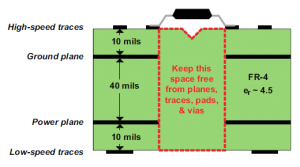

Przynajmniej cztery warstwy są potrzebne do uzyskania struktury PCB o niskiej interferencji elektromagnetycznej (rysunek 9). Ułożenie warstw musi odpowiadać następującej kolejności (od góry do dołu): warstwa sygnałów wysokiej szybkości, warstwa uziemiająca, warstwa zasilania i warstwa sygnałów niskiej częstotliwości.

Rys. 9. Zalecane ułożenie warstw

Zalecenia:

- Prowadzenie ścieżek wysokich szybkości na górnej warstwie ułatwia unikanie przelotek (i wnoszonych przez nie indukcyjności), a także pozwala na czyste połączenia między izolatorem a obwodami nadajnika i odbiornika łącza danych

- Ułożenie warstwy ciała stałego bezpośrednio pod warstwą dużych szybkości stabilizuje kontrolowalną impedancję połączeń linii transmisyjnej i zapewnia doskonałą ścieżkę powrotną o niskiej impedancji dla przepływu prądu.

- Umieszczenie warstwy zasilania obok warstwy uziemiającej tworzy dodatkową pojemność na dużych częstotliwościach, rzędu 100pF na cal kwadratowy.

- Prowadzenie wolniejszych sygnałów kontrolnych na dolnej warstwie pozwala na większą dowolność, ponieważ te połączenia mają pewien margines tolerancji dla nieciągłości w rodzaju przelotek.

Jeśli potrzebna jest dodatkowa warstwa zasilająca lub sygnałowa, należy dodać drugą warstwę zasilania / uziemienia w celu zapewnienia symetrii. To sprawia, że całość staje się stabilna mechanicznie i zapobiega odkształceniom. Ponadto, warstwy zasilania i uziemienia każdego systemu zasilania mogą być umieszczone bliżej siebie, zwiększając znacząco pojemność przy wysokich częstotliwościach.

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii  Mieszacze aktywne – ćwiczenie z serii ADALM

Mieszacze aktywne – ćwiczenie z serii ADALM