Komunikacja sieciowa z wykorzystaniem mikrokontrolerów Freescale Kinetis

Sterowanie interfejsem MII

MII to podstawowy interfejs komunikacyjny służący do wymiany danych między kontrolerem MAC i układem PHY. Jest złożony z 18 linii sygnałowych i pracuje z częstotliwością 25 MHz. Konfigurację rejestrów do pracy w trybie MII przedstawiono w listingu:

PORTA_PCR14 = PORT_PCR_MUX(4);//RMII0_CRS_DV/MII0_RXDV PORTA_PCR5 = PORT_PCR_MUX(4);//RMII0_RXER/MII0_RXER PORTA_PCR12 = PORT_PCR_MUX(4);//RMII0_RXD1/MII0_RXD1 PORTA_PCR13 = PORT_PCR_MUX(4);//RMII0_RXD0/MII0_RXD0 PORTA_PCR15 = PORT_PCR_MUX(4);//RMII0_TXEN/MII0_TXEN PORTA_PCR16 = PORT_PCR_MUX(4);//RMII0_TXD0/MII0_TXD0 PORTA_PCR17 = PORT_PCR_MUX(4);//RMII0_TXD1/MII0_TXD1 PORTA_PCR11 = PORT_PCR_MUX(4);//MII0_RXCLK PORTA_PCR25 = PORT_PCR_MUX(4);//MII0_TXCLK PORTA_PCR9 = PORT_PCR_MUX(4);//MII0_RXD3 PORTA_PCR10 = PORT_PCR_MUX(4);//MII0_RXD2 PORTA_PCR28 = PORT_PCR_MUX(4);//MII0_TXER PORTA_PCR24 = PORT_PCR_MUX(4);//MII0_TXD2 PORTA_PCR26 = PORT_PCR_MUX(4);//MII0_TXD3 PORTA_PCR27 = PORT_PCR_MUX(4);//MII0_CRS PORTA_PCR29 = PORT_PCR_MUX(4);//MII0_COL ENET_RCR = ENET_RCR_MAX_FL(configENET_RX_BUFFER_SIZE) | ENET_RCR_MII_MODE_MASK | ENET_RCR_CRCFWD_MASK;

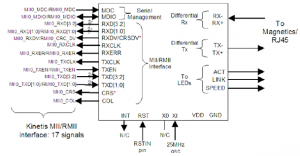

Fizyczne połączenie linii interfejsu MII mikrokontrolera Kinetis z układem PHY pokazano na rysunku 3.

Rys. 3. Sposób połączenia mikrokontrolera Kinetis z układem PHY za pomocą magistrali MII

Sterowanie interfejsem RMII

RMII to interfejs komunikacyjny kompatybilny z MII i może zostać użyty zamiast MII. Wymaga jedynie dziewięciu linii sygnałowych zachowując tą samą funkcjonalność, co MII. Interfejs RMII pracuje z częstotliwością 50 MHz. Przykładowy kod źródłowy konfigurujący rejestry do pracy w trybie RMII przedstawiono w listingu:

PORTA_PCR14 = PORT_PCR_MUX(4);//RMII0_CRS_DV/MII0_RXDV PORTA_PCR5 = PORT_PCR_MUX(4);//RMII0_RXER/MII0_RXER PORTA_PCR12 = PORT_PCR_MUX(4);//RMII0_RXD1/MII0_RXD1 PORTA_PCR13 = PORT_PCR_MUX(4);//RMII0_RXD0/MII0_RXD0 PORTA_PCR15 = PORT_PCR_MUX(4);//RMII0_TXEN/MII0_TXEN PORTA_PCR16 = PORT_PCR_MUX(4);//RMII0_TXD0/MII0_TXD0 PORTA_PCR17 = PORT_PCR_MUX(4);//RMII0_TXD1/MII0_TXD1 ENET_RCR = ENET_RCR_MAX_FL(configENET_RX_BUFFER_SIZE) | ENET_RCR_MII_MODE_MASK | ENET_RCR_CRCFWD_MASK | ENET_RCR_RMII_MODE_MASK;

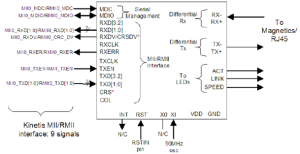

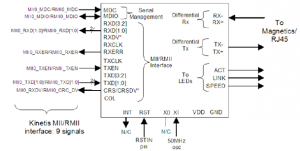

Interfejs RMII może zostać zaimplementowany fizycznie w dwóch wariantach w zależności od rodzaju układu PHY. Różnice polegają na sposobie połączenia linii między modułem MAC i układem PHY. W pierwszym wariancie linia MII0RXDV/RMII0_CRC_DV modułu MAC-NET połączona jest z linią RXDV/CRSDV układu PHY. W drugim wariancie linia MII0RXDV/RMII0_CRC_DV modułu MAC-NET połączona jest z linią CRS/CRSDV. Pierwszy wariant przedstawiono na rysunku 4, natomiast drugi wariant pokazano na rysunku 5.

Rys. 4. Sposób połączenia mikrokontrolera Kinetis z układem PHY za pomocą magistrali RMII, wariant pierwszy

Rys. 5. Sposób połączenia mikrokontrolera Kinetis z układem PHY za pomocą magistrali RMII, wariant drugi

Bibliografia

[1] www.freescale.com Kinetis Peripheral Module, 11/2010[2] www.freescale.com Kinetis Reference Manual, 05/2011

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii