Cortex-M0+ – najbardziej energooszczędny z rdzeni ARM

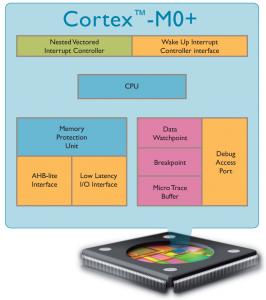

32-bitowy Cortex-M0+ to najnowszy z rdzeni mikroprocesorowych firmy ARM (o jego powstaniu producent poinformował 13 marca). Jak nazwa wskazuje, został zaprojektowany w oparciu o rdzeń Cortex-M0, który na rynku obecny jest od trzech lat i przez ten czas zdobył sobie duże uznanie klientów, o czym świadczy aż 50 licencji na ten rdzeń, które ARM udostępnił producentom mikrokontrolerów (do listopada 2011 rok). Od momentu powstania rdzenia Cortex-M0 inżynierowie z firmy ARM pracowali nad usprawnieniami, które mogłyby dodatkowo poprawić jego parametry techniczne. Efektem tych działań jest właśnie rdzeń Cortex-M0+, znany też pod nazwą „Flycatcher” (rys. 1).

Rys. 1. ARM Cortex-M0+

2-stopniowy Pipeline

Jednym z głównych wymagań wobec nowego rdzenia było obniżenie poboru mocy w porównaniu do rdzenia Cortex-M0. W celu spełnienia tego założenia zdecydowano się wykorzystać (po raz pierwszy w rdzeniu ARM) 2-stopniowy pipeline . W wyniku tego zabiegu pobór mocy (tzw. dynamic power ) przez rdzeń został zredukowany o około 1/3 (tab. 1).

Tab. 1. Porównanie poboru mocy (Cortex-M0+, Cortex-M0) dla procesu technologicznego 90 nm i częstotliwości pracy 50 MHz

| Cortex-M0+ | Cortex-M0 | |

| Static power | 0.95 µW | 0.96 µW |

| Dynamic Power | 11.21 µW/MHz | 16.36 µW/MHz |

Zmniejszenie poboru mocy przez rdzeń jest z pewnością ważne, jednak rozpatrując efektywność energetyczną trzeba się też odnieść do zapotrzebowania na moc przez cały układ, a więc rdzeń oraz zasoby mikrokontrolera. Wspomniany 2-stopwnnowy pipeline zmniejsza liczbę cykli pracy na instrukcję (CPI – number of Cycles Per Instruction ) usprawniając dostęp rdzenia do pamięci Flash, co skutkuje dalszym zmniejszeniem poboru mocy.

Ograniczenie poboru mocy nie wpłynęło negatywnie na wydajność rdzenia Cortex-M0+, która kształtuje się na poziomie 1.77 CoreMark/MHz (0.93 DMIPS/MHz), w porównaniu do 1.62 CoreMark/MHz w przypadku Cortex-M0 (0.84 DMIPS/MHz).

Nowy interfejs wejścia/wyjścia

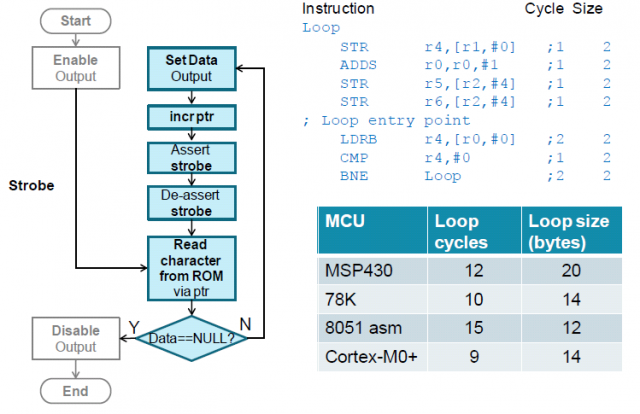

W Cortex-M0+ zaimplementowany został nowy interfejs wejścia/wyjścia (I/O), który umożliwia wykonywanie operacji I/O w jednym cyklu. Dzięki temu dostęp rdzenia do wykorzystujących ten interfejs peryferii i portów I/O jest niezwykle szybki (rys. 2).

Rys. 2. Wykonywanie instrukcji I/O – Cortex-M0+ i inne rdzenie

Moduł MPU

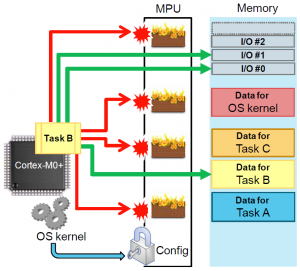

W rdzeniu Cortex-M0+ zintegrowanych zostało kilka funkcjonalności, które obecne są w Cortex-M3 i Cortex-M4, a które były niedostępne w Cortex-M0. Do najważniejszych z nich należy moduł MPU ( Memory Protection Unit ). Jest to jednostka ochrony pamięci, sterująca dynamicznie dostępem do 8 konfigurowalnych regionów pamięci. Może być użyteczna podczas wykorzystania systemu operacyjnego do nadawania uprawnień dostępu do pamięci różnym zadaniom zapobiegając nadpisaniu przez jedno z zadań obszaru pamięci, który jest już używany przez inne zadanie (rys. 3).

Rys. 3. Zasada działania modułu MPU

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii  Mieszacze aktywne – ćwiczenie z serii ADALM

Mieszacze aktywne – ćwiczenie z serii ADALM