Migracja z Cortex-M3 do Cortex-M4

SIMD

Cortex-M4 obsługuje instrukcje SIMD (oferujące zoptymalizowane operacje na wielu danych), które były niedostępne w poprzednich produktach rodziny Cortex- M. Niektóre z instrukcji znajdujących się w powyższej tabeli należą do instrukcji SIMD. Dzięki wykonywaniu ich z zastosowaniem zoptymalizowanego układu mnożenia i sumowania (MAC), wszystkie te instrukcje są wykonywane w jednym cyklu pracy. Wykorzystując instrukcje SIMD, rdzeń Cortex-M4 jest w stanie w jednym cyklu pracy wykonać operację mnożenia dwóch liczb 32-bitowych i następnie sumowania wyniku z liczbą 64-bitową dając w rezultacie liczbę 64-bitową: 32×32+64->64, zwalniając zasoby dla innych zadań, zamiast być obarczony wieloma operacjami mnożenia i dodawania.

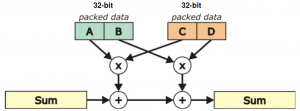

Na rysunku 7 przedstawiono operację arytmetyczną, w której dwa iloczyny na liczbach 16-bitowych (16×16) plus sumowanie liczb 32-bitowych koduje i wykonuje się za pomocą jednej instrukcji.

Suma = Suma + (A x C) + (B x D)

Rys. 7.

FPU

Jednostka obliczeniowa FPU jest opcjonalnym modułem rdzenia Cortex-M4, przeznaczonym do wykonywania operacji na liczbach zmiennoprzecinkowych pojedynczej precyzji i spełnia normę IEEE 754. Jest to implementacja wariantu pojedynczej precyzji układu rozszerzenia zmiennoprzecinkowego FPv4-SP (Floating-Point Extension). FPU rozszerza model programowania rejestrów wykorzystując zestaw 32 rejestrów pojedynczej precyzji. Rejestry te mogą być traktowane jako:

- szesnaście 64-bitowych rejestrów podwójnego słowa, od D0 do D15,

- trzydzieści dwa 32-bitowe rejestry jednego słowa, od S0 do S31.

FPU oferuje trzy tryby pracy, które umożliwiają dostosowanie do wymagań różnych aplikacji:

- tryb pełnej zgodności (Full-Compliance). W trybie pełnej zgodności jednostka FPU przetwarza wszystkie operacje zgodnie z normą IEEE 754.

- tryb zerowania (Flush-to-Zero). Ustawianie na 1 bitu FZ zmiennoprzecinkowego rejestru statusów i kontroli FPSCR (Floating-point Status and Control Register) [24] włącza tryb zerowania. W tym trybie FPU traktuje wszystkie niewłaściwe argumenty wejściowe operacji arytmetycznych CDP (Continuous Data Protection) jako zera. Odpowiednio sygnalizowane są wyjątki, które wynikają z zerowego argumentu. Operacje VABS, VNEG i VMOV nie są uważane za operacje arytmetyczne CDP i nie dotyczą trybu zerowania. Wynikowa wartość, która jest bardzo mała, jak opisano w normie IEEE 754, gdzie wartość bezwzględna docelowej precyzji obliczeń jest mniejsza niż normalna minimalna wartość przed zaokrągleniem, jest zastępowana zerem. Flaga IDC, FPSCR [7], wskazuje zerowanie wejścia. Flaga UFC, FPSCR [3], wskazuje zerowanie wyniku.

- domyślny tryb NaN. Ustawienie na 1 bitu DN, FPSCR [25], włącza domyślny tryb NaN. W tym trybie, wynik każdej arytmetycznej operacji przetwarzania danych, która używa wartości NaN (Not a Number – wartość nie będąca liczbą) na wejściu, lub która generuje wynik o wartości NaN, domyślne zwraca wartość NaN. Bity części ułamkowej są przetwarzane tylko w operacjach VABS, VNEG i VMOV. Wszystkie inne operacje CDP ignorują jakiekolwiek informacje zawarte w bitach części ułamkowej wartości NaN na wejściu.

Tabela 3 przedstawia zestaw instrukcji FPU.

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii