Migracja z Cortex-M3 do Cortex-M4

Debugowanie

Rdzenie Cortex-M4, tak samo jak Cortex-M3, są debugowane poprzez standardowe złącze JTAG lub SWD (Serial Wire Debug). Do podłączenia do systemu hosta wymagane jest proste, standardowe złącze zewnętrzne.

Zasilanie

Zarządzanie energią

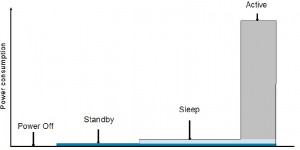

Cortex-M4, tak samo jak Cortex-M3, ma cztery tryby zasilania: aktywny, uśpienia, tryb gotowości, oraz wyłączania. Na rysunku 8 przedstawiono cztery tryby zasilania:

Rys. 8.

Power consumption – pobór mocy

Power Off – Tryb wyłączenia

Standby – Tryb gotowości

Sleep – Tryb uśpienia

Acitve – Tryb aktywny

Porównanie mocowe

Z poniższej tabeli wynika, że Cortex-M4 sprawuje się dużo lepiej niż Cortex-M3 w zakresie efektywności energetycznej.

Tab. 4.

| Cortex-M3 | Cortex-M4 | |||

| Proces | TSMC 90nm G | Proces niskiej mocy 65nm | ||

| Typ optymalizacji | Szybkość zoptymalizo-wana | Obszar zoptymalizo-wany | Szybkość zoptymalizo-wana | Obszar zoptymalizo-wany |

| Standardowa biblioteka komórkowa | ARM SC9 | ARM SC9 | ARM SC12 | ARM SC9 |

| Wydajność w liczbach całkowitych (razem DMIPS) | 344 | 63 | 375 | 188 |

| Częstotliwość (MHz) | 275 | 50 | 300 | 150 |

| Efektywność energetyczna (DMIPS/mW) | TBD | 12.5 | 24 | 38 |

| Powierzchnia (mm2) | 0.083 | 0.047 | 0.21 | 0.11 |

| Powierzchnia FPU (mm2) | NA | NA | 0.08 | 0.06 |

Migracja oprogramowania

Informacje ogólne

Ponieważ Cortex-M4 jest rozszerzonym rdzeniem Cortex-M3, oprogramowanie na poziomie systemowym może być stosowane na obu platformach. W szczególności, stos, pamięć, kod oraz umiejscowienie danych, jak również przerwania w obu rdzeniach są takie same, ponieważ mają one tę samą architekturę ARMv7-M oraz ten sam zestaw instrukcji Thumb/Thumb-2. Migrację oprogramowania z Cortex-M3 do M4 można przeprowadzić bardzo łatwo z niewielkimi zmianami. Jeśli kod jest opracowany w języku C, nie ma potrzeby żadnych zmian. Kompilatory przystosowane dla rdzenia Cortex-M4 automatycznie wywołują 32-bitową jednostkę obliczeniową MAC oraz instrukcje SIMD do realizacji zadań cyfrowego przetwarzania sygnałów (DSP). Jednak, mimo w pełni kompatybilnego kodu, występują dodatkowe uwarunkowania:

- wszystkie nieużywane rejestry SCS (System Control Space) oraz pola rejestrów rdzenia należy traktować jako niemodyfikowalne,

- należy skonfigurować następujące bity w rejestrze kodów warunków CCR (Condition Code Register): bit STKALIGN na 1, bit UNALIGN_TRP na 1, pozostawić oryginalne wartości pozostałych bitów rejestru CCR.

Przykładowy kod

W poniższym przykładzie występuje funkcja matematyczna, zapisana za pomocą instrukcji kodu źródłowego, używana do implementacji cyfrowego filtru o nieskończonej odpowiedzi impulsowej IIR oraz zliczenia liczb cykli, jakie potrzebują na to rdzenie Cortex-M3 i M4.

Funkcja:

y[n] = b0 * x[n] + b1 * x[n-1] + b2 * x[n-2] – a1 * y[n-1] – a2 * y[n-2]

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii