Mikrokontrolery Kinetis: co (prawdopodobnie) nas wkrótce spotka

Rodzina mikrokontrolerów Kinetis szybko się rozwija, obok dobrze już znanych podrodzin Kinetis K do sprzedaży trafiają już mikrokontrolery z rodzin Kinetis L i Kinetis W. W artykule przedstawiamy plany firmy Freescale związane z dalszym rozwojem rodziny mikrokontrolerów Kinetis.

W aktualnej ofercie produkcyjnej firmy Freescale znajdują się mikrokontrolery Kinetis K (z rdzeniami Cortex-M4 i i Cortex-M4F) oraz Kinetis L (z rdzeniem Cortex-M0+). Obydwie produkowane podrodziny składają się z kilku grup mikrokontrolerów (Kinetis K10…K70, Kinetis KL0…KL4), różniących się między sobą możliwościami, wewnętrznym wyposażeniem, pojemnościami pamięci i wieloma innymi detalami, które predestynują poszczególne grupy mikrokontrolerów do różnych zastosowań. Mikrokontrolery produkowane dotychczas w ramach rodziny Kinetis są ze sobą w znacznym zakresie fizycznie kompatybilne (rysunek 1), co ułatwia migrację pomiędzy platformami sprzętowymi o różnej mocy obliczeniowej i wynikającej z tego – mocy obliczeniowej.

Rys. 1. Podrodziny Kinetis K (Cortex-M4/M4F) i Kinetis L (Cortex-M0) są w znacznym zakresie wzajemnie wymienne, w obydwu podrodzinach oferowane są mikrokontrolery o wyposażeniu podstawowym i zaawansowanym

Interesującym pomysłem twórców rodziny Kinetis L jest planowane wprowadzenie mikrokontrolerów Kinetis KL0, zgodnych fizycznie z 8-bitową rodziną S08P. Jest to zgodne z niegdyś intensywnie promowanym przez Freescale pomysłem zapewnienia konstruktorom korzystającym z produkowanych przez firmę mikrokontrolerów ścieżkę continuum, pozwalającą elastycznie dostosowywać typ mikrokontrolera (i jego cenę) do realnych i zmieniających się wymagań aplikacji. Planowany zakres pojemności pamięci Flash w mikrokontrolerach Kinetis L wynosi od 8 do 256 kB, częstotliwości taktowania rdzenia mieszczą się w przedziale 32…48 MHz, układy będą oferowane w obudowach o liczbie wyprowadzeń od 16 do 100.

|

Cortex-M0+ vs Cortex-M0 – szybciej, taniej, energooszczędnie Podstawowym celem firmy ARM podczas opracowywania rdzenia Cortex-M0 było przygotowanie maksymalnie taniej w implementacji wersji 32-bitowego rdzenia w znacznym stopniu zgodnego z większym „rodzeństwem” – Cortex-M3 i Cortex-M4/M4F. Podstawowym uproszczeniem w stosunku do rdzenia M3 było zredukowanie listy instrukcji asemblera do 56 rozkazów, które są podstawowym podzbiorem obsługiwanym przez wszystkie rdzenie Cortex-M, zrezygnowano także z modułu MPU, uproszczono blok sprzętowego debugowania, zmodyfikowano interfejs łączący pamięci z CPU, zmniejszono liczbę przerwań obsługiwanych przez kontroler NVIC, uproszczeniom i redukcjom poddano także wiele innych fragmentów rdzenia. Zabiegi te zaowocowały dwukrotnym zmniejszeniem dynamicznego poboru mocy przez Cortex-M0 w stosunku do Cortex-M3 (16 uW/MHz vs 32 uW/MHz w technologii referencyjnej 90LP) oraz trzykrotnym zmniejszeniem powierzchni zajmowanej przez rdzeń (0,04 mm2 vs 0,12 mm2) – co ułatwia jego tanią implementację. Obniżenie poboru mocy i zmniejszenie zajmowanej powierzchni odbiły się na wypadkowej wydajności rdzenia Cortex-M0, który zamiast prędkości wykonywania programu 1,25 DMIPS/MHz (Cortex-M3) uzyskiwał w testach zaledwie 0,84 DMPIS/MHz. Tak znaczne obniżenie prędkości wykonywania programów i krótka lista instrukcji (co czasami wymagało wykonywania dłuższych sekwencji programowych zamiast jednego polecenia) redukowały zalety wynikające z mniejszego nominalnego poboru mocy na jednostkę częstotliwości taktowania. Problemy zgłaszane przez użytkowników i producentów mikrokontrolerów wyposażonych w rdzenie Cortex-M0 zostały dostrzeżone także przez firmę ARM, co zaowocowało wprowadzeniem do oferty zmodyfikowanej wersji rdzenia, nazwanej Cortex-M0+. |

Pomimo bogatych możliwości i różnorodnego wyposażenia dotychczas produkowanych mikrokontrolerów, firma Freescale przymierza się do wprowadzenia na rynek dwóch kolejnych rodzin – zapowiadanych od kilku miesięcy Kinetis X oraz nieujawnianej dotychczas podrodzinie Kinetis E (rysunek 2).

Rys. 2. Planowane przez firmę Freescale pozycjonowanie mikrokontrolerów z rodziny Kinetis

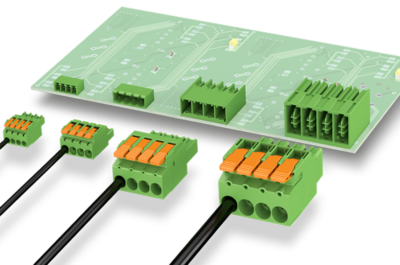

Nowe generacje złączy: innowacyjne metody połączeń w elektronice

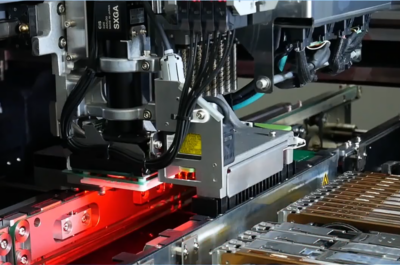

Nowe generacje złączy: innowacyjne metody połączeń w elektronice  Zaawansowane urządzenia do montażu SMT na przykładzie automatu P&P RS-2 – analiza technologiczna i zastosowania w nowoczesnej produkcji elektroniki

Zaawansowane urządzenia do montażu SMT na przykładzie automatu P&P RS-2 – analiza technologiczna i zastosowania w nowoczesnej produkcji elektroniki  Wdrażanie fizycznej AI na obrzeżach sieci radiowej w systemach obronnych

Wdrażanie fizycznej AI na obrzeżach sieci radiowej w systemach obronnych