Nowość w ofercie Atmela: mikrokontrolery SAM D20 z rdzeniem Cortex-M0+

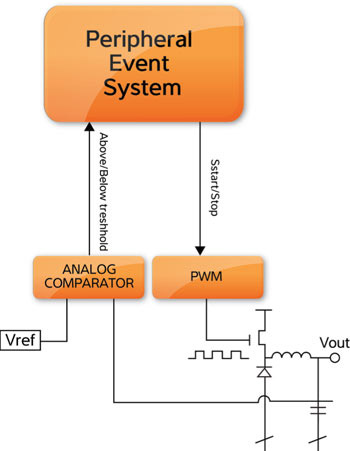

Kontroler zdarzeń zastępuje częściowo sterownik DMA, a przykładem jego wykorzystania może być korygowanie bez udziału CPU wartości współczynnika PWM w zależności od obciążenia, w przetwornicy DC/DC zaimplementowanej w mikrokontrolerze (rysunek 3).

Rys. 3. Przykładowa aplikacja kontrolera zdarzeń: niezależna od CPU przetwornica DC/DC

Zaletą wbudowanego w prezentowane układy kontrolera zdarzeń, jest możliwość wybudzania przez niego bloków peryferyjnych z trybu uśpienia (włączania sygnału zegarowego) i ich usypianie (czyli wyłączanie sygnału zegarowego) po wykonaniu zadania. Funkcjonalność ta nosi nazwę Sleep Walking.

|

JTAGICE 3 i SAM D20 Najnowsza wersja pakietu Atmel Studio 6.1 update 2.0 (build 2730), zawiera upgrade firmware’u do programatora-debuggera JTAGICE3, który dotychczas obsługiwał wyłącznie mikrokontrolery z rodziny AVR. Nowa wersja firmware’u umożliwi użytkownik interfejsu programowanie i debugowanie mikrokontrolerów SAMD20 poprzez interfejs SWD (Serial Wire Debug).

|

|

Mikrokontrolery z rodziny SAM D20 są pierwszymi układami w ofercie Atmela z energooszczędnym rdzeniem Cortex-M0+. Wraz z wprowadzeniem do sprzedaży pierwszych mikrokontrolerów z tej rodziny, firma Segger ogłosiła, że są one obsługiwane przez interfejsy JTAG z rodziny J-Link (m.in. atrakcyjny cenowo J-Link EDU, dostępny w KAMAMI.pl). Za pomocą tych interfejsów można programować pamięć Flash mikrokontrolerów z rodziny SAM D20 oraz śledzić wykonywanie programów z wykorzystaniem popularnych środowisk programistycznych (m.in. uVision firmy Keil, EWARM firmy IAR). Rdzeń Cortex-M0 obsługuje maksymalnie cztery sprzętowe pułapki, jednak korzystając z funkcji bardziej rozbudowanych interfejsów JTAG (J-Link PLUS, J-Link ULTRA+, J-Link PRO i J-Trace) programista może korzystać z zaimplementowanej w tych interfejsach funkcji umożliwiającej zastawiane nieograniczonej liczby pułapek zarówno w wewnętrznej, jak i zewnętrznej pamięci programu mikrokontrolera.

|

Mikrokontrolery SAM D20 wyposażono w pamięć Flash, w której można zaimplementować emulowaną pamięć EEPROM o pojemności do 64 kB (ustala użytkownik, parytet wynosi 8:1 Flash/EEPROM), w której aplikacja użytkownika może przechowywać swoje często zmieniane dane. Prezentowane mikrokontrolery wyposażono ponadto w mechanizmy wspomagające bezpieczną wymianę oprogramowania przechowywanego w pamięci Flash, w czym jest pomocny wydzielony, chroniony przed skasowaniem, obszar pamięci dla bootloadera. Producent umożliwił – w zależności od potrzeb aplikacji – przeznaczenie dla bootloadera od 512 B aż do 32 kB pamięci Flash, można z niego także całkiem zrezygnować, przeznaczając całą pamięć Flash na potrzeby aplikacji użytkownika. Co interesujące, CPU może podczas przeprogramowywania Flash wykonywać program z pamięci RAM, dzięki czemu – w wymagających tego urządzeniach – pomimo wymiany firmware system może działać, obsługując najważniejsze wydarzenia na bieżąco.

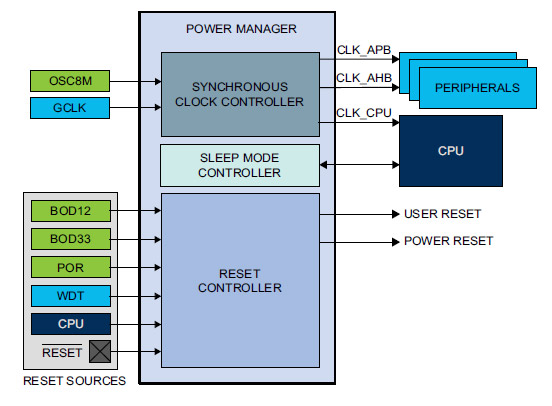

Rys. 4. Budowa bloku Power Manager, który jest integralną częścią otoczenia CPU w mikrokontrolerach SAM D20

Mając na uwadze bezpieczeństwo aplikacji mikrokontrolery SAM D20 wyposażono w blok kontroli prawidłowej pracy generatora taktującego, który zawarto w podsystemie Power Manager (rysunek 4). Wykrycie zatrzymania z jakiejś przyczyny generatora taktującego z zewnętrznym rezonatorem powoduje automatyczne przełączenie źródła taktowania na wewnętrzny generatora OSC8M i wygenerowanie przerwania, które informuje aplikację użytkownika o konieczności uwzględnienia zmiany źródła taktowania.

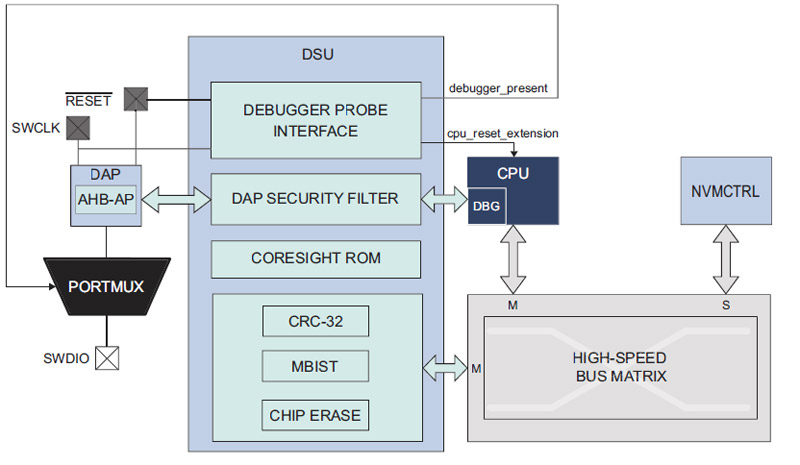

Rys. 5. Schemat blokowy bloku DSU (Device Service Unit)

Kolejnym blokiem sprzętowym, zwiększającym bezpieczeństwo działania systemu z mikrokontrolerem SAM D20 jest Device Service Unit (DSU) – rysunek 5. Zintegrowano w nim generator CRC32, który służy do niezależnej od CPU weryfikacji zawartości pamięci Flash, RAM oraz EEPROM. Poprawność funkcjonowania pamięci Flash i RAM weryfikuje także specjalny kontroler o nazwie mBIST (Memory Built in Self Test), który weryfikuje prawidłowość działania każdej komórki pamięci. Kolejnym elementem wbudowanym w DSU jest Peripheral Access Controller (PAC), którego zadaniem jest ochrona zawartości rejestrów konfigurujących peryferia przed przypadkowym zamazaniem.

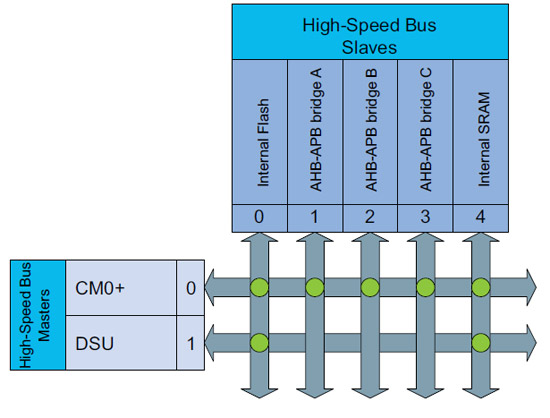

Rys. 6. Matryca połączeń komunikacyjnych CPU i DSU z mostem szybkiej magistrali komunikacyjnej w mikrokontrolerach SAM D20

Na rysunku 6 pokazano możliwości komunikacyjne rdzenia (CPU) mikrokontrolera oraz bloku DSU, które są dostępne poprzez szybkie magistrale komunikacyjne.

Blok DSU współpracuje z interfejsem SWD (Single Wire Debug, nieco uproszczona funkcjonalnie wersja JTAG), który jest wykorzystywany do programowania pamięci Flash i debugowania pracy mikrokontrolera (o narzędziach piszemy nieco więcej w ramkach).

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485