Renesas Synergy – mikrokontrolery z Cortex-M w ofercie produkcyjnej firmy Renesas

Środowisko Renesas Synergy jest pierwszym na rynku, kompleksowym zestawem oprogramowania narzędziowego, bibliotek, driverów i sprzętu, zorientowanym zarówno na aplikacje IoT jak i klasyczne aplikacje mikrokontrolerowe. Dla wielu programistów zachęcający do przetestowania możliwości tego środowiska jest fakt, że bazuje ono na mikrokontrolerach wyposażonych w rdzenie Cortex-M.

Mikrokontrolery wyposażone w rdzenie z rodziny ARM Cortex-M są gorącą nowością w ofercie firmy Renesas, która dotychczas konsekwentnie rozwijała i promowała rozwiązania głównie z własnego portfolio. W ramach rodziny Synergy producent oferuje 4 rodziny, z których jedna – oznaczona symbolem S1 – jest wyposażona w rdzeń Cortex-M0+ (taktowany do 32 MHz), pozostałe rodziny – oznaczone symbolami S3, S5 i S7 – wyposażono w rdzenie Cortex-M4F (z wbudowanymi: jednostką FPU i MPU). Programowanie pamięci Flash i debugowanie pracy odbywa się za pomocą interfejsu JTAG (rodziny S7, S5 i S3) lub SWD (w mikrokontrolerach S7, S5, S3 i S1). Ciekawostką, dowodzącą dużego potencjału technologicznego firmy Renesas, jest szybki dostęp do pamięci Flash w mikrokontrolerach S7 i S5, w których CPU może ją bezpośrednio taktować z częstotliwością do 120 MHz. Wartym podkreślenia atutem rodzin S3 i S1 jest z kolei szeroki zakres napięć zasilających, który wynosi od 1,6 do 5,5 V. Standardowy zakres temperatur pracy mikrokontrolerów Renesas Synergy montowanych w obudowach LQFP wynosi od -40 do +105oC, pozostałe obudowy (LGA i BGA) są przystosowane do pracy w zakresie temperatur od -40 do +85oC. Mikrokontrolery S5 i S7 – o rozbudowanych zasobach wewnętrznych – są produkowane w technologii o wymiarze charakterystycznym 40 nm, do produkcji „mniejszych” mikrokontrolerów – S3 i S1 – użyto nowoczesnej technologii 130 nm.

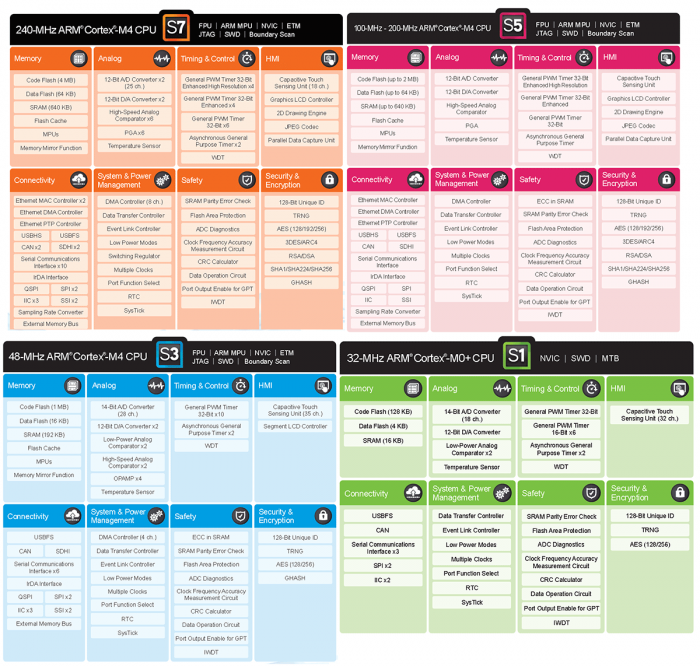

Zestawienie najważniejszych elementów wyposażenia poszczególnych rodzin znajduje się w tabeli 1, a na rysunku 1 pokazano ogólne schematy blokowe poszczególnych rodzin mikrokontrolerów Renesas Synergy.

Tab. 1. Zestawienie podstawowych danych mikrokontrolerów Renesas Synergy

|

Cecha |

S7 |

S5 |

S3 |

S1 |

|

Rdzeń |

||||

|

ARM® Cortex®-M0+ (MHz) |

32 |

|||

|

ARM® Cortex®-M4 (MHz) |

240 |

120 |

48 |

|

|

Pamięci |

||||

|

Flash – program [kB] |

4096 |

2048 |

1024 |

128 |

|

Flash – dane [kB] |

64 |

64 |

16 |

4 |

|

SRAM [kB] |

640 |

640 |

192 |

16 |

Rys. 1. Schemat blokowe mikrokontrolerów Renesas Synergy

Jak widać, wyposażenie mikrokontrolerów jest bardzo bogate, przy czym uważnie podzielone pomiędzy poszczególne rodziny, co w znacznym stopniu determinuje ich obszary aplikacyjne. Wspólne wyposażenie wszystkich rodzin mikrokontrolerów, jak m.in.: duża liczba uniwersalnych liczników-timerów, watchdogi, synchroniczne i asynchroniczne porty komunikacyjne (SPI, I2C, UART), przetworniki ADC i DAC, bufor cache dla pamięci Flash, interfejsy USB device oraz CAN, interfejs klawiatur i nastawników pojemnościowych czy kontroler przerwań NVIC nie odbiega od standardów, do jakich przyzwyczaili się użytkownicy alternatywnych mikrokontrolerów 32-bitowych.

|

Renesas Synergy – pełna skalowalność

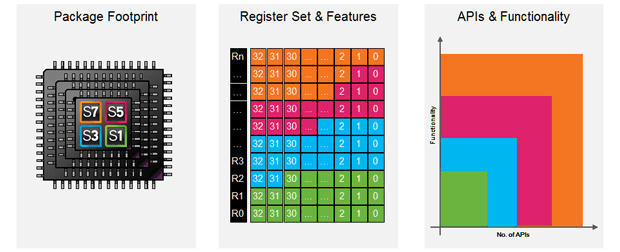

Mikrokontrolery Renesas Synergy gwarantują konstruktorom możliwość wygodnego skalowania sprzętu użytego do realizacji zadań, co jest możliwe dzięki kompatybilności wyprowadzeń układów montowanych w takich samych obudowach, utrzymaniu we wszystkich modelach funkcji rejestrów i ich lokalizacji w przestrzeni adresowej, a także skalowanemu API bibliotek. |

Standardowym wyposażeniem wszystkich rodzin mikrokontrolerów Renesas Synergy są także rzadko spotykane wśród rozwiązań konkurencyjnych bloki funkcjonalne:

- DOC (Data Operation Circuit), który jest – w zależności od konfiguracji – sprzętowym arytmometrem (dodającym, odejmującym i porównującym 16-bitowe dane),

- DTC (Data Transfer Controller), który samodzielnie realizuje transfer niewielkich paczek danych po wystąpieniu wybranego przez użytkownika przerwania, zastępując CPU i kanały DMA i wykorzystując podczas działania wewnętrzną magistralę DMA,

- ELC (Event Link Controller), będący konfigurowalnym automatem samoczynnie obsługującym transfery danych z wewnętrznych modułów generujących dane (jak porty GPIO, DMAC czy DTC) do modułów wymagających danych wejściowych (jak m. in. DAC, CTSU – Capacitive Touch Sensing Unit, porty GPIO czy GPT – General PWM Timer). Moduł ELC jest uruchamiany przerwaniami PORT_IRQ1…15,

- system autodiagnostyki przetwornika ADC, zapobiegający powstawaniu błędnych odczytów,

- MMF (Memory Mirror Function), który w sposób konfigurowalny realizuje sprzętowe mapowanie programu zapisanego w pamięci Flash do standardowo nieużywanej 23-bitowej przestrzeni adresowej,

- system diagnostyki sygnałów zegarowych z oceną ich częstotliwości i wartości współczynnika wypełnienia,

- system weryfikacji poprawności danych w SRAM (parity error chceck), który wykrywa także błędy podwójne,

- system ochrony zawartości pamięci RAM ze sprzętowym korektorem ECC.

Bardziej wyspecjalizowane bloki wewnętrzne producent rozdzielił pomiędzy poszczególne rodziny, co w pewnym stopniu determinuje ich obszary aplikacyjne.

Ponadstandardowymi elementami wyposażenia wewnętrznego w mikrokontrolerach Renesas Synergy są na przykład: interfejsy komunikacyjne Ethernet z PTP (S7 i S5), wzmacniacze PGA (S7 i S5), wzmacniacze operacyjne (S3), komparatory analogowe (szybkie w S7, S5 i S3 oraz energooszczędne w S3 i S1) czy konwerter częstotliwości próbkowania cyfrowych sygnałów audio (S7).

|

Selektor pomoże wybrać optymalny mikrokontroler Producent mikrokontrolerów Synergy przygotował interaktywny selektor, za pomocą którego można szybko i wygodnie wybrać mikrokontroler o cechach i wyposażeniu optymalnych dla danej aplikacji. |

Ponieważ środowisko Renesas Synergy powstało z myślą o aplikacjach IoT, w mikrokontrolerach Synergy zastosowano zaawansowane rozwiązania sprzętowe wspomagające bezpieczeństwo transmisji danych. Koprocesor kryptograficzny obsługuje symetryczne (AES/3DES/ARC4) i asymetryczne (RSA/DSA/DLP) algorytmy szyfrujące, sprzętowo oblicza skróty danych SHA1/SHA224/SHA256/GHASH, wyposażono go także w sprzętowy generator liczb losowych, zgodny z zaleceniami NIST.

|

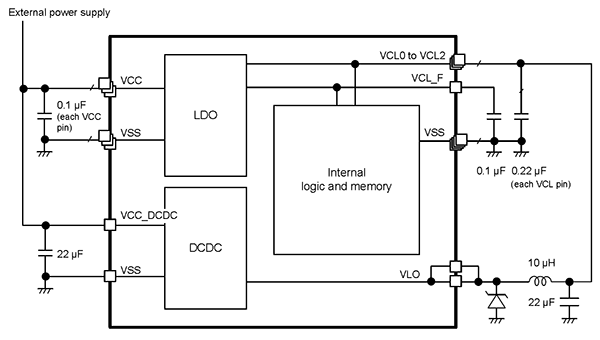

Przetwornica DC/DC w Synergy S7

Mikrokontrolery Synergy S7 wyposażono w zintegrowaną przetwornicę DC/DC, która wymaga zastosowania tylko dwóch elementów zewnętrznych: dławika i diody Schottky’ego (jak na schemacie powyżej). Rozwiązanie takie jest rzadko spotykane w mikrokontrolerach, a pozwala m.in. zminimalizować straty mocy w strukturze mikrokontrolera. |

Mikrokontrolery z rodzin S7 i S5 – przeznaczone w rodzinie Synergy do stosowania w najbardziej wymagających aplikacjach – wyposażono w kontrolery graficznych LCD, których pracę wspomaga koprocesor graficzny 2D. Umożliwia on wygodne tworzenie zaawansowanych grafik z wykorzystaniem efektów przeźroczystości, nakładania tekstur, rozmywania krawędzi oraz automatycznego antyaliasingu, który jest szczególnie przydatny podczas skalowania zrastrowanych obrazów. Koprocesor graficzny może współpracować ze sprzętowym kodekiem JPEG, który jest także standardowym elementem wyposażenia mikrokontrolerów S7 i S5. Moduły obsługujące grafikę w mikrokontrolerach Renesas Synergy dołączono do CPU za pomocą wydzielonej magistrali GPX, co minimalizuje ryzyko powstawania „wąskich gardeł” podczas transferów dużych paczek danych.

|

Bezpłatne oprogramowanie narzędziowe

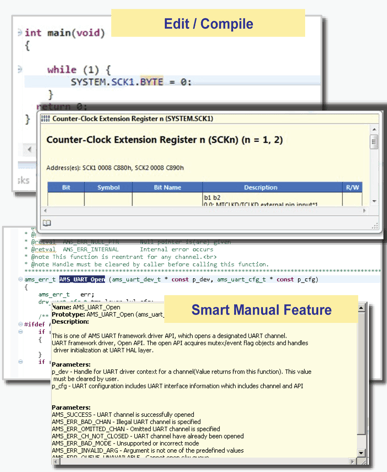

Firma Renesas przygotowała i bezpłatnie udostępnia środowisko programistyczne dla osób zainteresowanych platformą Synergy – e2Studio. Narzędzie bazuje na IDE Eclipse, dzięki czemu oswojenie środowiska nie sprawi większej trudności konstruktorom korzystającym z innych narzędzi tego typu dostępnych na rynku. |

Prezentowane w artykule mikrokontrolery Renesas Synergy są integralnym elementem opracowanej przez firmę Renesas platformy Synergy, która jest zintegrowanym rozwiązaniem programowo-sprzętowo-narzędziowym zorientowanym na konstruktorów korzystających z rozwiązań bazujących na rdzeniach Cortex-M. W kolejnych artykułach naszego cyklu pokażemy przykłady prostych aplikacji zrealizowanych w tym środowisku, bazując na jednym z pierwszych dostępnych zestawów startowych – SK-S7G2 (opisany w artykule).

Piotr Zbysiński

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485