[RAQ] Dlaczego procesor marnuje energię? Oto jest pytanie…

Pytanie:

Dlaczego mój procesor pobiera więcej mocy, niż podano w karcie katalogowej?

Odpowiedź:

W artykule ”Spalony tak małą mocą? Niski pobór prądu też może powodować problemy” opisałem problem urządzenia pobierającego zbyt małą moc (tak, to możliwe), co wpakowało mnie w kłopoty. To jednak rzadko spotykana sytuacja. Częstszym problemem, z którym borykają się klienci, jest pobieranie przez elementy większej mocy, niż jest podane w ich karcie katalogowej

Pamiętam, jak klient wszedł do mojego biura z płytką i procesorem, oznajmiając, że pobierają one zbyt dużą moc i wyczerpują baterię. Ponieważ my reklamowaliśmy ten procesor jako energooszczędny (ultra low power), musieliśmy udowodnić, że jest taki w istocie. Gdy przygotowałem się do typowego badania polegającego na odcinaniu zasilania kolejnych układów w poszukiwaniu tego, który był przyczyną problemów, przypomniałem sobie jak w niedalekiej przeszłości w podobnym przypadku winna była dioda włączona beztrosko między szynę zasilania i masę bez jakiegokolwiek rezystora ograniczającego prąd. Prawdopodobnie zbyt wysoki pobór prądu doprowadził do spalenia tej samotnej diody – ale to już dygresja.

Mając w pamięci ten przypadek, w pierwszym momencie poszukałem diody LED świecącej intensywnie gdzieś na płytce. Jednak tym razem przyczyna nie była tak jasno widoczna – prawdę mówiąc, nie było żadnego innego układu poza procesorem, na który można by zrzucić winę. Sytuację pogorszyła jeszcze inna informacja od klienta: odkrył, że pobór mocy i zużycie baterii było zgodne z oczekiwaniami podczas testów w laboratorium, natomiast baterie szybko się wyczerpywały po zainstalowaniu systemu w terenie. Tego rodzaju problemy są najtrudniejsze do rozwiązania, ponieważ kłopot stanowi już samo odtworzenie takiego zachowania. Tego rodzaju nieprzewidywalność najczęściej jest kojarzona z układami analogowymi i stanowi dodatkowe wyzwanie w przypadku układu cyfrowego, który zazwyczaj przetwarza bardzo przewidywalne wartości zer i jedynek.

W najprostszym ujęciu procesor składa się z dwóch sfer pobierających prąd: rdzenia oraz układów wejścia/wyjścia. Gdy zachodzi potrzeba sprawdzenia poboru mocy rdzenia, można zbadać takie rzeczy, jak konfigurację PLL i szybkość zegara, napięcia na szynie zasilania oraz czas, jaki procesor poświęca na obliczenia. Zawsze istnieją sposoby na minimalizację poboru mocy rdzenia – na przykład poprzez obniżenie częstotliwości zegara lub wykorzystanie specjalnych instrukcji, które zatrzymują pracę rdzenia czy też powodują przejście w tryb uśpienia lub hibernacji. Natomiast jeśli wysoki pobór mocy jest powodowany przez blok wejścia/wyjścia, warto zwrócić uwagę na zasilenia układów I/O, szybkość ich pracy oraz dołączone do nich obciążenie.

To były jedyne dwa obszary, które mogłem zbadać. Okazało się, że w rdzeniu nie było niczego podejrzanego. Zatem problem musiał tkwić w sferze I/O. W tym momencie klient wyjawił, że wykorzystywał procesor wyłączenie do obliczeń, a aktywność w obszarze I/O była minimalna. W praktyce nie wykorzystywał większości interfejsów I/O dostępnych w układzie.

- „Zaraz! Nie używasz niektórych pinów bloku I/O. Zatem nie są one używane. Jak je podłączyłeś?”

- „Oczywiście nie podłączyłem ich do niczego.”

- „Aha!”

W tym momencie powinienem raczej krzyknąć „Eureka!”. Po chwili entuzjazmu zabrałem się za wyjaśnienie problemu.

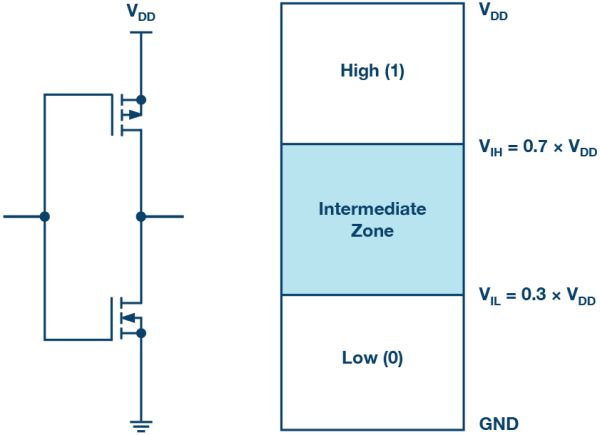

Typowe cyfrowe wejście CMOS widać na rysunku 1.

Rysunek 1. Typowy obwód wejścia cyfrowego CMOS (po lewej) i stany logiczne CMOS (po prawej)

Jeśli to wejście jest wysterowane wymaganym poziomem 0 lub 1, tylko jeden z tranzystorów MOSFET (PMOS lub NMOS) jest włączony – ale nigdy oba naraz. Występuje jednak pewna strefa niepewności poziomu napięcia wejściowego, zwana obszarem progowym, gdzie oba tranzystory NMOS i PMOS mogą włączyć się częściowo w tym samym czasie, tworząc ścieżkę przepływu prądu między linią zasilania a masą. Takie zjawisko może wystąpić, jeśli wejście nie jest do niczego podłączone i zbiera szumy otoczenia. To tłumaczy oba zjawiska podane przez klienta: wysoki pobór mocy płytki klienta oraz losowe występowanie tego problemu.

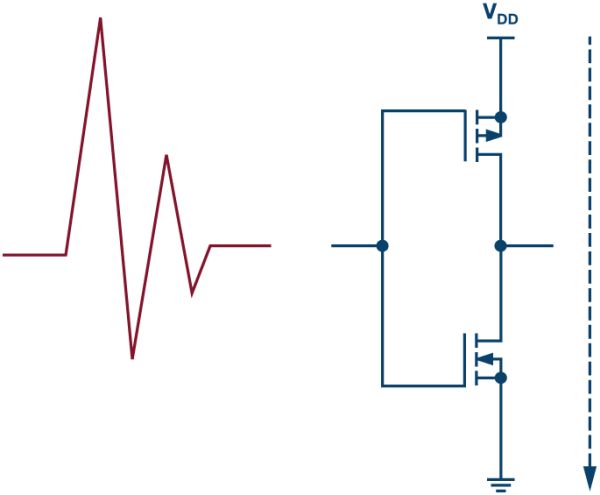

Rysunek 2. Oba tranzystory PMOS i NMOS są częściowo włączone, powodując przepływ prądu między zasilaniem a masą

W pewnych sytuacjach może to doprowadzić do stanu zatrzaśnięcia (latch-up), w wyniku którego układ stale pobiera wysoki prąd i w rezultacie ulega przepaleniu. Można powiedzieć, że taki problem łatwo zidentyfikować i zdebugować, bo układ zaczyna dymić na twoich oczach. Problem, który zgłosił mój klient, był trudniejszy do rozwiązania, ponieważ nie wznosił czerwonej flagi ostrzeżenia, gdy był testowany w komfortowych warunkach laboratorium, ale powodował dużo żalu podczas pracy w terenie.

Rozumiejąc już pierwotną przyczynę problemu, oczywistym rozwiązaniem jest wysterowanie wszystkich nieużywanych wejść prawidłowym poziomem logicznym – niskim lub wysokim. Jest jednak coś, napisane drobnym drukiem, na co należy jednak zwrócić uwagę. Przyjrzyjmy się kilku innym scenariuszom, w których niewłaściwie obsłużone wejścia CMOS mogą spowodować wystąpienie problemów. Jest to możliwe nie tylko w sytuacjach, w których wejścia są zupełnie do niczego nie podłączone, ale także, gdy wydaje się, że zostały podłączone do prawidłowego poziomu logicznego.

W przypadku prostego połączenia pinu z linią zasilania lub masą za pomocą rezystora należy zwracać uwagę na wartość tego ostatniego. Pod wpływem prądu płynącego przez wyprowadzenie mogłaby nastąpić zmiana napięcia widzianego przez pin do niepożądanego poziomu. Krótko mówiąc, musisz upewnić się, że podciąganie lub zwieranie jest poprawne.

W przypadku aktywnego wysterowania pinu, zawsze należy upewnić się, że moc tego wysterowania jest wystarczająca do obciążenia CMOS. Jeśli ten warunek nie zostanie spełniony, przypadkowe szumy mogą okazać się silniejsze od sygnału i przełączyć pin w niepożądany stan.

Przyjrzyjmy się kilku przykładom:

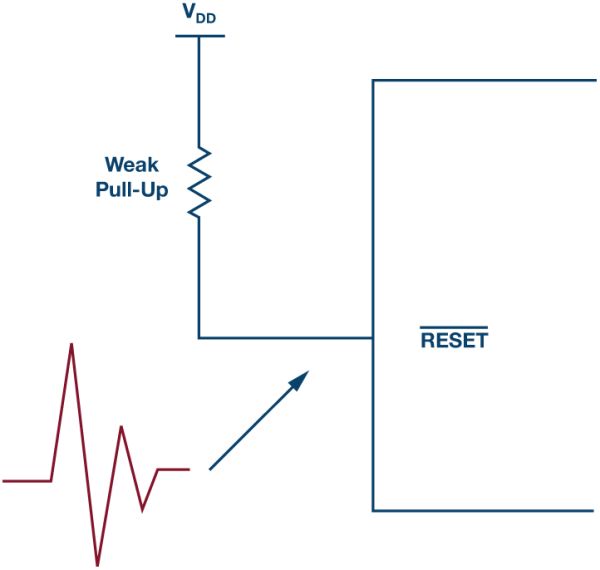

1. Procesor pracujący poprawnie w laboratorium zaczyna się resetować podczas pracy w terenie pod wpływem szumu sprzęgającego się z linią RESET, która nie miała wystarczająco silnego podciągnięcia.

Rysunek 3. Szum sprzęgający się z wejściem RESET podłączonego do małego rezystora podciągającego powoduje restart procesora

2. Można sobie wyobrazić sytuację, w której wejście CMOS jest wejściem dla sterownika bramki MOSFET/IGBT dużej mocy, który mógłby przypadkowo włączyć się w nieodpowiednich momentach. W rzeczy samej, to ponure wieści.

Rysunek 4. Szum silniejszy od słabego wysterowania wejścia CMOS powoduje zwarcie na linii wysokiego napięcia

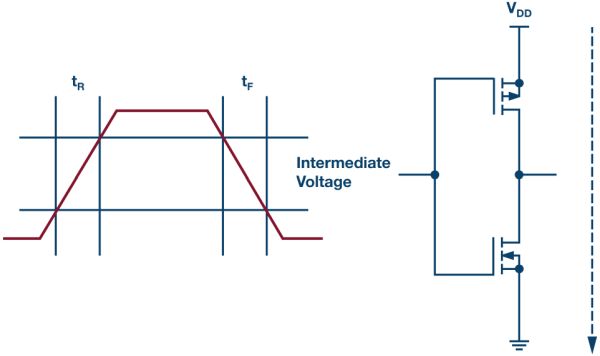

Innym podobnym, choć nie tak oczywistym scenariuszem jest sytuacja, w której sygnały sterujące mają bardzo wolne czasy narastania i opadania. Wówczas wejście może przez określony czas znaleźć się w przejściowym zakresie napięcia, co może prowadzić do najróżniejszych problemów.

Rysunek 5. Długie czasy narastania i opadania na wejściach CMOS powodują chwilowe zwarcie obwodu w okresie przejściowym

Po zapoznaniu się z pewnymi potencjalnymi problemami na wejściach CMOS wszelkiego rodzaju, warto przypomnieć, że wiele układów dobrze sobie z nimi radzi dzięki samej zasadzie działania. Na przykład podzespoły z przerzutnikami Schmitta na wejściach z natury lepiej obsługują sygnały zaszumione lub te o powolnych zboczach.

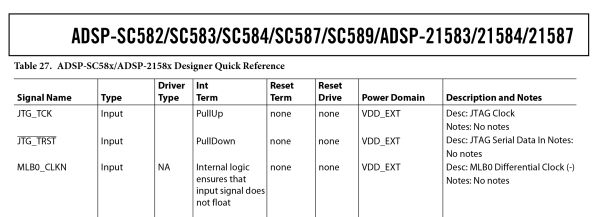

Niektóre z najnowszych procesorów w ofercie ADI uwzględniają te problemy i są wyposażone w specjalne środki zabezpieczające lub dostarczają bezpośrednich wskazówek projektowych, które gwarantują poprawne działanie. Na przykład karta katalogowa modelu ADSP-SC58x/2158x jasno określa, które piny mają wewnętrzne zakończenie lub obwód logiczny gwarantujący, że pin nie pozostanie nigdy nieustalony.

Rys. 6. Fragment specyfikacji układu ADSP-SC58x/2158x

Reasumując, jak zawsze się mówi, w przypadku cyfrowych wejść CMOS dobrze jest zadbać o podłączenie nieaktywnych wyprowadzeń.

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485