Akeana wychodzi z ukrycia z nisko- i wysokowydajnymi alternatywami RISC-V dla ARM

Dziś startup ogłosił szeroką gamę konfigurowalnych rozwiązań IP procesorów opartych na RISC-V, wspieranych przez 100 milionów dolarów finansowania.

źródło – Akeana

Podczas gdy wiele startupów spędza swoje początkowe lata w zapomnieniu z niewielkimi zasobami, Akeana rozoczęła ze znacznym doświadczeniem i finansowaniem. Firma z siedzibą w San Jose została założona w 2021 roku przez zespół doświadczonych projektantów chipów serwerowych, a kilku założycieli było bezpośrednio zaangażowanych w projektowanie ThunderX2 firmy Marvell. Po około trzech latach Akeana pozyskała ponad 100 milionów dolarów finansowania i zatrudnia 150 inżynierów na całym świecie.

Misją Akeana jest wprowadzanie innowacji w sektorze półprzewodników dzięki kompleksowemu pakietowi konfigurowalnych rozwiązań IP procesorów opartych na RISC-V. Firma oferuje alternatywy dla uznanych architektur, takich jak ARM, dostarczając wysokowydajne i skalowalne IP procesora, które można dostosować do konkretnych aplikacji. Dziś startup z Doliny Krzemowej wyszedł z trybu ukrycia z nową serią procesorów RISC-V.

Procesory RISC-V firmy Akeana o niskiej i wysokiej wydajności

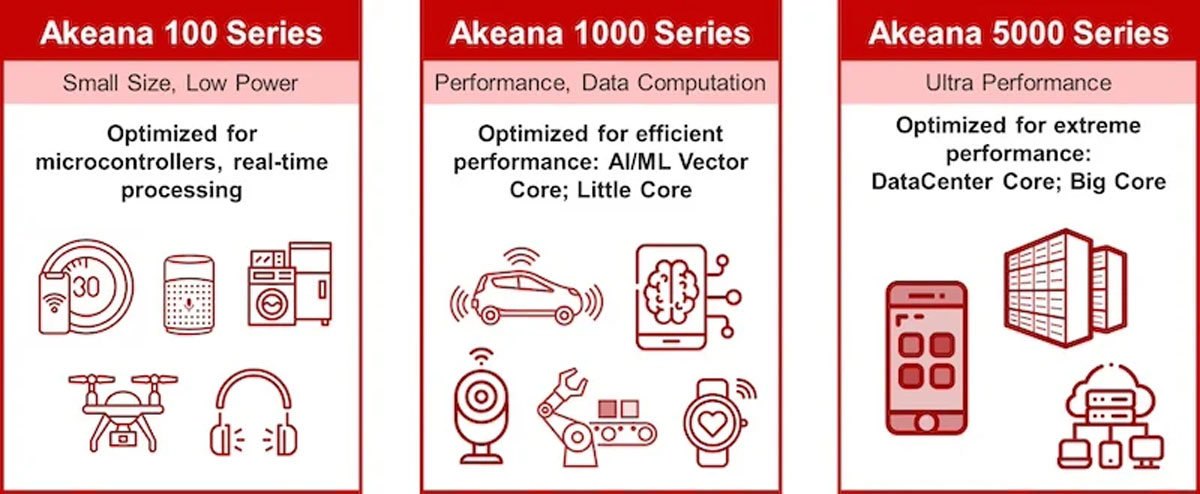

Portfolio chipów Akeana obejmuje trzy podstawowe serie, z których każda została zaprojektowana w celu zaspokojenia różnych potrzeb rynku, z naciskiem na wysoką wydajność i dostosowanie.

Rodziny produktów Akeana

Akeana 100

Seria Akeana 100 jest zbudowana wokół 32-bitowych rdzeni RISC-V i jest przeznaczona do zastosowań od wbudowanych mikrokontrolerów po osobiste urządzenia komputerowe. Procesory te działają z częstotliwością do 3 GHz i oferują szereg konfiguracji, od single- do dual-issue architektur in-order z cztero- do dziewięciostopniowymi potokami. Architektura ta obsługuje buforowanie L1 i L2, a także ICCM i DCCM, dzięki czemu pod względem wydajności jest odpowiednikiem serii M i R firmy ARM.

Akeana 1000

Seria Akeana 1000 obejmuje 64-bitowe rdzenie RISC-V wyposażone w jednostki MMU do obsługi rozbudowanych systemów operacyjnych przy zachowaniu niskiego zużycia energii i minimalnej powierzchni matrycy. Procesory te mogą być skalowane od jedno- do czterostopniowych architektur in-order, opcjonalnie rozszerzając się do 12-stopniowego potoku out-of-order. Obsługują rozszerzenia wektorowe do 512 bitów i wielowątkowość do czterech wątków, zapewniając wydajność w zakresie od 5 do 15 SPECint2006/GHz. Seria ta jest szczególnie odpowiednia dla elektroniki użytkowej, aplikacji motoryzacyjnych i brzegowych urządzeń IoT, pozycjonując się w stosunku do rdzeni ARM z serii A i Neoverse N1.

–Jesteśmy jedyną firmą RISC-V z tak wysoką wydajnością na poziomie IP, która może konkurować z Neoverse N i serią V – powiedział Bruno Putmanem, wiceprezes Akeana ds. sprzedaży i rozwoju biznesu.

Akeana 5000

Seria Akeana 5000 oferuje 64-bitowe rdzenie RISC-V zoptymalizowane pod kątem centrów danych i wysokowydajnych aplikacji mobilnych. Procesory te charakteryzują się architekturą o szerokości od sześciu do 10 out-of-order z 12-stopniowymi potokami, osiągając wskaźniki wydajności od 15 do 25 SPECint2006/GHz.

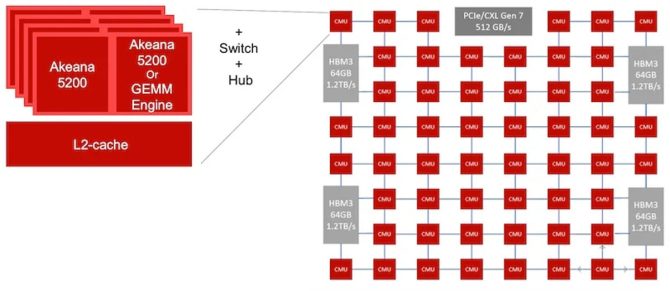

SoC Akeany o dużej liczbie rdzeni

Integrują one zaawansowane możliwości przetwarzania wektorowego i obsługę wielowątkowości, odzwierciedlając wydajność rdzeni ARM Neoverse N2, V1, V2 i Cortex serii X. Seria 5000 została zaprojektowana z myślą o maksymalnej wydajności jednowątkowej i solidnej skalowalności wielordzeniowej.

Akcelerator AI Matrix

Akeana oferuje również akcelerator AI Matrix, który ściśle integruje się z podsystemami pamięci procesora w celu optymalizacji przepływu danych i obliczeń. Akeana opracowała swoje chipy przy użyciu standardowego SystemVerilog, co pozwoliło znacznie rozszerzyć personalizację projektu i jego elastyczność. Rozwiązania te są również wspierane przez zintegrowane spójne połączenia międzysystemowe i skalowalne architektury siatkowe, które dodatkowo zwiększają ich wydajność i skalowalność.

– Nasz konfigurowalny projekt jest przełomem w branży” – powiedział Putman. „Pochodzi z jednej bazy danych. Wszystko jest w pełni napisane w standardowym języku SystemVerilog. To pozwala nam mieszać i dopasowywać funkcje. Jeśli opracujemy jakąś funkcję, możemy wciągnąć ją do dowolnej części naszej mapy drogowej.

Alternatywy RISC-V dla całej mapy drogowej Arm

Firma wykorzystuje RISC-V ISA, aby podkreślić elastyczność i dostosowanie swoich rozwiązań. Akeana jest aktywnie zaangażowana w społeczność RISC-V, zasiadając w zarządzie RISC-V i uczestnicząc w inicjatywach mających na celu rozwój ekosystemu ISA.

Firma wierzy, że ma to, czego potrzeba, aby konkurować z dużymi graczami, takimi jak ARM.

– W ciągu trzech lat i zatrudniając 150 osób, zespół ten był w stanie pokryć całą mapę drogową ARM – od low-endu aż po high-end – powiedział Putman.

Ostatecznie firma ma nadzieję, że jej połączenie doświadczenia, finansowania i obiecującej technologii może znaleźć szerokie zastosowanie w serwerach AI, odblokowując tym samym nowy poziom elastyczności i wydajności w centrum danych.

– Rynek jest na rozdrożu. AI to zupełnie nowy rynek i nie opiera się już na ustalonym ekosystemie Arm. Uważamy, że to ślepa plamka dla Arm i szansa dla nas.

Jake Hertz – All about circuits

Microchip prezentuje zestaw rozwojowy dla układu PolarFire SoC FPGA z rdzeniem RISC-V

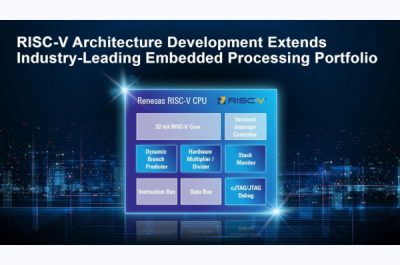

Microchip prezentuje zestaw rozwojowy dla układu PolarFire SoC FPGA z rdzeniem RISC-V  Renesas zaprojektował własny rdzeń oparty o zestaw instrukcji RISC-V

Renesas zaprojektował własny rdzeń oparty o zestaw instrukcji RISC-V  Ważni gracze na rynku elektroniki wspierają platformę RISC-V

Ważni gracze na rynku elektroniki wspierają platformę RISC-V