Zasady projektowania płytek drukowanych wykorzystujących interfejs DisplayPort

DisplayPort (DP) jest nowoczesnym interfejsem służącym do przesyłania sygnałów audio i video. Niniejsze opracowanie zawiera wytyczne dotyczące projektowania warstwy fizycznej tego standardu (ścieżek płytki drukowanej, przelotek oraz kondensatorów sprzęgających. Szczególną uwagę poświęcono minimalizacji strat i zakłóceń w celu utrzymania integralności sygnału. Opracowanie zawiera ponadto praktyczne wskazówki projektowania rozmieszczenia na płytce drukowanej referencyjnych układów scalonych firmy NXP: układów z rodziny DisplayPort level shifter PTN33xx oraz układów multiplekserów z rodziny DP/PCI Express (PCIe) CBTL061xx.

Połączenie interfejsu DisplayPort z płytką drukowaną

DisplayPort jest skalowalnym cyfrowym interfejsem graficznym, który jest dwukierunkowym szeregowym łączem par sygnałów różnicowych. Interfejs ten jest przeznaczony zarówno do wewnętrznych połączeń układów scalonych, jak i zewnętrznych cyfrowych urządzeń wyświetlających. Łącze główne składa się z jednego, dwóch lub czterech podwójnie zakończonych par różnicowych. Obsługiwane są dwie prędkości transmisji danych w jednym torze: 2,7 Gbit/s oraz 1,62 Gbit/s.

W rozwiązaniach projektowych sygnały przesyłowe złącza DisplayPort często współdzielą piny z sygnałami złącz DVI i HDMI. Te wielo-modalne sygnały interfejsu DisplayPort są czasami zwielokratniane (multipleksowane) sygnałami złącza PCI Express, który obsługuje prędkości transmisji danych 2,5 Gb/s i/lub 5 Gbit/s.

Wysoka szybkość transmisji danych dla złącz DP/PCIe wymaga spełnienia pewnych wymagań w odniesieniu do płytki drukowanej. Kluczowe wymagania to zminimalizowanie możliwości utraty połączenia oraz eliminacja zakłóceń.

Warstwy płytki drukowanej i płaszczyzny odniesienia

Interfejs DisplayPort nie wymaga nowych technologii płytek drukowanych. Ogólnie płytki drukowane do komputerów są projektowane z 4-warstw laminatu FR4, na przemian z warstwy prepreg 1080 i dieelektrycznej warstwy rdzeniowej 1,19 mm (0,047 cala), o całkowitej grubości znamionowej 1,5 mm (0,059 cala).

Przy projektowaniu należy zwrócić szczególną uwagę na uzyskanie odpowiedniej impedancji przy utrzymaniu małych tolerancji, tak by zminimalizować straty i zakłócenia sygnałów.

Dla par sygnałowych powinno unikać się nieciągłości w płaszczyźnie odniesienia, takich jak rozdzielenia (szczeliny) i otwory. Kiedy sygnał zmienia warstwy, przelotki do masy powinny być umieszczone blisko przelotek sygnałowych. Zaleca się minimum od 1 do 3 przelotek na parę sygnałową. Nigdy nie należy tak wyznaczać ścieżkę, aby musiała otaczać rozdzielenie płaszczyzny.

Ścieżki

Pierwszym istotnym parametrem ścieżek jest ich impedancja. Impedancja We/Wy układów PTN33xx i CBTL061xx powinna mieć wartości 50 Ω w konfiguracji asymetrycznej (jednokońcówkowej) oraz 100 Ω w konfiguracji symetrycznej (różnicowej). W celu zachowania integralności sygnału zaleca się, aby ścieżki płytki drukowanej złącza DP utrzymały impedancję w konfiguracji asymetrycznej 50 Ω ± 15% oraz w konfiguracji symterycznej 100 Ω ± 20%. Wymagana wartość impedancji została obniżona dla platformy Calpella, wprowadzonej w 2009, uwzględniając dokowanie oraz kartę dodatkową. Dla wszystkich sygnałów różnicowych, wymagana jest impedancja złącz DP, HDMI / DVI, i PCIe o wartości 85 Ω ± 15%. Istnieją dwa główne powody dla zalecenia nie-przekraczania 100 Ω. Jednym z nich są straty sygnałowe. Im większa impedancja, tym więcej strat. Długość ścieżki między układem scalonym a złączem nie może być większa niż 5 do 10 cm, w przeciwnym razie mogą powstawać znaczne straty. Innym powodem jest to, jak wykazuje symulacja, że przy połączeniu ścieżki obwodu drukowanego z szybkim złączem, zwłaszcza ze złączem PCIe, nieciągłości sygnału są duże, a pomiar reflekto-metryczny (TDR) pokazuje spadek do 70 Ω. Układy scalone są w dalszym ciągu projektowane dla impedancji 100 Ω, tak że występuje niedopasowanie pomiędzy układem scalonym a obwodem drukowanym. Jakkolwiek, symulacje wykazały, że ostatecznie lepiej mieć obwód drukowany zaprojektowany dla impedancji właściwej (fa-lowej) o wartości 85 Ω.

Kolejnym parametrem ścieżek jest ich szerokość i odstęp. Sprzężenie wewnętrznych różnicowych par sygnałowych oraz zwiększenie odstępów między sygnałami pomaga zminimalizować szkodliwe przesłuchy oraz zakłócenia elektromagnetyczne. W przypadku mikrolinii paskowej, ścieżka sygnału różnicowego powinna mieć szerokość 0,127 mm (5 milicali), przy odstępie szczeliny powietrznej między ścieżkami 0,178 mm (7 milicali) pary sygnałowej. Odstępy między parami sygnałowymi oraz sygnałami innymi niż sygnały DP/PCIe, powinny być równe co najmniej czterokrotnej grubości warstwy dieelektrycznej (rdzeniowej). Jeśli sygnały inne niż sygnały DP/PCIe mają znacznie wyższy poziom napięcia lub bardziej strome zbocza impulsu niż sygnały DP/PCIe, odległość powinna wzrosnąć do 0,762 mm (30 milicali) w celu uniknięcia sprzężenia.

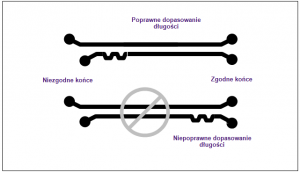

Następnym parametrem ścieżek jest ich długość. Długość ścieżki w znacznym stopniu wpływa na wielkość strat i zakłóceń połączeń. Ścieżka płytki drukowanej może wprowadzać wahania impulsów od 1 ps do 5 ps oraz tłumienność od 0,35 dB do 0,50 dB na długości 2,54 cm (1 cal). Długie ścieżki powinny być wyznaczone (trasowane) pod określonym kątem w układzie współrzędnych X-Y warstwy płytki drukowanej, tak by zneutralizować wpływ wiązek z włókien szklanych oraz bogatych w żywicę obszarów dielektryka. Dwie ścieżki pary sygnałowej powinny być trasowane symetrycznie (rysunek 1).

Rys. 1. Należy unikać niesymetrycznego trasowania

Różnica długości pomiędzy ścieżkami pary sygnałowej powinna być ograniczona maksymalnie do 0,127 mm (5 milicali). Dopasowanie długości jest wymagane w każdym segmencie i jakiekolwiek zwiększenie długości (zwykle fragment „serpentyny”) ze względu na dopasowanie pary, powinno być dodane w pobliżu miejsca, gdzie występuje niezgodność (rysunek 2).

Rys. 2. Dopasowanie długości ścieżek w miejscu występowania niezgodności.

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485