Zasady projektowania płytek drukowanych wykorzystujących interfejs DisplayPort

Przylutowanie środowych pól lutowniczych obudowy HWQFN/HVQFN do płytki drukowanej

Zarówno dla układu z rodziny PTN33xx DisplayPort level shifter, jak i układu z rodziny CBTL061xx DP/PCI Express (PCIe) multiplekser zastosowano obudowy HWQFN oraz HVQFN.

Środkowe pole kontaktowe obudowy HVQFN/HWQFN musi być przylutowane do odpowiadającego pola lutowniczego na płytce drukowanej dla zapewnienia masy elektrycznej oraz optymalnych warunków termicznych.

Podczas lutowania rozpływowego, pasta lutownicza topi się, a gaz lub uwięzione powietrze uwalnia się, powodując rozpryskiwanie lub zbrylanie lutu. Zbrylanie lutu lub jego rozpryski można zminimalizować, jeśli pasta lutownicza odpowiednio jest dozowana punktowo, zamiast jednego dużego nałożenia, oraz jeśli pasta jest utrzymywana w odpowiedniej odległości od krawędzi pola lutowniczego.

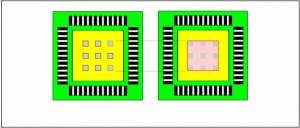

Wzorcowa powierzchnia pasty lutowniczej powinna obejmować 35% powierzchni pola lutowniczego. Podczas nakładania pasty lutowniczej na odsłonięte pole lutownicze płytki drukowanej, powierzchnia nałożenia pasty lutowniczej powinna pokrywać nie więcej niż 20% tej powierzchni do lutowania. Ponadto, pasta powinna być nakładana z dala od krawędzi pola lutowniczego. Zilustrowano to na rysunku 8 – wzorcowa powierzchnia nakładania pasty lutowniczej znajduje się w granicach wskazanych czerwoną linią i jest podzielona na całej powierzchni pola lutowniczego.

Rys. 8. Obszar punktów pasty lutowniczej (po lewej stronie) oraz wzorcowy obszar pasty (po prawej stronie).

Podsumowanie

Sygnały interfejsów DP/PCIe na płytce drukowanej są przesyłane z prędkością 1,6/2,7 Gbit/s lub 2,5/5 Gbit/s. Wysoka prędkość transmisji danych wymaga wdrożenia pewnych specyficznych rozwiązań w projekcie płytki drukowanej. Poniżej znajduje się podsumowanie wytycznych:

- Ścieżki par różnicowych muszą być prowadzone symetrycznie. Należy zapewnić jednakową długość wszystkich ścieżek sygnałów różnicowych. Różnica długości ścieżki powinna być mniejsza niż 0,127 mm (5 milicali).

- Należy utrzymać impedancję asymetryczną (jednokońcówkową) o wartości 50 Ω ± 15% oraz symetryczną (różnicową) o wartości 100 Ω ± 20%.

- Nie należy trasować ścieżek sygnałów o wysokiej prędkości transmisji, tak by otaczać jakiekolwiek rozdzielenie płaszczyzny. Należy używać tylko jednej płaszczyzny masy, znajdującą się pod płaszczyzną sygnałów różnicowych.

- Należy unikać jakichkolwiek nieciągłości w celu zapewnienia integralności sygnału. Pary różnicowe powinny być trasowane na tej samej warstwie. Liczba przelotek na ścieżkach sygnałów różnicowych powinna być zminimalizowana. Punkty pomiarowe powinny być rozmieszczone szeregowo i symetrycznie. Wyprowadzenia nie powinny być wprowadzone na pary ścieżek sygnałów różnicowych.

- Należy odpowiednio postępować ze środkowym polem lutowniczym obudowy HWQFN/HVQFN.

Opracowanie wykonane na podstawie noty aplikacyjnej NXP AN10798: DisplayPort PCB layout guidelines; Rev. 01, marzec 2009.

Bibliografia

[1]Eaglelake platform design guide — Wyd. popr. 1.1.1, wrzesień 2007; Intel Corp.[2]Calpella platform design guide — Wyd. popr. 0.8, sierpień 2008; Intel Corp.

[3]DisplayPort Standard — Version 1.1; VESA

[4]AN10373, “PCI Express PHY PCB Layout Guideline” — Rev. 01; 30 kwiecień 2005; NXP Semiconductors

[5]Board design guidelines for PCI Express architecture — 2004; PCI-SIG

[6]AN10366, “HVQFN application information” — Wyd. popr. 02; styczeń 2006; NXP Semiconductors

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485