Programowy UART w trybie full-duplex dla LPC111x oraz LPC13xx

Środowisko programistyczne

W omawianym przykładzie wykorzystano kilka wersji projektów oprogramowania. Zostały one przetestowane w środowiskach i na platformach sprzętowych wymienionych w tabeli 4. Pierwotne (tj. bez optymalizacji) rozmiary przykładowych projektów znajdują się w tabeli 5.

Tabela 4. Wersje używanych narzędzi

| Narzędzie | Numer wersji | LPC1114 PCB | LPC1343 PCB |

| LPCXpresso | v3.3.4 | LPCXpresso LPC1114 Rev. A, LPCXpresso Base Board Rev. A | LPCXpresso LPC1343 Rev A. LPCXpresso Base Board Rev. A |

| ompilator IAR C/C++ od ARM | 5.50.0.31878 | LPC1114-SK Rev. B | LPC1343-SK Rev. B |

| Kompilator Keil C/C++ | V4.0.0.728 | LPC1114-SK Rev. B | LPC1343-SK Rev. B |

Tabela 5. Szacowany rozmiar programu

| Narzędzie | Układ | Rozmiar pliku (bajty) |

| LPCXpresso | LPC1114 | 3632 |

| LPCXpresso | LPC1343 | 5236 |

| IAR | LPC1114 | 3636 |

| IAR | LPC1343 | 3710 |

| Keil | LPC1114 | 3796 |

| Keil | LPC1343 | 4216 |

Konfiguracja sprzętu – IAR LPC1114 SK

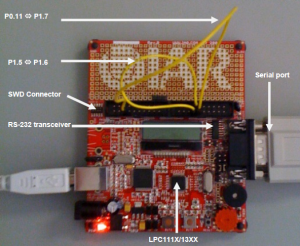

Przykładowe połączenie sprzętowe pokazano na rysunku 1. Warto zwrócić uwagę, iż zworki łączące porty P.0.11 oraz P1.7 ingerują w standardowe łącze 20-pinowe przeznaczone do debugowania. Nie wpływa to na proces debugowania poprzez wbudowany programator i debuger Jlink, jednak w przypadku wykorzystania zewnętrznych debugerów, takich jak Keil ULINK2, wymagane jest stosowanie 10-pinowego interfejsu SWD.

Rys. 1. Połączenie sprzętowe na płytce IAR LPC1114 SK

Konfiguracja sprzętu – LPC1114 LPCXpresso

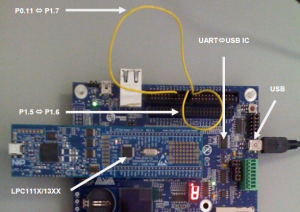

Na rysunku 2 zilustrowano sposób połączenia sygnałów UART do kontrolera USB na płytce LPC1114 LPCXpresso i na płytce bazowej.

Rys. 2. Połączenie sprzętowe na płytce LPC1114 LPCXpresso i na płytce bazowej

Praca systemu

Program demonstracyjny dla rodziny LPC13XX był testowany w następujących warunkach: w systemie z zewnętrznym oscylatorem krystalicznym o częstotliwości 12 MHz bez użycia pętli PLL, w systemach wykorzystujących PLL w celu generacji zegarów 24 MHz, 60 MHz i 72 MHz. Rodzina LPC111X została przetestowana w systemie z zewnętrznym oscylatorem 12 MHz, a także systemie z PLL generującym zegary 24 MHz i 48 MHz.

Warto zauważyć, że szybkość transferu układu UART zależna jest od częstotliwości zegara systemowego. Z tego powodu w systemach pracujących z zegarem innym, niż 48 MHz / 72 MHz użytych w przykładach, należy ustawić ręcznie wartość zmiennej BIT_LENGTH w kodzie źródłowym. Na przykład w systemie 12 MHz przesyłającym dane z prędkością 9600 bit/s, BIT_LENGTH będzie równe 12000000/9600 = 1250. Jeśli zegar systemowy zostanie przestawiony na 48 MHz, BIT_LENGTH należy zmienić na 48000000/9600 = 5000.

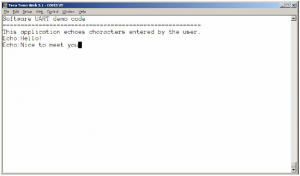

Aplikacja demonstracyjna wyświetli wiadomość dla użytkownika, a następnie wejdzie do nieskończonej pętli, w której otrzymywane znaki będą przekazywane z powrotem do użytkownika. Pokazuje to rysunek 3.

Rys. 3. Przykładowa odpowiedź programu

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485