Wykorzystywanie trybów pracy o obniżonym poborze energii w mikrokontrolerach NXP LPC1700

Niniejszy artykuł ma na celu przedstawienie różnych trybów pracy o obniżonym poborze energii dostępnych w mikrokontrolerach serii LPC1700, sposobu wchodzenia w te tryby oraz użytecznych wskazówek pozwalających na bardziej energooszczędną pracę układów. W tekście został przedstawiony również przykładowy program demonstrujący wchodzenie w tryby pracy o obniżonym poborze energii oraz metody pomiaru jej zużycia w zestawie ewaluacyjnym Keil MCB1700.

Rodzina LPC1700

Mikrokontrolery rodziny LPC1700 są zbudowane w oparciu o rdzeń ARM Cortex-M3, przeznaczony do zastosowań w systemach wbudowanych, cechujący się wysokim stopniem integracji zasobów wewnętrznych i niskim zużyciem energii. Mikrokontrolery LPC1700 są wyposażone w kluczowe funkcje i moduły, takie jak: magistrala AHB łącząca zasoby wewnętrzne, kontroler przerwań NVIC zintegrowany z licznikiem systemowym SYSTICK, kontroler przerwań wybudzających (Wakeup Interrupt Controller), jednostka ochrony pamięci, cztery tryby pracy o obniżonym poborze energii oraz szeroka gama peryferiów, co czyni je najbardziej zaawansowanymi mikrokontrolerami z rdzeniem Cortex-M3 na rynku.

Wśród zasobów będących na wyposażeniu mikrokontrolerów LPC1700 można znaleźć: do 512 kB pamięci Flash, do 64 kB pamięci danych, kontroler Ethernet z adresem MAC, interfejs USB z możliwością pracy jako host lub urządzenie, 8-kanałowy kontroler DMA ogólnego przeznaczenia, interfejsy komunikacyjne (4 x UART, 2 x CAN, 2 x SSP, SPI, 3 x I2C), 8-kanałowy, 12-bitowy przetwornik A/C, 10-bitowy przetwornik C/A, generator PWM do sterowania silnikami, zegar RTC o ultra-niskim poborze energii z osobnym zasilaniem bateryjnym oraz do 70 wyprowadzeń I/O ogólnego przeznaczenia.

Układy rodziny LPC1700 mogą znaleźć zastosowanie w wielu aplikacjach, m.in. w: systemach zdalnego pomiaru energii (e-metering), systemach oświetleniowych, sieciach przemysłowych, systemach alarmowych, sprzęcie AGD czy przy sterowaniu silnikami.

Struktura systemu zasilania i zarządzenie nim

W niniejszym rozdziale omówione zostały dwa zagadnienia: domeny zasilania oraz tryby pracy o obniżonym poborze energii.

Domeny zasilania

W mikrokontrolerach LPC1700 można wyróżnić 5 domen zasilania:

- VDD(Reg)(3V3) – wbudowany w mikrokontroler stabilizator napięcia (zasilanie od 2.4 do 3.6 V),

- VDD(3V3) – zasilanie portów I/O (zasilanie od 2.4 do 3.6 V),

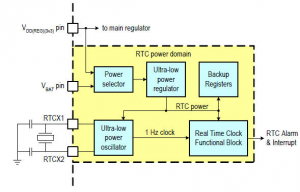

- VBAT (zasilanie od 2.1 do 3.6 V) – zasilanie tylko zegara czasu rzeczywistego (RTC) i rejestrów zapasowych (Backup Registers),

- VDDA (od 2.7 do 3.6 V) – analogowe źródło zasilania dla 12-bitowych przetworników A/C,

- VREFP (od 2.7 do 3.6 V) – analogowe napięcie odniesienia dla przetworników A/C.

W mikrokontrolerach LPC1700 zaimplementowano osobną domenę zasilania VBAT, aby umożliwić wyłączenie zasilania układu z jednoczesnym podtrzymaniem pracy zegara czasu rzeczywistego. Wyprowadzenie VBAT dostarcza zasilanie tylko dla domeny RTC. Gdy rdzeń mikrokontrolera jest zasilany, RTC współdzieli z nim źródło zasilania, co zapobiega rozładowywaniu baterii, gdy nie jest ona bezwzględnie konieczna.

Rys. 1. Domena zasilania RTC w mikrokontrolerach LPC1700

Tryby zasilania

Mikrokontrolery rodziny LPC1700 są wyposażone w cztery tryby pracy o obniżonym poborze energii: tryb uśpienia (Sleep mode), tryb głębokiego uśpienia (Deep-sleep mode), tryb wyłączenia (Power-down mode) oraz tryb zupełnego wyłączenia (Deep Power-down mode). Poniżej omówione zostały wszystkie wymienione tryby.

Tryb uśpienia (Sleep mode)

W trybie tym wykonywanie instrukcji jest zawieszone (zegar taktujący rdzeń jest zatrzymany) aż do wystąpienia przerwania lub Resetu. Działanie peryferiów są podtrzymane i peryferia mogą wystawiać przerwania powodujące wznowienie wykonywania instrukcji. Kontroler DMA ogólnego przeznaczenia (GPDMA) w tym trybie może pracować, uzyskując dostęp do pamięci SRAM podłączonej do magistrali AHB oraz peryferiów mogących współpracować z GPDMA. Nie jest jednak możliwe uzyskanie dostępu do pamięci Flash oraz głównej pamięci SRAM, które są wyłączone w celu oszczędzania energii. Tryb uśpienia eliminuje pobór mocy wynikający z pracy procesora, systemów pamięci i powiązanych z nimi kontrolerów oraz magistral wewnętrznych.

Wybudzenie z trybu uśpienia następuje przy pojawieniu się któregoś z obsługiwanych przerwań.

Tryb głębokiego uśpienia (Deep-sleep mode)

Gdy układ wchodzi w tryb głębokiego uśpienia, odłączane jest zasilanie głównego oscylatora i wyłączane są prawie wszystkie zegary. Nie jest przerywana praca wewnętrznego oscylatora RC (Internal RC Oscilator, IRC), który można skonfigurować do współpracy z timerem układu watchdoga, pozwalając na wybudzanie jednostki centralnej przez watchdog. Nie jest też zatrzymywany, pracujący z częstotliwością 32 kHz, oscylator zegara czasu rzeczywistego, a przerwania od RTC także można wykorzystywać do wybudzania procesora. Pamięć Flash jest w trybie wstrzymania (standby), pozwalającym na szybki powrót do pracy. Pętle PLL są automatycznie wyłączane i odłączane. Stan procesora oraz zawartość jego rejestrów, podobnie jak zawartość rejestrów peryferiów oraz dane z wewnętrznej pamięci SRAM są zachowywane, a poziomy logiczne wyprowadzeń pozostają bez zmiany. Z trybu głębokiego uśpienia można układ wybudzić poprzez Reset lub wybrane specyficzne przerwania, które mogą zostać wystawione bez zegarów. Jako że wszelkie dynamiczne operacje są w tym trybie zawieszone, zużycie energii jest zredukowane do bardzo niskiego poziomu.

Jeżeli przed wejściem w tryb głębokiego uśpienia używany był wewnętrzny oscylator RC, przy wychodzeniu z tego trybu odliczanie zaczyna dwubitowy timer tego oscylatora, a wykonywanie instrukcji rozpoczyna się na powrót po zakończeniu odliczania (czyli po 4 cyklach). Jeśli używany był natomiast główny oscylator zewnętrzny, odliczanie zaczyna 12-bitowy timer głównego oscylatora i wykonywanie kodu zaczyna się po 4096 cyklach. Użytkownik po wybudzeniu procesora musi pamiętać o rekonfiguracji pętli PLL i dzielników zegara, których zamierza używać.

Wybudzenie z trybu głębokiego uśpienia można uzyskać poprzez przerwanie niemaskowane (NMI), jedno z przerwań zewnętrznych (External Interrupts) od EINT0 do EINT3, przerwanie GPIO, przerwanie typu Wake-on-LAN kontrolera Ethernet, wykrycie spadku napięcia (Brownout Detect), przerwanie alarmu RTC, zakończenie zliczania timera watchdoga, albo zmianę stanu wyprowadzeń wejściowych USB (USB Activity interrupt) lub CAN (CAN Activity interrupt), wygenerowaną wskutek aktywności na magistrali CAN. Wybudzenie przez timer watchdoga może nastąpić, jeśli timer ten jest taktowany przez wewnętrzny oscylator RC.

Tryb wyłączenia (Power-down mode)

W trybie wyłączenia stosowane są wszystkie mechanizmy oszczędzania energii wykorzystywane w trybie głębokiego uśpienia, a dodatkowo wyłączana jest pamięć Flash. Pozwala to na większe oszczędności, ale kosztem wydłużonego czasu dostępu do pamięci Flash. Do czasu dostępu do kodu lub danych zapisanych w tej pamięci jest bowiem dodawany czas konieczny na wznowienie pracy pamięci. Gdy układ wchodzi w tryb wyłączenia, zatrzymywane są: główny oscylator, wewnętrzny oscylator RC (IRC) i wszystkie zegary. Zegar czasu rzeczywistego nie przerywa pracy, o ile był uruchomiony, a przerwania od niego można wykorzystać do wybudzania CPU. Pamięć Flash jest wyłączana bezwarunkowo. Pętle PLL są automatycznie wyłączane i odłączane. Dzielniki zegarów CCLK i USBCLK zostają wyzerowane. Jeśli przed wejściem w tryb Power-down używany był IRC, to przy wybudzeniu z tego trybu, po upłynięciu czasu koniecznego na jego włączenie (około 60 µs), odliczać zaczyna dwubitowy timer IRC. Jego praca kończy się po zliczeniu 4 cykli, po czym – o ile przed wejściem w tryb wyłączenia wykonywany był kod z pamięci SRAM – następuje bezzwłocznie dalsze wykonywanie kodu. W międzyczasie, timer startowy pamięci Flash odlicza czas około 100 µs. Gdy kończy zliczanie, możliwy jest dostęp do pamięci Flash. Użytkownik musi pamiętać o rekonfiguracji pętli PLL i dzielników zegara, których zamierza używać po wybudzeniu.

Podobnie jak dla trybu Deep-sleep, wybudzenie z trybu Power-down można uzyskać poprzez przerwanie niemaskowane (NMI), jedno z przerwań zewnętrznych (External Interrupts) od EINT0 do EINT3, przerwanie GPIO, przerwanie typu Wake-on-LAN kontrolera Ethernet, wykrycie spadku napięcia (Brownout Detect), przerwanie alarmu RTC, zakończenie zliczania timera watchdoga oraz zmianę stanu wyprowadzeń wejściowych USB (USB Activity interrupt) lub CAN (CAN Activity interrupt), wygenerowaną wskutek aktywności na magistrali CAN.

Tryb zupełnego wyłączenia (Deep Power-down mode)

W trybie zupełnego wyłączenia zasilanie jest odłączone od całego układu, z wyjątkiem: zegara czasu rzeczywistego, nóżki RESET, kontrolera przerwań WIC (Wakeup Interrupt Controller) oraz rejestrów zapasowych RTC. Aby zoptymalizować zużycie energii, użytkownik może opcjonalnie wyłączyć oraz z powrotem włączyć zasilanie oscylatora 32 kHz. Możliwe jest też wykorzystanie zewnętrznych układów do odłączenia zasilania wewnętrznego stabilizatora napięcia poprzez nóżki VDD(REG)(3V3). Zasilanie wewnętrznego stabilizatora musi jednak być przywrócone przed powrotem do normalnej pracy.

Wybudzenie ztego trybu pracy można uzyskać za pomocą zewnętrznego sygnału resetu lub przerwania RTC, o ile przerwania te są włączone.

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485